Release Date: January, 1999

Order Number: 272865-004

The 8XC196NT may contain design defects or errors known as errata that may cause the processor's behavior to deviate from published specifications. Current characterized errata are documented in this specification update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 8XC196NT microcontroller may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1/11/99

\*Third-party brands and names are the property of their respective owners.

# **CONTENTS**

| CONTENTS                     | iii |

|------------------------------|-----|

| REVISION HISTORY             | 1   |

| PREFACE                      | 2   |

| SUMMARY TABLE OF CHANGES     | 4   |

| IDENTIFICATION INFORMATION   | 6   |

| ERRATA                       | 7   |

| SPECIFICATION CHANGES        | 11  |

| SPECIFICATION CLARIFICATIONS | 11  |

| DOCUMENTATION CHANGES        | 12  |

# **REVISION HISTORY**

| Rev. Date | Version | Description                                                                                                    |

|-----------|---------|----------------------------------------------------------------------------------------------------------------|

| 07/96     | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date. |

| 09/96     | 002     | Added documentation change number 001 (ICC, IIDLE versus Frequency).                                           |

| 01/97     | 003     | Added specification change number 001 (Iol/Ioh values for ports 1–6).                                          |

| 01/99     | 004     | Added errata # 9900007.                                                                                        |

#### PREFACE

As of July, 1996, Intel has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### Affected Documents/Related Documents

| Title                                    | Order  |

|------------------------------------------|--------|

| 8XC196NT CHMOS Microcontroller datasheet | 272267 |

| 8XC196NT Microcontroller User's Manual   | 272317 |

#### Nomenclature

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

# الهint

#### **8XC196NT SPECIFICATION UPDATE**

#### NOTE:

Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

#### SUMMARY TABLE OF CHANGES

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the 8XC196NT product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

# Codes Used in Summary Table

# Stepping

X: Errata exists in the stepping indicated. Specification Change

or Clarification that applies to this stepping.

(No mark)

or (Blank box): This erratum is fixed in listed stepping or specification change

does not apply to listed stepping.

Page

(Page): Page location of item in this document.

Status

Doc: Document change or update will be implemented.

Fix: This erratum is intended to be fixed in a future step of the com-

ponent.

Fixed: This erratum has been previously fixed. NoFix: There are no plans to fix this erratum.

Eval: Plans to fix this erratum are under evaluation.

Row

Change bar to left of table row indicates this erratum is either

new or modified from the previous version of the document.

# Errata

| Number  | Steppings |                   | Page S | Status | ERRATA                                                                        |                                          |

|---------|-----------|-------------------|--------|--------|-------------------------------------------------------------------------------|------------------------------------------|

| Number  | D         | # # # Fage Status |        | Status |                                                                               |                                          |

| 9600001 | Χ         |                   |        | 7      | 7 Fix Illegal Opcode Interrupt Vector in 1-Mb                                 |                                          |

| 9600002 | Χ         |                   |        | 7      | 7 Fix Aborted Interrupt Vectors to Lowest Priority in 1-Mbyte Mode            |                                          |

| 9600003 | Χ         |                   |        | 8      | 8 Fix PTS Request During Interrupt Latency 1-Mbyte Mode                       |                                          |

| 9600004 | Χ         |                   |        | 9      | Fix Modes 1 and 2 Need a Latch on Upper Address Lines                         |                                          |

| 9600005 | Χ         |                   |        | 9      | Fix Jump Instruction at 64K Page Boundary                                     |                                          |

| 9600006 | Х         |                   |        | 9      | 9 Fix External Memory Accesses After Idle Mode Exit in Bus-timing Modes 1 and |                                          |

| 9900007 | Χ         |                   |        | 10     | NoFix                                                                         | A/D Conversion Error on First Conversion |

# Specification Changes

| Number | St | eppin | gs | Page | Status                              | SPECIFICATION CHANGES |

|--------|----|-------|----|------|-------------------------------------|-----------------------|

| Number | #  | #     | #  | raye | Status                              | SPECIFICATION CHANGES |

| 001    |    |       |    | 11   | Doc   lol/loh values for ports 1–6. |                       |

# Specification Clarifications

| Number | St | eppin | gs | Page | Status | SPECIFICATION CLARIFICATIONS                        |  |

|--------|----|-------|----|------|--------|-----------------------------------------------------|--|

| Number | #  | #     | #  | raye | Status | SPECIFICATION CEARIFICATIONS                        |  |

|        |    |       |    |      |        | None for this revision of this specification update |  |

272865-004 January, 1999 5 of 12

# **Documentation Changes**

| Number | Document<br>Revision | Page | Status | DOCUMENTATION CHANGES                                                                                              |

|--------|----------------------|------|--------|--------------------------------------------------------------------------------------------------------------------|

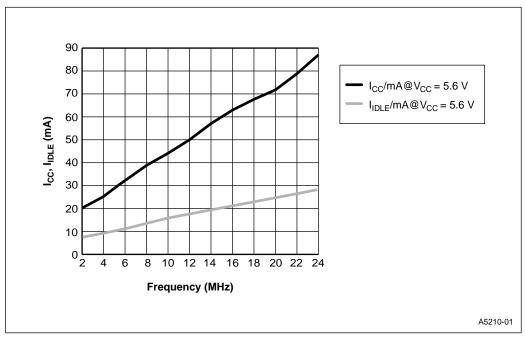

| 001    | -002                 | 12   | Doc    | Added I <sub>CC</sub> , I <sub>IDLE</sub> versus Frequency graph; will be added to revision -005 of the datasheet. |

# **IDENTIFICATION INFORMATION**

# Markings

Bottom mark: N87C196NT (OTPROM) or N80C196NT (no nonvolatile memory)

Stepping indicator: D-step components are identified by a "D" at the end of the topside tracking number.

#### FRRATA

# 9600001. Illegal Opcode Interrupt Vector in 1-Mbyte Mode

**PROBLEM:** The illegal opcode interrupt should be generated when there is an attempt to execute an undefined opcode, and should vector to address FF2012H to handle the interrupt. But in 1-Mbyte mode only, the vector address for the illegal opcode interrupt is not generated correctly and a random vector address is generated.

**IMPLICATION:** Code that executes an illegal opcode (10h or E5h) will vector to a random address.

**WORKAROUND:** Use a C-compiler or assembler that will flag the Illegal opcode, or put a reset opcode (FFh) at the end of any data tables or unused memory locations.

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

## 9600002. Aborted Interrupt Vectors to Lowest Priority in 1-Mbyte Mode

**PROBLEM:** In 1-Mbyte mode only, an aborted interrupt (either intentional or unintentional) may cause an undesired branch to the lowest-priority interrupt vector (FF2000H) even if the lowest-priority interrupt is masked. This may occur if any bit in the INT\_MASK, INT\_MASK1, INT\_PEND, or INT\_PEND1 register is cleared after the corresponding INT\_PEND or INT\_PEND1 bit is set.

**Example:** If the EXTINTO interrupt on the 8XC196NT is enabled by setting INT\_MASK.3, and a rising edge on EXTINTO occurs, INT\_PEND.3 is then set. The following instruction may cause the CPU to vector to FF2000H instead of FF2006H.

```

ANDB INT_MASK,#0F7H ;masks EXTINT0 ;may cause vector to FF2000H

```

**IMPLICATION:** This may occur if any bit in the INT\_MASK, INT\_MASK1, INT\_PEND, or INT\_PEND1 register is cleared after the corresponding INT\_PEND or INT\_PEND1 bit is set. An undesired branch to the lowest-priority interrupt may occur if an interrupt is aborted, unless the workaround is used.

**WORKAROUND:** Use a disable interrupt (DI) instruction before clearing a bit in INT\_MASK, INT\_MASK1, INT\_PEND, or INT\_PEND1. The following code example demonstrates how to safely disable the EXTINTO interrupt.

| DI   |           |       | ;disable | interrupts |

|------|-----------|-------|----------|------------|

| ANDB | INT_MASK, | #0F7H | ;mask EX | TINTO      |

| EI   |           |       | ;enable  | interrupts |

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

# 9600003. PTS Request During Interrupt Latency in 1-Mbyte Mode

**PROBLEM:** This erratum occurs only in 1-Mbyte mode. If a standard interrupt occurs at approximately the same time (this time is code dependent and therefore cannot be stated as an exact number of state times) as a PTS serviced interrupt, the PTS interrupt may be processed as a standard interrupt. The standard interrupt service routine for a PTS-serviced interrupt (usually referred to as the End-of-PTS) is typically used to modify the PTS control block and re-enable the PTS by setting the corresponding bit in the PTSSEL register. When this anomaly occurs, the End-of-PTS service routine will execute regardless of the value in PTSCOUNT. As a result, an indeterminate number of PTS cycles will fail to occur. This applies to all interrupts serviced by the PTS.

**IMPLICATION:** Customers using both PTS and standard interrupts. If the workaround described below is not used, an indeterminate number of PTS cycles may be missed.

**WORKAROUND:** In the standard interrupt service routine (End-of-PTS) for each PTS enabled, the first instruction following a PUSHF or PUSHA should determine whether the associated bit in the PTSSEL register is set or cleared. Checking this bit will determine whether the desired number of cycles were completed or a premature End-of-PTS occurred. If the bit is set, the associated pending bit in the INT\_PEND or INT\_PEND1 should be set and a RET instruction executed. This will cause a PTS cycle to occur. If the associated bit in the PTSSEL register is cleared, the normal End-of-PTS procedure should be executed. The following is an example of an End-of-PTS service routine for the external interrupt 0 (EXTINTO).

```

CSEG AT 0FF2006H

DCW EXTINT0_END_OF_PTS

CSEG AT 0FF3000H

EXTINT0_END_OF_PTS:

PUSHA

JBC PTSSEL,3,OKAY

ORB INT_PEND,#08H

POPA

RET

OKAY:

;

; reload PTSCOUNT

; re-enable PTSSEL

;

POPA

RET

```

# intها

#### **8XC196NT SPECIFICATION UPDATE**

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

## 9600004. Modes 1 and 2 Need a Latch on Upper Address Lines

**PROBLEM:** In all bus timing modes, for 16-bit bus-width operation, latch the upper and lower address/data lines. In modes 1 and 2, for 8-bit bus-width operation, also latch the upper and lower address/data lines; the upper address lines are not driven throughout the entire bus cycle. In modes 0 and 3, for 8-bit bus-width operation, latch only the lower address/data lines. In these modes, it is not necessary to latch the upper address lines because these lines are driven throughout the entire bus cycle.

**IMPLICATION:** If the latch is not used, the 8XC196NT could read from and write to undesired memory locations.

**WORKAROUND:** Add a latch to the upper address lines.

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

# 9600005. Jump Instruction at 64K Page Boundary

**PROBLEM:** Any jump, conditional jump, or call instruction located within six bytes of the top of any 64K page boundary, (e.g., 01FFFAH-01FFFFH) may cause a jump to the wrong page.

**IMPLICATION:** A jump to the wrong page could cause the device to reset due to an undesired code fetch.

**WORKAROUND:** To ensure that this problem does not occur, place at least six NOPs at the top of each page.

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

# 9600006. External Memory Accesses After Idle Mode Exit in Bus-timing Modes 1 and 2

**PROBLEM:** When operating in bus-timing modes 1 and 2, the 8XC196NT cannot access external memory immediately after exiting idle mode. Accesses to internal memory are unaffected.

**IMPLICATION:** Applications using external memory with bus-timing mode 1 or 2 and idle mode will be affected. Attempts to access external memory immediately upon exiting idle

mode will result in corrupted data. If the access is a code fetch, the results are unpredictable.

**WORKAROUND:** For 80C196NT microcontrollers, which have no internal nonvolatile memory, do not use idle mode with bus-timing mode 1 or 2.

For 87C196NT microcontrollers, which have internal OTPROM, you can use idle mode with bus-timing mode 1 or 2 if you ensure that all interrupt vectors, interrupt service routines, and the stack are located in internal memory. (Interrupt vectors must reside in OTPROM; interrupt service routines must reside in either OTPROM or code RAM; and the stack must be located in either code RAM or register RAM.) Ensure that software does not access external memory until at least 10ms after the microcontroller exits idle mode.

**STATUS:** Fix. This erratum is intended to be fixed in a future stepping of the component. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9900007. A/D Conversion Error on First Conversion

**PROBLEM:** The first A/D conversion performed after a reset of the device may produce a result that is less accurate than the accuracy specification in the datasheet. The amount of error is dependant on several environmental conditions including process variation, light exposure, temperature, and  $V_{CC}/V_{RFF}$  differential.

**IMPLICATION:** If the application is sensitive to A/D accuracy, an error in the application may occur as a result of the first conversion error.

**WORKAROUND:** Do not compare for the A/D result on the first conversion. All subsequent conversions should produce accurate results.

**STATUS:** NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).

# **SPECIFICATION CHANGES**

# 001. Iol/loh values for ports 1–6.

ITEM: Include the IoI/Ioh values in the DC Characteristic section of the datasheet.

Test condition: Voh = Vcc-0.7V, Vol = 0.45V

- Port 1 Max Iol = 6.5mA, Max Ioh = 7.5mA

- Port 2 Max Iol = 8.0mA, Max Ioh = 12.0mA

- Port 3 Max Iol = 7.5mA, Max Ioh = 7.5mA

- Port 4 Max Iol = 7.5mA, Max Ioh = 7.5mA

- Port 5 Max Iol = 9.0mA, Max Ioh = 9.0mA

- Port 6 Max Iol = 8.0mA, Max Ioh = 9.0mA

Test condition: Voh = Vcc-1.5V, Vol = 1.5V

- Port 1 Max Iol = 21.0mA, Max Ioh = 26.0mA

- Port 2 Max Iol = 26.0mA, Max Ioh = 29.0mA

- Port 3 Max Iol = 17.0mA, Max Ioh = 25.0mA

- Port 4 Max Iol = 16.0mA, Max Ioh = 25.0mA

- Port 5 Max lol = 21.0mA, Max loh = 28.0mA

- Port 6 Max lol = 19.0mA, Max loh = 26.0mA

# SPECIFICATION CLARIFICATIONS

None for this revision of this specification update.

# **DOCUMENTATION CHANGES**

# 001. Added ICC, IIDLE versus Frequency graph; will be added to revision -005 of the datasheet.

**ITEM:** The following graphic illustrating ICC and IIDLE versus Frequency will be added to the next revision (-005) of the *8XC196NT CHMOS Microcontroller* datasheet.

Figure 1. I<sub>CC</sub>, I<sub>IDLE</sub> versus Frequency