## 80960Cx Processor

**Specification Update**

October 1998

**Notice:** The 80960Cx processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this specification update.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

| Revision History             | 5  |

|------------------------------|----|

| Preface                      | 6  |

| Summary Table of Changes     | 7  |

| Identification Information   | 11 |

| Errata                       | 12 |

| Specification Changes        | 28 |

| Specification Clarifications | 29 |

| Documentation Changes        | 30 |

## int<sub>el</sub> *Revision History*

| Date of Revision | Version | Description                                                                                                    |

|------------------|---------|----------------------------------------------------------------------------------------------------------------|

| 10/05/98         | 004     | Corrected erroneous Status marking (e.g., Fix, NoFix) for errata items #17, #18, #28, #36, #40, #42            |

| 04/10/98         | 003     | Added Errata #45.                                                                                              |

| 06/30/97         | 002     | Added Errata #44.                                                                                              |

| 07/01/96         | 001     | This is the new Specification Update document. It contains all identified errata published prior to this date. |

## **Preface**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

### **Affected Documents/Related Documents**

| Title                                                                                              | Order # |

|----------------------------------------------------------------------------------------------------|---------|

| 80960CA 32-Bit High-Performance Embedded Processor datasheet                                       | 270727  |

| 80960CF-40, -33, -25, -16 32-Bit High-Performance Superscalar Embedded<br>Microprocessor datasheet | 272886  |

| i960 <sup>®</sup> Cx Microprocessor User's Manual                                                  | 270710  |

| i960 <sup>®</sup> Cx Microprocessor User's Manual - Instruction Set Quick Reference                | 272220  |

#### Nomenclature

**Errata** are design defects or errors. These may cause the 80960CA/CF's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

## Summary Table of Changes

The following table indicates the errata, specification changes, specification clarifications, or documentation changes which apply to the 80960CA/CF product. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. This table uses the following notations:

### **Codes Used in Summary Table**

#### Stepping

| X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|-----------------|---------------------------------------------------------------------------------------------------------------|

| (No mark)       |                                                                                                               |

| or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| (Page):         | Page location of item in this document.                                                                       |

| Doc:            | Document change or update will be implemented.                                                                |

| Fix:            | This erratum is intended to be fixed in a future step of the component.                                       |

| Fixed:          | This erratum has been previously fixed.                                                                       |

| NoFix:          | There are no plans to fix this erratum.                                                                       |

| Eval:           | Plans to fix this erratum are under evaluation.                                                               |

#### Row

Page

**Status**

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### Errata (Sheet 1 of 3)

|            |             |         | S          | itepp | ings |    |    |        |        |                                                                                                                                  |

|------------|-------------|---------|------------|-------|------|----|----|--------|--------|----------------------------------------------------------------------------------------------------------------------------------|

| New<br>No. | Prev<br>No. | 80960CA |            | 80    | 0960 | CF | Pg | Status | ERRATA |                                                                                                                                  |

|            |             | C2      | <b>C</b> 3 | D     | в    | С  | Е  |        |        |                                                                                                                                  |

| 1          | A2          | Х       | Х          |       |      |    |    | 12     | Fixed  | A2 Bus Backoff and READY#                                                                                                        |

| 2          | A5A         | х       | х          |       |      |    |    | 12     | Fixed  | A5A DACK Timing Vs Ready Wait States                                                                                             |

| 3          | A5B         | х       | х          |       |      |    |    | 12     | Fixed  | A5B DACK Timing with Multiple<br>Accesses Per Bus Request                                                                        |

| 4          | A18         | х       | х          |       |      |    |    | 12     | Fixed  | A18 DMA SSDEM Mode Packing and EOP                                                                                               |

| 5          | A19         | х       | х          |       |      |    |    | 13     | Fixed  | A19 Suspend DMA, EOP and SDMA                                                                                                    |

| 6          | A20A        | х       | х          |       |      |    |    | 13     | Fixed  | A20 A EOP, SDMA and Multi-<br>Channel DMA Operations                                                                             |

| 7          | A20B        | х       | х          |       |      |    |    | 14     | Fixed  | A20 B EOP, SDMA and Multi-<br>Channel DMA Operations                                                                             |

| 8          | A21         | х       | х          |       |      |    |    | 14     | Fixed  | A21 Disabling Branch Lookahead<br>Causes DMA problems                                                                            |

| 9          | A22         | х       | х          |       |      |    |    | 14     | Fixed  | A22 NMI is Level-Triggered after RESET                                                                                           |

| 10         | A25         | x       | х          |       | х    |    |    | 14     | Fixed  | A25 Interrupts During SYSCTL<br>Instruction to Load and Lock the<br>Instruction Cache                                            |

| 11         | A26         | x       | х          |       | x    |    |    | 15     | Fixed  | A26 32-32 Bit Transfers in Source-<br>Synchronized Demand Mode with<br>Unaligned Destination Address                             |

| 12         | A27         |         |            |       | x    |    |    | 15     | Fixed  | A27 Terminal Count (TC) pins are<br>non-functional when using any<br>channel in source synchronized<br>demand mode or block mode |

| 13         | A28         | х       | х          |       | х    |    |    | 15     | Fixed  | A28 DMA and Instruction<br>Scheduler Interaction                                                                                 |

| 14         | A29         | х       | х          |       | х    |    |    | 17     | Fixed  | A29 Destination Synchronized 128-<br>to 128-Bit Quad-Word Transfer Mode                                                          |

| 15         | A30         |         |            |       | х    |    |    | 17     | Fixed  | A30 Disabling the Instruction<br>Cache                                                                                           |

| 16         | A31         |         |            |       | x    |    |    | 18     | Fixed  | A31 Interrupt Can Cause User<br>Process Stall when DMA Active<br>Under Certain Complex Conditions                                |

| 17         | A32         |         |            | Х     |      |    |    | 18     | NoFix  | A32 Register Cache                                                                                                               |

| 18         | B1          | х       | х          |       |      |    |    | 18     | Fixed  | B1 Cache Functionality/Re-<br>fetching Cached Instructions                                                                       |

| 19         | B3          | Х       | Х          |       |      |    |    | 19     | Fixed  | B3 COBR Branch Trace                                                                                                             |

| 20         | B5          | Х       | Х          |       |      |    |    | 19     | Fixed  | B5 EOP and DREQ Deassertion                                                                                                      |

| 21         | B6          | Х       | Х          |       |      |    |    | 19     | Fixed  | B6 DREQ Sampling                                                                                                                 |

### Errata (Sheet 2 of 3)

|            |             |         | S  | tepp | ings  |    |    |        |        |                                                                                                    |

|------------|-------------|---------|----|------|-------|----|----|--------|--------|----------------------------------------------------------------------------------------------------|

| New<br>No. | Prev<br>No. | 80960CA |    | 8    | 09600 | CF | Pg | Status | ERRATA |                                                                                                    |

|            |             | C2      | C3 | D    | в     | С  | Е  |        |        |                                                                                                    |

| 22         | B8          | х       | х  |      |       |    |    | 19     | Fixed  | B8 SYSCTL followed by RET May<br>Incorrectly Fault                                                 |

| 23         | B10         | Х       | Х  |      |       |    |    | 20     | Fixed  | B10 Terminal Count Operation                                                                       |

| 24         | B11A        | Х       | х  |      |       |    |    | 20     | Fixed  | B11A Testif and Faultif Cause<br>Incorrect Branch Trace                                            |

| 25         | B11B        | Х       | х  |      |       |    |    | 20     | Fixed  | B11B Branch Tracing Misses<br>Branch Instruction                                                   |

| 26         | B12         | х       | х  |      |       |    |    | 21     | Fixed  | B12 Disabling Interrupts with sysctl is non-atomic                                                 |

| 27         | B13         | х       | х  |      | х     |    |    | 21     | Fixed  | B13 Unaligned DMA Transfer<br>Modes When Using Incrementing<br>Source and Destination Address      |

| 28         | B14         |         |    |      | х     | х  | х  | 21     | NoFix  | B14 Data Cache Global Disable<br>Bit is 0 After Device Reset                                       |

| 29         | C1          | Х       | Х  | Х    | Х     | Х  | Х  | 21     | NoFix  | C1 Instruction Cache                                                                               |

| 30         | C2          | Х       | Х  |      | Х     | Х  | Х  | 21     | NoFix  | C2 Register Cache                                                                                  |

| 31         | C3          | х       | х  | х    | х     | х  | х  | 22     | NoFix  | C3 Data Address Breakpoint Fault on a CALLX                                                        |

| 32         | C4          | х       | х  | х    | х     | х  | х  | 22     | NoFix  | C4 Data Address Breakpoints on<br>Stacks and Tables                                                |

| 33         | C5          | Х       | Х  | Х    | Х     | Х  | Х  | 22     | NoFix  | C5 Pipelined Region Limitation                                                                     |

| 34         | C6          | х       | х  | х    | х     | х  | х  | 22     | NoFix  | C6 EOP and Buffer Complete<br>Interrupt                                                            |

| 35         | C7          | Х       | Х  | Х    | Х     | Х  | Х  | 22     | NoFix  | C7 MULI Fault Return                                                                               |

| 36         | C8          | х       | х  |      | х     |    |    | 23     | Fixed  | C8 (B7) Fault Handler Executes before Interrupt Handler                                            |

| 37         | C9          | Х       | Х  | Х    | Х     | Х  | Х  | 23     | NoFix  | C9 (A17) Extra RIP Read                                                                            |

| 38         | C10         | х       | х  | х    | х     | х  | х  | 23     | NoFix  | C10 (B9) Disabling and Enabling<br>Interrupts via Modifying the Interrupt<br>Mask Register (sf1)   |

| 39         | C10b        | х       | х  | x    | x     | x  | x  | 23     | NoFix  | C10b Microcoded Instructions<br>Can Be Corrupted after Writing to<br>Interrupt Mask Register (sf1) |

| 40         | C11         | х       | х  |      | х     |    |    | 24     | Fixed  | C11 NMI during Built-In-Self-Test<br>(BIST)                                                        |

| 41         | C12         | Х       | Х  |      | Х     |    |    | 24     | Fixed  | C12 BTERM# Functionality                                                                           |

| 42         | C13         | х       | х  | х    |       | х  | х  | 25     | NoFix  | C13 Modifying the Previous Frame<br>Pointer (PFP) before Returning                                 |

### Errata (Sheet 3 of 3)

|            | Prev<br>No. | Steppi  |            |   | ings    |   |    |        |               |                                                                               |  |

|------------|-------------|---------|------------|---|---------|---|----|--------|---------------|-------------------------------------------------------------------------------|--|

| New<br>No. |             | 80960CA |            |   | 80960CF |   | Pg | Status | Status ERRATA |                                                                               |  |

|            |             | C2      | <b>C</b> 3 | D | В       | С | Е  |        |               |                                                                               |  |

| 43         |             |         |            | х |         | х | х  | 26     | NoFix         | Erroneous TC Can Be Signaled<br>When Using Multiple DMA Channels              |  |

| 44         |             | х       | х          | х | х       | x | x  | 26     | NoFix         | Supervisor Access Pin Operation<br>During System-Supervisor Fault<br>Handling |  |

| 45         |             | х       | х          | х | х       | х | х  | 27     | NoFix         | Power Supply Sequence Can<br>Damage Internal Diodes                           |  |

### **Specification Changes**

| No. | Steppings |  |  | Page | Status | SPECIFICATION CHANGES                                |

|-----|-----------|--|--|------|--------|------------------------------------------------------|

|     |           |  |  |      |        |                                                      |

|     |           |  |  |      |        | None for this revision of this specification update. |

### **Specification Clarifications**

| No. | St | epping | S | Page | Status | SPECIFICATION CLARIFICATIONS                         |

|-----|----|--------|---|------|--------|------------------------------------------------------|

| NO. |    |        |   | raye | Status | SI ECHICATION GEARINGATIONS                          |

|     |    |        |   |      |        | None for this revision of this specification update. |

### **Documentation Changes**

| No. | Document<br>Revision | Page | DOCUMENTATION CHANGES                                           |  |  |  |

|-----|----------------------|------|-----------------------------------------------------------------|--|--|--|

| 1   | 270710-003           | 30   | Chapter 4 - Instruction Set Summary                             |  |  |  |

| 2   | 270710-003           | 30   | Chapter 9 - Instruction Set Reference                           |  |  |  |

| 3   | 270710-003           | 30   | Chapter 11 - External Bus Description                           |  |  |  |

| 4   | 270710-003           | 30   | Chapter 12 - Interrupt Controller                               |  |  |  |

| 5   | 270710-003           | 30   | Chapter 12 - Page 12-22, Table 12-2                             |  |  |  |

| 6   | 270710-003           | 31   | Chapter 13 - DMA Controller                                     |  |  |  |

| 7   | 270710-003           | 31   | Appendix A - Instruction Execution and Performance Optimization |  |  |  |

| 8   | 270710-003           | 31   | Appendix A - Page A-42, Section A.2.6.10                        |  |  |  |

| 9   | 270710-003           | 31   | Appendix B - Bus Interface Examples                             |  |  |  |

| 10  | 270710-003           | 31   | Appendix F - Register and Data Structures                       |  |  |  |

| 11  | 272220-002           | 31   | divi Instruction Issue changed in Quick Reference               |  |  |  |

| 12  | 272220-002           | 31   | modac Instruction Issue changed in Quick Reference              |  |  |  |

## **Identification Information**

### **Markings**

80960CA/CF processors may be identified electrically according to device type and stepping. Refer to the data sheet for instructions on how to obtain the identifier number.

The various 80960CA steppings are identified by a topside mark as indicated below.

|                | C-2 Stepping | C-3 Stepping | D-Stepping                |

|----------------|--------------|--------------|---------------------------|

| KU 80960CA -25 | SV914        | SW033        | D2                        |

| KU 80960CA -16 | SV913        | SW032        | D2                        |

|                |              |              |                           |

| A 80960CA-33   | SV908        | SW031        | D2                        |

| A 80960CA-25   | SV907        | SW030        | D2                        |

| A 80960CA-16   | SV906        | SW029        | D2                        |

| TA 80960CA-16  |              | SW147        | VA80960CA-16 <sup>1</sup> |

NOTE:

TA80960CA16,S W147 will no longer be offered. It is replaced by VA80960CA16, which has a temperature range of -40°C to +125°C, and manufactured on the D-stepping. In addition, a 25 MHz extended temperature part will be offered as VA80960CA25.

## Errata

#### 1. A2 **Bus Backoff and READY# Problem:** If either RDY# or BTERM# is asserted between the deassertion of BOFF# and the completion of the ADS# strobe, then the regenerated access will be lost or corrupted. Implication: Improper operation and/or data corruption may result. The work around is to ensure that RDY or BTERM# is not asserted from the time BOFF# is Workaround: asserted until the time that ADS# is regenerated. Status: Fixed. Refer to Summary Table of Changes to determine the affected stepping(s). 2. A5A DACK Timing Vs Ready Wait States **Problem:** The deassertion of DACK can be triggered by conditions other than the end of a Ready access. Because DACK is used as a chip select, simple connection of DACK to system DACK does not work for Ready controlled regions. Additional glue logic is required. Implication: Workaround: External logic is necessary for proper operation. This logic should latch DACK during the address cycle. Status: Fixed. Refer to Summary Table of Changes to determine the affected stepping(s). **DACK Timing with Multiple Accesses Per Bus Request** 3. A5B **Problem:** DACK deasserts early on multiple bus accesses per bus request during the following conditions. If the DMA transfer type and external bus width are unequal so that the Bus Controller is required to issue multiple bus accesses per request, then DACK deasserts on the rising edge of BLAST of the first access and stays deasserted for the duration of the request. For example, a DMA transfer type of 128 by 128 requires the Bus Controller to issue quad stores on a non-burst 32-bit external bus. Therefore DACK asserts with the first ADS and deasserts on the rising edge of BLAST of the first access. **Implication:** Improper DMA transfers may occur. Workaround: Match the DMA mode transfer width with the external bus width. The correct functioning of DACK is as follows: DACK should assert at the falling edge of ADS and remain asserted throughout the entire bus request. DACK should deassert at the rising edge of BLAST of the last access. Status: Fixed. Refer to Summary Table of Changes to determine the affected stepping(s). 4. DMA SSDEM Mode Packing and EOP A18 **Problem:** Asserting EOP during a Source Synchronized Demand Mode DMA can corrupt the last word or byte of the transfer. The following table shows the packing modes and how the SAR (Source Address Register) and DAR (Destination Address Register) are aligned in order to manifest this condition. The EOP failure point denotes where a failure will occur with respect to EOP and

individual transfers.

| Packing type | SAR                    | DAR       | EOP Fail Point |

|--------------|------------------------|-----------|----------------|

| 16-32        | Aligned                | Aligned   | All Xfers      |

| 8-16         | -                      | Aligned   | 1st Xfer Only  |

| 16-16        | Unaligned <sup>1</sup> | Aligned   | 1st Xfer Only  |

| 32-32        | Aligned                | Unaligned | 1st Xfer Only  |

NOTE:

1. Block Mode

Implication: Data corruption may occur.

- Workaround: There are three workarounds. The first one is to not use EOP but rather an interrupt to signal an asynchronous termination of a transfer. Second, if it is known that the above condition is going to happen, then throw away the last word or byte of the transfer and adjust the SAR and the BCR (Byte Count Register) accordingly. Third, for those packing modes where EOP can only cause a failure during the first transfer, a dummy transfer can be inserted as the first transfer and no data will be corrupted.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 5. A19 Suspend DMA, EOP and SDMA

- **Problem:** An unrecoverable error can occur during the time that an interrupt is being posted if the Suspend DMA function is enabled (ICON bit 15) and either an EOP or SDMA event occurs. The following conditions must exist for the error to occur:

- 1. Suspend DMA function is enabled by setting ICON Register bit 15.

- 2. Two or more DMA channels are operating at the same time.

- 3. An interrupt is actually being posted.

- 4a. An EOP is received or,

- 4b. An SDMA is executed.

- Implication: Unrecoverable error state may occur.

- **Workaround:** There are several workarounds. The Suspend DMA function should be enabled only if it can be guaranteed that an EOP or an SDMA will not occur. An SDMA can occur by first disabling the Suspend DMA function by resetting ICON Register bit 15. EOP, however, due to its asynchronous nature, cannot be used with the Suspend DMA feature enabled. Instead, a separate external hardware interrupt should be used to signal the end of a channel. An interrupt handler can then disable the channel by clearing the enable bit in the DMAC (DMA Command Register sf2) and wait until the active bit in the DMAC is cleared.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 6. A20 AEOP, SDMA and Multi-Channel DMA Operations

- **Problem:** When a Setup DMA (SDMA) instruction is issued, transfer requests on all four channels are held off until SDMA completion. It is possible to enter a state in which a DMA Load request has completed but not the corresponding Store. Once the setup is done, the pending Store request will be serviced and completed. However, during the time that the SDMA instruction is executing, an EOP on the same channel may be accepted by the DMA controller. The EOP will be serviced BEFORE the DMA cycle has completed. The Store access will never be executed.

- Implication: The transfer may be terminated prematurely and the data that is expected on the last Load may be lost.

Errata

**Workaround:** The workaround for this anomaly is to make sure that an EOP does not occur during an SDMA instruction. An alternate method of setting up a DMA channel is to use the Chaining mode with wait. However, the user cannot change the DMA mode this way.

**Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 7. A20 BEOP, SDMA and Multi-Channel DMA Operations

**Problem:** If during the time that an SDMA is issued for a channel that was the last active channel, an EOP occurs on another channel, then the Byte Count, Source Address, and Next Pointer Address pertaining to the SDMA may be corrupted.

Implication: Data corruption may occur.

- Workaround: The workaround for this anomaly is to make sure that an EOP does not occur during a SDMA instruction.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 8. A21 Disabling Branch Lookahead Causes DMA problems

- **Problem:** When using multiple DMA channels, bit 21 of the word at PRCB offset 0x20 must be zero (0). Otherwise, DMA data corruption occurs.

- Implication: When using older debug monitors, DMA corruption can occur.

- **Workaround:** Make sure bit 21 of the PRCB offset 0x20 (instruction cache configuration word) is zero (0). This disables the branch lookahead logic, so some decrease in performance may be observed.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 9. A22 NMI is Level-Triggered after RESET

- **Problem:** NMI (Non-Maskable Interrupt) normally only occurs after a high-to-low (1-to-0) transition on the NMI pin. After RESET, however, NMI is level-triggered and a low (0) on the NMI pin will generate a Non-Maskable Interrupt.

- Implication: Spurious NMI could occur.

- Workaround: Make sure the NMI pin is driven high during the RESET sequence. After RESET is deasserted, (driven high), the user must drive NMI high within 10 clocks. Otherwise, a Non-Maskable Interrupt will occur.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 10. A25 Interrupts During SYSCTL Instruction to Load and Lock the Instruction Cache

Problem: Any hardware interrupts (maskable or unmaskable) which occur during the execution of a SYSCTL instruction to load and lock the instruction cache causes the processor to malfunction. SYSCTL instructions have the configure cache message and either the load and lock 1 Kbyte or load and lock 512 bytes cache mode configuration. The processor actually enters the interrupt handler, but enters it in an unrecoverable state. The only way to completely recover from this malfunction is to reset the device.

Implication: Processor can enter an unrecoverable error state.

- Workaround: The workaround is to disable hardware interrupts while executing the SYSCTL instruction to load and lock the instruction cache. The user must also guarantee that his system never generates an NMI during the SYSCTL instruction.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 11. A26 32-32 Bit Transfers in Source-Synchronized Demand Mode with Unaligned Destination Address

**Problem:** The DMA controller is optimized to perform unaligned 32-32 bit transfers. However, when in source-synchronized demand mode, the DMA controller requires an extra DREQ# to complete the transfer when the destination address is unaligned.

For example, assume an aligned source address and a destination address which is unaligned by one byte (has an address of xxxxxx1) and a byte count of 16. The DMA controller should transfer 3 bytes for the first DREQ#, 4 bytes for the two middle DREQ#s, and 5 bytes for the last DREQ#. However, only 4 bytes are transferred for the 4th DREQ# and requires a 5th DREQ# to transfer the last byte.

All other source synchronized transfer modes with an unaligned destination address will work correctly (i.e., 16-16, 8-8, etc.).

- Implication: Improper unaligned DMA behavior may result.

- **Workaround:** The workaround is to always ensure that your destination address is aligned on a 4 byte boundary, or have your hardware generate an extra DREQ#.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 12. A27 Terminal Count (TC) pins are non-functional when using any channel in source synchronized demand mode or block mode

**Problem:** When any EOP/TC# pin is configured as an output (terminal count function), it may not ever be asserted if any of the four DMA channels is configured for either source synchronized demand mode, or block mode. The TC pin works correctly when all DMA channels are programmed only for destination synchronized demand mode or fly-by modes. This errata does not affect the operation of the EOP/TC# pin when programmed for the EOP function.

The TC pin will not be asserted when any unsynchronized DMA store is present on the external bus and the DMA controller issues the last load (the load in which TC should be asserted) of a source synchronized demand mode or block mode transfer. Note that even though TC is not asserted, the DACK# pin is asserted correctly for the load. An unsynchronized DMA store is defined to be a DMA store in which the DACK# pin is not asserted, as in source synchronized demand mode and block mode transfers.

**Implication:** For application purposes, this renders the TC pins non-functional when using these modes.

Workaround: None

**Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 13. A28 DMA and Instruction Scheduler Interaction

**Problem:** The DMA controller is implemented primarily in microcode. DMA operations are executed in microcode while providing core bandwidth for the user's program. Core resources are shared by implementing a separate hardware process for each DMA channel and one for the user code. This hardware mechanism allows the core to switch processes on clock boundaries to service either a DMA process or the user process. See Chapter 13 in the *i960*® *Cx Microprocessor User's Manual*.

Under very specific circumstances, a DMA process can cause a conditional branch instruction to branch along the incorrect path. The branch instruction unconditionally follows the path dictated by the branch prediction bit. The circumstances are:

1. The instruction scheduler must attempt to issue three instructions in parallel (a Reg-Memconditional branch triplet). For the device to execute three instructions in parallel, they must be in this order. For example:

```

CMPI r4,r5;reg-side must affect condition codes

```

ST r6,(r7)

```

BGE.f some_where;must be conditional branch ;which relies on condition codes

```

- 2. The reg-side instruction must begin on an odd word boundary.

- 3. The mem-side must be scoreboarded; i.e., the ST instruction cannot execute because of a resource limitation. The conditions in which the mem-side is scoreboarded are covered in the *i960*® *Cx Microprocessor User's Manual*.

- 4. A DMA event must occur while the mem-side is scoreboarded. A DMA event is defined to be the assertion of DREQ# on an active DMA channel and causing a process switch to a DMA task.

- 5. The branch prediction bit for the branch instruction must be incorrect for the result of the regside comparison.

- 6. Branch Lookahead must be enabled.

The instructions affected are listed below. Any combination of these instructions in the reg-memctrl ordering are affected.

| REG-side         | Mem side        | Conditional      |

|------------------|-----------------|------------------|

| ADDC             | LDA offset      | BE, BNE, BL, BLE |

| CMPI,CMP0        | LDA (reg)       | BG, BGE, BO, BNO |

| CMPDECI,CMPDECO  | LDA offset(reg) |                  |

| CMPINCI, CMPINCO |                 |                  |

| CONCMPI,CONCMPO  | LD/ST offset    |                  |

| СНКВІТ           | LD/ST (reg)     |                  |

| SCANBYTE         |                 |                  |

| SUBC             |                 |                  |

The LD/ST instructions include the byte, short, word, triple, and quad versions. The chances of this anomaly occurring in an application are exacerbated when the processor is in NIF mode, because the mem-side is always scoreboarded until the reg-side compare instruction is finished.

Implication: Incorrect program operation may occur.

**Workaround:** For the 80960CA A through C-3 stepping, errata A21 prevents simply disabling Branch Lookahead for applications which have more than one DMA channel active at a time. Multichannel DMA applications will have to prevent this code sequence in their application to workaround this errata for the 80960CA. Intel will also provide switches for the development tools (C compilers) which will prevent this sequence of instructions from taking place, as well as a method for screening existing object code for the instruction triplet. Please contact your local Intel support person for information on obtaining these tools.

Code workaround - Because it is very difficult to predict when the mem-side will be scoreboarded, code workarounds should remove all cases of the code triplet. This guarantees that the errata will not occur in an application.

The simplest workaround is to insert a nop (mov g0,g0) between the reg-side and mem-side instructions. This prevents the triplet from being issued in parallel. The Intel tools will provide this kind of workaround as an assembler patch. An alternate workaround is to reorder the instructions so the triplet is not issued in parallel. A third workaround is to combine the separate reg-side and conditional branch instructions into a single compare and branch (cobr) instruction.

| CMPI  | r4,r5;insert a nop               |

|-------|----------------------------------|

| MOV   | a0,a0                            |

| ST    | r6,(r7)                          |

| BGE.f | some_where                       |

|       |                                  |

| ST    | r6,(r7);reorder the instructions |

| CMPI  | r4,r5                            |

| BGE.f | some_where                       |

|       |                                  |

ST r6,(r7);Use a cobr instruction

CMPIBGE.f r4,r5,some\_where #.

**Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 14. A29 Destination Synchronized 128- to 128-Bit Quad-Word Transfer Mode

- **Problem:** The destination synchronized multi-cycle quad-word transfer mode will execute the final transfer (last sixteen bytes) immediately without waiting for the final DREQ#. A 32 byte transfer, for example, will only require a single DREQ# to transfer both quad words. The single DREQ# also causes two DACKS# to be asserted. When the DMA is programmed to transfer a single quad word (16 bytes), DMA will work correctly and require a single DREQ#. This erratum does not affect the fly-by, block, or source synchronized 128- to 128-bit quad word transfer modes.

- Implication: Synchronous DMA operation may occur.

- Workaround: Do not use destination synchronized multi-cycle quad-word DMA.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 15. A30 Disabling the Instruction Cache

- **Problem:** The instruction cache cannot be disabled while the DMA is active. Prefetch algorithms operate differently with the instruction cache disabled. An interrupt, DMA event, and instruction prefetch all occurring around the same time can infinitely scoreboard the prefetch, causing user code to stop executing at the prefetch. This erratum cannot happen while the instruction cache is enabled.

- Implication: No stepping of the 80960CA is effected by this errata.

- Workaround: The only way to recover from this condition is to reset the device.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

### 16. A31 Interrupt Can Cause User Process Stall when DMA Active Under Certain Complex Conditions

- **Problem:** An interrupt request can cause the user program to stop execution when several specific events occur in sequence under strict timing requirements. The full explanation of this condition can be found in the paper titled "80960CF User Process Stall Bug" available through Intel application's FaxBack system; document number 2050. The FaxBack telephone number is 1-800-628-2283 or 916-356-3105 from outside the U.S. and Canada. The conditions required to cause the stall are:

- 1. A REG-format instruction followed by an "invalid" word in the cache. An "invalid" word is a word that was not written into the cache due to a change of program flow. This REG-format instruction must be on an even word (address ending in 0x0 or 0x8).

- 2. An instruction fetch issued in parallel with the execution of this REG-format instruction.

- 3. MEM side of CPU scoreboarded (e.g., due to bus queues full) causing fetch to be canceled.

- 4. DMA process switch occurring at least 3 clocks after the fetch, and MEM-side must still be scoreboarded.

- 5. Interrupt request occurs while MEM-side still scoreboarded.

This is most likely to occur under heavy bus traffic with 0 data to data wait states, heavy DMA activity, and heavy interrupt activity.

- Implication: Only the 80960CF B step is affected.

- **Workaround:** DMA activity will continue until the DMA transfer is "done" (e.g., null chaining pointer, zero byte count, EOP). To recover from this condition, reset the device.

- **Status:** Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 17. A32 Register Cache

- **Problem:** Programming a register cache size of zero (0) causes the processor to generate an operation fault while performing a return. During proper operation, a value of zero (0) should yield one (1) set of register cache.

- Implication: Improper program operation may occur.

- Workaround: Program the register cache size with a value of one (1). A value of zero (0) or one (1) yields one (1) set of register cache.

- **Status:** NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 18. B1 Cache Functionality/Re-fetching Cached Instructions

**Problem:** If loops exceed the cache size (256 instructions), even by one instruction, then all instructions in that loop will be fetched again. This can be eliminated by setting bit 31 of the PRCB offset 0x20 to a one. However, setting this bit may impact performance. As a rule of thumb, it would be best to operate with bit 31 of the PRCB offset 0x20 cleared unless this cache re-fetching is clearly affecting the performance of the design.

Further analysis of how the 80960CA fetches instructions shows that other conditions exist where instructions are fetched from memory instead of being executed from the cache. This is a result of a change that improves the performance of the prefetch mechanism. Instructions are fetched into an instruction queue before they are executed. If an instruction is executed, then it is loaded into the cache. If an instruction is not executed because of a branch or a call being taken, then that instruction may not be loaded into the cache. This may leave instructions in the cache that are invalid, although the tag for the current cache line is valid. Extra fetches occur because of how the prefetch mechanism handles an invalid instruction when no cache miss occurs.

|                                                                                              | This erratum may affect performance as much if not greater than the setting of bit 31 mentioned above. Bit 31 enables or disables the original slow prefetching algorithm used in previous steppings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                              | Be aware that even with the above problem corrected, there is the possibility of seeing instructions being fetched that would appear to have been fetched previously. This extra fetching occurs because the cache is only guaranteed to be loaded if an instruction is executed, not just fetched.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| Implication:                                                                                 | Performance may be negatively impacted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

| Workaround:                                                                                  | Setting bit 31 is considered the best workaround.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

| Status:                                                                                      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 19.                                                                                          | B3 COBR Branch Trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Problem:                                                                                     | A Branch Trace may be incorrectly reported on a cobr (Compare and Branch) instruction that is scoreboarded by a previous instruction. This occurs only when trace faults are enabled. Because the compare is scoreboarded, the branch never takes place; however, the trace fault is still reported.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Implication:                                                                                 | Debugger may report branch trace when one did not occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| Workaround:                                                                                  | Do not order a cobr instruction just after instructions such as multiply where one could possibly be using resources needed by the cobr instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| Status:                                                                                      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 20.                                                                                          | B5 EOP and DREQ Deassertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

| Problem:                                                                                     | A DMA cycle may terminate prematurely if the DMA controller accepts a DMA request and EOP occurs while DREQ is still asserted. Data may be buffered internally but never stored.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| Implication:                                                                                 | Data corruption may occur.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Workaround:                                                                                  | Do not assert EOP while DREQ is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

|                                                                                              | Bo not assert hor while bring is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| Status:                                                                                      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| Status:<br>21.                                                                               | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|                                                                                              | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |

| 21.                                                                                          | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B6 DREQ Sampling</li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 21.<br>Problem:                                                                              | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s). B6 DREQ Sampling In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on external READY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 21.<br>Problem:<br>Implication:                                                              | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B6 DREQ Sampling</li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on external READY.</li> <li>Extra DMA transfers may occur.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

| 21.<br>Problem:<br>Implication:<br>Workaround:                                               | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B6 DREQ Sampling</li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on external READY.</li> <li>Extra DMA transfers may occur.</li> <li>Make sure DREQ is de-asserted before wait-state timer expires.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                 |  |

| 21.<br>Problem:<br>Implication:<br>Workaround:<br>Status:                                    | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B6 DREQ Sampling</li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on external READY.</li> <li>Extra DMA transfers may occur.</li> <li>Make sure DREQ is de-asserted before wait-state timer expires.</li> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> </ul>                                                                                                                                                                                                                                                                                                        |  |

| 21.<br>Problem:<br>Implication:<br>Workaround:<br>Status:<br>22.                             | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B6 DREQ Sampling</li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on external READY.</li> <li>Extra DMA transfers may occur.</li> <li>Make sure DREQ is de-asserted before wait-state timer expires.</li> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li>B8 SYSCTL followed by RET May Incorrectly Fault</li> <li>A sysctl instruction followed by a ret instruction with no instructions in between may cause the</li> </ul>                                                                                                                                     |  |

| 21.<br>Problem:<br>Implication:<br>Workaround:<br>Status:<br>22.<br>Problem:                 | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li><b>B6 DREQ Sampling</b></li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on the external READY.</li> <li>Extra DMA transfers may occur.</li> <li>Make sure DREQ is de-asserted before wait-state timer expires.</li> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li><b>B8 SYSCTL followed by RET May Incorrectly Fault</b></li> <li>A sysctl instruction followed by a ret instruction with no instructions in between may cause the false generation of an OPERATION.UNIMPLEMENTED fault.</li> </ul>                                                             |  |

| 21.<br>Problem:<br>Implication:<br>Workaround:<br>Status:<br>22.<br>Problem:<br>Implication: | <ul> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li><b>B6 DREQ Sampling</b></li> <li>In some DMA modes, the DREQ signal is sampled when the internal wait-state generator has timed out, regardless of the state of the external READY signal. This could lead to extra DMA cycles being generated erroneously by the incorrect sampling of DREQ during the time that READY is deasserted by an external memory system. Sampling of DREQ does not depend on the external system trying to complete a slow memory cycle; i.e., DREQ sampling does not depend on the external READY.</li> <li>Extra DMA transfers may occur.</li> <li>Make sure DREQ is de-asserted before wait-state timer expires.</li> <li>Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).</li> <li><b>B8 SYSCTL followed by RET May Incorrectly Fault</b></li> <li>A systel instruction followed by a ret instruction with no instructions in between may cause the fase generation of an OPERATION.UNIMPLEMENTED fault.</li> <li>User software operation may be negatively impacted.</li> </ul> |  |

T

#### 23. B10 Terminal Count Operation

**Problem:**

On the 80960CA only (80960CF not affected): on steppings previous to the D-step the Terminal Count (TC) pin timing does not become active at the specified time. TC should have the same timing as DACK#, but does not. The following describes the condition:

**Source Synchronized Demand Mode (SSDEM):** The TC bit will not become active until all stores related to the last access are issued. For most aligned transfers in which there is no unpacking, the number of clock cycles between the deassertion of the last DACK and the active edge of TC will be 20. This assumes the 4:1 DMA cycle mode.

Block Mode: Same as SSDM with above.

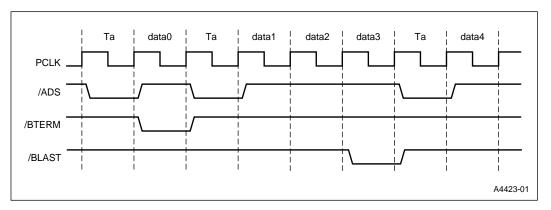

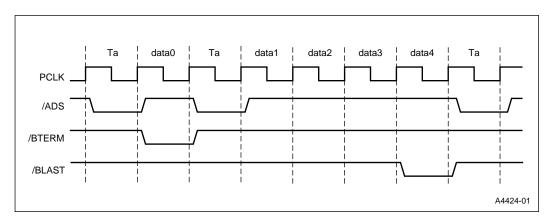

**Destination Synchronized Demand Mode (DSDEM):** The last store is synchronized with the external bus. When the DACK deasserts, there are approximately 17 cycles to the active edge of TC.