### 80960HA/HD/HT

**Specification Update**

April 1998

**Notice:** The 80960HA/HD/HT may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update..

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 80960HA/HD/HT may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are documented in this Specification Update.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 1998

\*Third-party brands and names are the property of their respective owners.

# int<sub>el</sub>。 *Contents*

| Revision History             | 1  |

|------------------------------|----|

| Preface                      | 2  |

| Summary Table of Changes     | 4  |

| Identification Information   | 7  |

| Errata                       | 8  |

| Specification Changes        | 28 |

| Specification Clarifications | 29 |

| Documentation Changes        | 32 |

### **Revision History**

| Date       | Version | Description                                                                                                                                                                                                 |

|------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.4/4.0/00 | 005     | Added "B2" Stepping to errata table.                                                                                                                                                                        |

| 04/10/98   | 005     | Added errata item 27. Power Supply Sequence Can Damage Internal Diodes                                                                                                                                      |

|            |         | Added errata item 26. Deasserting Level-Detect Interrupts During CISC Instructions<br>Can Produce Spurious INVALID_OPCODE Faults                                                                            |

| 11/3/97    | 004     | Added Specification Clarification 3. BSTALL Does Not Always Coincide With BREQ.<br>Added Documentation Changes 23 and 24 to incorporate this specification<br>clarification into the 80960Hx documentation. |

|            |         | Added errata item 25. DT/R# Timings Do Not Meet Published Specifications.                                                                                                                                   |

| 10/07/97   | 003     | Removed Specification Change items 1–3; these changes have been incorporated into the <i>80960HA/HD/HT 32-Bit High Performance Superscalar Processor</i> datasheet.                                         |

|            |         | Added descriptions of the B-0 stepping.                                                                                                                                                                     |

|            |         | Added errata items:                                                                                                                                                                                         |

|            |         | 20. Using atmod or sysctl to Change IMSK or IPND MMRS Can Hang the Processor                                                                                                                                |

|            |         | 21. Storing the Contents of the I_CACHE to External Memory Also Disables the Cache                                                                                                                          |

| 01/01/97   | 002     | 22. PCHK# Pin Does Not Indicate Parity Failures On HD and HT Processors                                                                                                                                     |

|            |         | 23. Spurious INVALID_OPCODE Faults Can Occur with Level-Detect Interrupts                                                                                                                                   |

|            |         | 24. Parity Can Fail on Reliable Data and Can Pass on Corrupted Data                                                                                                                                         |

|            |         | Added Document Change items:                                                                                                                                                                                |

|            |         | 5. Page 6-45                                                                                                                                                                                                |

|            |         | 13. Page 11-19                                                                                                                                                                                              |

| 07/01/96   | 001     | This is the new 80960Hx Specification Update document. It contains all identified errata published prior to this date.                                                                                      |

| 12/08/95   | 1.01    | Add Specification Clarification 2. Instruction Breakpoints Are Superseded by Invalid Opcode Faults                                                                                                          |

|            |         | The A-1 stepping fixes the following errata from the A-0 (A-0 Errata Sheet numbering shown):                                                                                                                |

|            |         | 14. RESET Has Priority Over HOLD,                                                                                                                                                                           |

|            |         | 15. Data Cache Global Disable Bit (CCON.dci, sf2) May Take 1 Extra Clock Cycle To Complete,                                                                                                                 |

|            |         | 16. Low Temperature Operating Limit Increased to 25°C, and                                                                                                                                                  |

|            |         | 17. IPND Register Not Cleared Automatically.                                                                                                                                                                |

| 11/17/95   | 1.00    | Remaining errata have been renumbered for the A-1 stepping. See the Summary of Known Errata, pg. 3                                                                                                          |

| ,          |         | Add errata:                                                                                                                                                                                                 |

|            |         | #20 Halt Mode Does not Conserve Power, and                                                                                                                                                                  |

|            |         | 13. Invalidating the Data Cache Automatically Re-enables It                                                                                                                                                 |

|            |         | Modifications since rev 0.11 (10/27/95) of the A-0 errata sheet                                                                                                                                             |

|            |         | #8 Hold $V_{CC}$ Above 3.15 V and Below 3.45 V                                                                                                                                                              |

|            |         | #15 DEN# Remains Asserted During ADS# Cycles                                                                                                                                                                |

|            |         | #16 TRST# Input Can Be Tied Low, and                                                                                                                                                                        |

|            |         | #17 Burst Accesses on 8- and 16-Bit Buses Do Not Behave Like the Cx Processor                                                                                                                               |

### **Preface**

As of July, 1996, Intel's Computing Enhancement Group has consolidated available historical device and documentation errata into this new document type called the Specification Update. We have endeavored to include all documented errata in the consolidation process, however, we make no representations or warranties concerning the completeness of the Specification Update.

This document is an update to the specifications contained in the Affected Documents/Related Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

#### **Affected Documents/Related Documents**

| Title                                                                            | Order  |

|----------------------------------------------------------------------------------|--------|

| 80960HA/HD/HT 32-Bit High Performance Superscalar Processor datasheet            | 272495 |

| i960 <sup>®</sup> Hx Microprocessor User's Manual                                | 272484 |

| i960 <sup>®</sup> Hx Microprocessor Instruction Set and Register Quick Reference | 272792 |

| AP-506: Designing for 80960Cx and 80960Hx Compatibility                          | 272556 |

| Reduced Power Options for the 80960HA/HD/HT Processor <sup>1</sup>               |        |

1. Can be downloaded from the Intel worldwide web homepage at: http://www.intel.com/design/i960/technote/hxlopwr.htm

#### Nomenclature

**Errata** are design defects or errors. These may cause the published (component, board, system) behavior to deviate from published specifications. Hardware and software designed to be used with any component, board, and system must consider all errata documented.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

*Note:* Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, etc.).

### **Summary Table of Changes**

#### **Codes Used in Summary Table**

#### Stepping

|        | X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark)       |                                                                                                               |

|        | or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Page   |                 |                                                                                                               |

|        | (Page):         | Page location of item in this document.                                                                       |

| Status |                 |                                                                                                               |

|        | Doc:            | Document change or update will be implemented.                                                                |

|        | Fix:            | This erratum is intended to be fixed in a future step of the component.                                       |

|        | Fixed:          | This erratum has been previously fixed.                                                                       |

|        | NoFix:          | There are no plans to fix this erratum.                                                                       |

|        | Eval:           | Plans to fix this erratum are under evaluation.                                                               |

|        |                 |                                                                                                               |

#### Row

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

### Errata

| No. | Steppings |           |    |           |           |           | Dese | Status | ERRATA                                                                                                        |  |

|-----|-----------|-----------|----|-----------|-----------|-----------|------|--------|---------------------------------------------------------------------------------------------------------------|--|

| NO. | <b>A0</b> | <b>A1</b> | A2 | <b>B0</b> | <b>B1</b> | <b>B2</b> | Page | Status | ERRATA                                                                                                        |  |

| 1   | х         | Х         | Х  |           |           |           | 8    | Fixed  | Parity Failure on 8- and 16-bit Unaligned Loads                                                               |  |

| 2   | х         | Х         | х  | х         | х         | х         | 8    | NoFix  | Read Wrong Location from Non-Burst, 8- and 16-bit<br>Memory Regions                                           |  |

| 3   | Х         | Х         | Х  | Х         | Х         | Х         | 9    | NoFix  | Breakpoints on Stacks Produce Wrong Fault IP                                                                  |  |

| 4   | х         | х         | х  |           |           |           | 9    | Fixed  | Parity Faults May Not Report Correct Address and Access Type                                                  |  |

| 5   | х         | Х         | х  |           |           |           | 9    | Fixed  | PMCON15 Temporarily Initialized Incorrectly During<br>RESET                                                   |  |

| 6   | Х         | Х         | Х  |           |           |           | 10   | Fixed  | BCON Register is not Cleared Before Software Reset                                                            |  |

| 7   | Х         | Х         | Х  |           |           |           | 10   | Fixed  | MODTC Command Can Set TC Register Event Flags                                                                 |  |

| 8   | х         | Х         | х  | х         | Х         | х         | 10   | NoFix  | Parity Faults Cannot Be Disabled Separate from the<br>PCHK# Pin                                               |  |

| 9   | Х         | Х         | Х  |           |           |           | 10   | Fixed  | Timer Terminal Count (TMR.tc) Bit Cannot Bear Polling                                                         |  |

| 10  | х         | Х         | х  | х         | х         | х         | 11   | NoFix  | Return Instruction Pointer (RIP) Cannot be Stored by Software                                                 |  |

| 11  | Х         | Х         | Х  |           |           |           | 11   | Fixed  | WAIT# Pin Asserts During NXDA Wait States                                                                     |  |

| 12  | х         | Х         | х  |           |           |           | 12   | Fixed  | Software Interrupts Can Access the Wrong Handler<br>Address                                                   |  |

| 13  | Х         | Х         | Х  |           |           |           | 12   | Fixed  | Invalidating the Data Cache Automatically Re-enables It                                                       |  |

| 14  | Х         |           |    |           |           |           | 13   | Fixed  | xed         RESET Has Priority Over HOLD                                                                      |  |

| 15  | х         |           |    |           |           |           | 13   | Fixed  | Data Cache Global Disable Bit (CCON.dci, sf2) May Take 1<br>Extra Clock Cycle To Complete                     |  |

| 16  | Х         |           |    |           |           |           | 14   | Fixed  | Low Temperature Operating Limit Increased to 25°C                                                             |  |

| 17  | Х         |           |    |           |           |           | 14   | Fixed  | IPND Register Not Cleared Automatically                                                                       |  |

| 18  | Х         | Х         | Х  |           |           |           | 15   | Fixed  | Fixed Cycle Type Bits (CT3:0) Do Not Indicate Some Fault Types                                                |  |

| 19  | х         | х         | х  | х         | х         | х         | 16   | NoFix  | Operation Fault Occurs When Clearing the IMASK (sf1)<br>Register                                              |  |

| 20  | х         | Х         | х  |           |           |           | 17   | Fixed  | Using atmod or sysctl to Change IMSK or IPND MMRS Can<br>Hang the Processor                                   |  |

| 21  | х         | Х         | х  |           |           |           | 18   | Fixed  | Storing the Contents of the I_CACHE to External Memory Also Disables the Cache                                |  |

| 22  | х         | х         | х  |           |           |           | 18   | Fixed  | PCHK# Pin Does Not Indicate Parity Failures On HD and HT Processors                                           |  |

| 23  | х         | Х         | х  | Х         | Х         | х         | 18   | NoFix  | Spurious INVALID_OPCODE Faults Can Occur with<br>Level-Detect Interrupts                                      |  |

| 24  | х         | Х         | х  | Х         |           |           | 21   | Fixed  | Parity Can Fail on Reliable Data and Can Pass on Corrupted Data                                               |  |

| 25  | Х         | Х         | Х  | Х         | Х         | Х         | 22   | NoFix  | DT/R# Timings Do Not Meet Published Specifications                                                            |  |

| 26  | х         | х         | x  | x         | х         | x         | 24   | NoFix  | Deasserting Level-Detect Interrupts During CISC<br>Instructions Can Produce Spurious INVALID_OPCODE<br>Faults |  |

| 27  | Х         | Х         | Х  | Х         | Х         | Х         | 27   | No Fix | Power Supply Sequence Can Damage Internal Diodes                                                              |  |

#### **Specification Changes**

| No. | Steppings |   | Page Status | SPECIFICATION CHANGES |                                                     |

|-----|-----------|---|-------------|-----------------------|-----------------------------------------------------|

| NO. | #         | # | Faye        | Status                | STEELING ATTON GHANGES                              |

|     |           |   |             |                       | None for this revision of the specification update. |

#### **Specification Clarifications**

| No. | St | Steppings |   | Page | Status | SPECIFICATION CLARIFICATIONS                                              |

|-----|----|-----------|---|------|--------|---------------------------------------------------------------------------|

| NO. | #  | #         | # | Fage | Status | SPECIFICATION CLARIFICATIONS                                              |

| 1   |    |           |   | 29   |        | Burst Accesses on 8- and 16-Bit Buses Do Not Behave Like the Cx Processor |

| 2   |    |           |   | 30   |        | Instruction Breakpoints Are Superseded by Invalid Opcode Faults           |

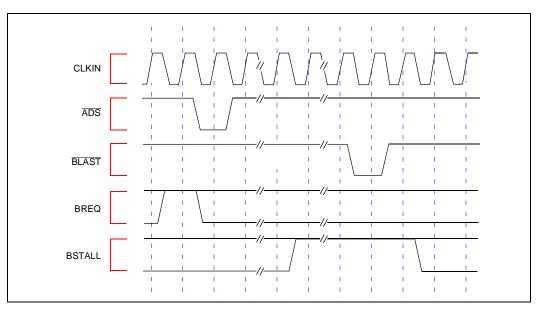

| 3   |    |           |   | 30   |        | BSTALL Does Not Always Coincide With BREQ                                 |

#### **Documentation Changes**

| No. | <b>Document Revision</b> | Page | Status | DOCUMENTATION CHANGES                            |

|-----|--------------------------|------|--------|--------------------------------------------------|

| 1   | 272484                   | 32   |        | Page 3-11, Table 3-4                             |

| 2   | 272484                   | 32   |        | Page 3-11, Table 3-4                             |

| 3   | 272484                   | 32   |        | Page 3-26                                        |

| 4   | 272484                   | 32   |        | Page 4-6, Section 4.4.3                          |

| 5   | 272484                   | 32   |        | Page 6-45                                        |

| 6   | 272484                   | 32   |        | Page 6-60, Table 6-8                             |

| 7   | 272484                   | 33   |        | Page 6-61, Figure 6-4                            |

| 8   | 272484                   | 33   |        | Page 6-62, Table 6-9                             |

| 9   | 272484                   | 33   |        | Page 6-63, Figure 6-5                            |

| 10  | 272484                   | 33   |        | Page 6-64, Figure 6-6                            |

| 11  | 272484                   | 33   |        | Page 6-116                                       |

| 12  | 272484                   | 33   |        | Page 8-6, Figure 6-6                             |

| 13  | 272484                   | 34   |        | Page 11-19                                       |

| 14  | 272484                   | 34   |        | Page 12-15                                       |

| 15  | 272484                   | 34   |        | Page 13-4, Figure 13-2                           |

| 16  | 272484                   | 34   |        | Page 13-9, Section 13.2.2.5                      |

| 17  | 272484                   | 34   |        | Page 13-11, Section 13.2.2.5                     |

| 18  | 272484                   | 35   |        | Page 13-23, Table 13-7                           |

| 19  | 272484                   | 35   |        | Page 13-37, Figure 13-9                          |

| 20  | 272484                   | 35   |        | Page 13-37, Figure 13-10                         |

| 21  | 272484                   | 35   |        | Page 15-15                                       |

| 22  | 272484                   | 35   |        | Pages E-41, E-44, E-45, Examples E-1, E-3, E-4   |

| 23  | 272556                   | 35   |        | AP-506, Page 17, "BSTALL" Section, 4th Paragraph |

| 24  | 272495                   | 36   |        | Datasheet, Page 8, Table 6                       |

### **Identification Information**

#### **Stepping Register**

80960HA/HD/HT processors may be identified electrically according to device type and stepping. The g0 register contains this information after reset initialization. The following table lists the devices to which this errata sheet applies:

#### Table 1. Device Identifier Codes Found in the g0 Register After Reset

|                   |            | Device     |            |

|-------------------|------------|------------|------------|

| Stepping          | 80960HA    | 80960HD    | 80960HT    |

| A-0               | 0x08840013 | 0x08841013 | 0x08842013 |

| A-1 and A-2       | 0x18840013 | 0x18841013 | 0x18842013 |

| B-0, B-1, and B-2 | 0x28840013 | 0x28841013 | 0x28842013 |

Refer to the data sheet for instructions on how to obtain the identifier number from the g0 register.

#### **JTAG Registers**

See the datasheet, release -006, dated July 1997, Section 5.1 80960Hx Boundary Scan Chain, pages 74-77 for the boundary scan chain definition.

See the data sheet, release -006, dated July 1997, Section 5.2 Boundary Scan Description Language Example (BSDL) for the simulator file describing the boundary scan configuration in the PGA and PQ2 packages. Contact your Intel sales office for an ASCII version of these files. Optionally, these BSDL files can be downloaded from the Intel worldwide web homepage at: http://www.intel.com/design/i960/swsup/.

See the user's manual, release -001, dated November 1995, Section 16.2 Boundary Scan (JTAG) for a full description of the implemented boundary scan registers and instructions.

### Errata

| 1.           | Parity Failure on 8- and 16-bit Unaligned Loads                                                                                                                                                                                             |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | The parity detection logic can falsely indicate a parity failure under specific conditions.                                                                                                                                                 |

| Implication: | False parity failures may result during unaligned short reads on an 8- or 16-bit bus.                                                                                                                                                       |

|              | Parity must be enabled on that 8- or 16-bit memory region for the failure to occur. Also, the error does not appear if the 8- or 16-bit memory region is designated as cacheable.                                                           |

|              | This error does not affect 32-bit memory regions.                                                                                                                                                                                           |

| Workaround:  | One or more of the following conditions will prevent this error:                                                                                                                                                                            |

|              | • Disable parity for 8- or 16-bit memory regions containing unaligned data.                                                                                                                                                                 |

|              | • Make the 8- or 16-bit memory region cacheable. (Since cacheable loads are always promoted to word loads, the errata conditions never occur.)                                                                                              |

|              | • Do not use short loads ( <i>ldis</i> or <i>ldos</i> ) on unaligned data in 8- or 16-bit regions. If necessary, break short loads into two discrete byte loads.                                                                            |

|              | These workarounds do not necessarily have to be removed after this errata is corrected in silicon.                                                                                                                                          |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                             |

| 2.           | Read Wrong Location from Non-Burst, 8- and 16-bit Memory Regions                                                                                                                                                                            |

| Problem:     | Under certain conditions, the processor reads a wrong memory location when reading unaligned data from either an 8- or 16-bit memory region.                                                                                                |

|              | The failure mode occurs when all the following conditions are present:                                                                                                                                                                      |

|              | Bursting disabled                                                                                                                                                                                                                           |

|              | Pipelining enabled                                                                                                                                                                                                                          |

|              | • 8- or 16-bit memory region                                                                                                                                                                                                                |

|              | • $N_{RAD} = 0$ and $N_{RDD} \neq 0$                                                                                                                                                                                                        |

|              | • Unaligned memory read access that crosses a 16-byte (quad word) boundary                                                                                                                                                                  |

|              | If any of the above conditions are not present, the processor behaves correctly.                                                                                                                                                            |

|              | When the above conditions are present, the processor may fail to access the correct location in the next 16-byte memory segment. Instead, it may "wrap around" and access a wrong location at the beginning of the current 16-byte segment. |

| Implication: | There is little impact to the user since it is impractical to design a pipelined memory systems using NRAD = 0 with NRDD $\neq$ 0.                                                                                                          |

| Workaround:  | In every 8- or 16-bit memory region where bursting is disabled and pipelining is enabled, set NRAD $\neq 0$ or NRDD = 0. Else, avoid at least one of the other conditions listed above.                                                     |

| Status:      | <b>NoFix.</b> Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                      |

|              |                                                                                                                                                                                                                                             |

| 3.           | Breakpoints on Stacks Produce Wrong Fault IP                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | When a data breakpoint is set on a stack location and a <i>call</i> , <i>callx</i> , or <i>calls</i> instruction causes a flush to that stack location, the resulting trace fault record may report the instruction pointer (IP) of the called procedure instead of the calling instruction.                                                                                                                                     |

|              | This error occurs only when the procedure call causes a frame flush from the on-chip register cache to the procedure stack.                                                                                                                                                                                                                                                                                                      |

| Implication: | The IP returned for breakpoints set on stack locations is unreliable.                                                                                                                                                                                                                                                                                                                                                            |

| Workaround:  | Avoid setting data breakpoints on the stack. Else, ensure that the register cache is large enough to prevent frame spills during debugging.                                                                                                                                                                                                                                                                                      |

|              | Otherwise, ignore the fault IP if you only need to know that data was flushed to the stack.                                                                                                                                                                                                                                                                                                                                      |

| Status:      | NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                  |

| 4.           | Parity Faults May Not Report Correct Address and Access Type                                                                                                                                                                                                                                                                                                                                                                     |

| Problem:     | When a parity fault occurs, the fault record may report the wrong faulting address and bus access type. Specifically, if another load or fetch access immediately follows the faulting access, the fault record address and bus access type describes the second access instead of the faulting access.                                                                                                                          |

| Implication: | The faulting address and bus access type in a parity fault record are not reliable.                                                                                                                                                                                                                                                                                                                                              |

| Workaround:  | Ignore the address of faulting instruction and the access type word of the parity fault record.                                                                                                                                                                                                                                                                                                                                  |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                  |

| 5.           | PMCON15 Temporarily Initialized Incorrectly During RESET                                                                                                                                                                                                                                                                                                                                                                         |

| Problem:     | The PMCON15 bytes loaded from the Initialization Boot Record (IBR) after RESET is deasserted become corrupted inside the processor. The resulting wait state profile can cause initialization read accesses to have more address-to-data (NRAD) and data-to-data (NRDD) wait states than intended.                                                                                                                               |

|              | This problem corrects itself later during initialization when the processor overwrites PMCON15 with the correct wait state profile from the Control Table image in user memory.                                                                                                                                                                                                                                                  |

|              | Specifically, the low nibble of IBR PMCON Byte 1 is logically OR'd with the high nibble of PMCON Byte 0.                                                                                                                                                                                                                                                                                                                         |

|              | The write wait states in Byte 1 are not at issue here because no writes occur during processor initialization after PMCON15 is overwritten from the Control Table.                                                                                                                                                                                                                                                               |

| Implication: | If the workaround is ignored, some systems may "hang" indefinitely during processor initial-<br>ization. Memory systems that use READY# during processor initialization cannot afford arbitrary<br>extra wait states because the processor ignores the READY# signal until after the wait states<br>expire. In that case, the processor can "hang" during initialization, awaiting a READY# signal that<br>has already occurred. |

| Workaround:  | Program IBR address 0xFEFFFF34 with 0x00.                                                                                                                                                                                                                                                                                                                                                                                        |

|              | No workaround is strictly necessary for memory systems that use the internal wait state generator. Processor initialization proceeds correctly, but possibly at a slower speed until the processor loads the Control Table from external memory.                                                                                                                                                                                 |

|              | This workaround does not necessarily have to be removed once this errata is corrected in silicon.                                                                                                                                                                                                                                                                                                                                |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                                                                                                  |

| 6.           | BCON Register is not Cleared Before Software Reset                                                                                                                                                                                                                                                                 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Processor microcode does not clear the BCON.sirp bit before performing a sysctl software reset.                                                                                                                                                                                                                    |

| Implication: | A TYPE MISMATCH fault is generated if the BCON.sirp bit is set when a software reset is executed.                                                                                                                                                                                                                  |

| Workaround:  | Clear BCON.sirp before executing a <i>sysctl</i> reset sequence.                                                                                                                                                                                                                                                   |

|              | This workaround does not necessarily have to be removed after this errata is corrected in silicon.                                                                                                                                                                                                                 |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                    |

| 7.           | MODTC Command Can Set TC Register Event Flags                                                                                                                                                                                                                                                                      |

| Problem:     | The <i>modtc</i> instruction can be used to set event flags in the Trace Control (TC) Register. Normally, event flags are set by hardware trace events and cleared by user software with <i>modtc</i> . There is no utility in the user setting those flags.                                                       |

| Implication: | User code could accidentally set the TC Register event flags with unpredictable results.                                                                                                                                                                                                                           |

| Workaround:  | Only use <i>modtc</i> to clear event flags.                                                                                                                                                                                                                                                                        |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                    |

| 8.           | Parity Faults Cannot Be Disabled Separate from the PCHK# Pin                                                                                                                                                                                                                                                       |

| Problem:     | Contrary to section 16.3.5 "Parity Generation and Checking" in the user's manual revision -001 (dated November 1995), parity faults cannot be disabled independently from the hardware parity checking pin, PCHK#. There is no bit in the PRCB Fault Configuration Word to enable/disable faults on parity errors. |

| Implication: | When parity is enabled, parity faults and the PCHK# pin responds to parity failures. Users cannot independently disable one or the other response.                                                                                                                                                                 |

| Workaround:  | Under evaluation.                                                                                                                                                                                                                                                                                                  |

| Status:      | NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                    |

| 9.           | Timer Terminal Count (TMR.tc) Bit Cannot Bear Polling                                                                                                                                                                                                                                                              |

| Problem:     | The TMRx.tc bit randomly fails to go true (high) if polled by software when the timer is used in one-shot mode. Timer0 and Timer1 are both affected.                                                                                                                                                               |

|              | Specifically, if the user software reads TMRx.tc at or about the same time the bit is set by the processor, the bit never gets set. The timer expires and halts as normal.                                                                                                                                         |

| Implication: | This errata affects applications that use the timer(s) to produce finite, one-shot delays. Applications that require cyclic, periodic delays can usually use the timer interrupts instead of polling.                                                                                                              |

| Workaround:  | Use either of the following techniques:                                                                                                                                                                                                                                                                            |

|              | 1. Poll the Timer Count Register (TCRx) until it decrements to zero. In one-shot mode, TCRx remains cleared when it reaches 0x0000000.                                                                                                                                                                             |

|              | 2. Poll the Timer Enable bit (TMRx.en) until it clears. In one-shot mode, TMRx.en clears when TCRx reaches 0x00000000.                                                                                                                                                                                             |

|              | These workarounds do not necessarily have to be removed after this errata is corrected in silicon.                                                                                                                                                                                                                 |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                    |

#### 10. Return Instruction Pointer (RIP) Cannot be Stored by Software

**Problem:**

A fault occurs when writing the RIP (located in register r2) directly to an external address using the following code sequence.

```

lda <address>, r6 # the register used is not significant

st RIP, (r6)

```

The following code sequence does not produce a fault.

| mov RIP, | r7 | # | mov  | and   | lda   | execute | in | parallel |

|----------|----|---|------|-------|-------|---------|----|----------|

|          |    | # | (1 0 | clock | с сус | cle)    |    |          |

lda <address>, r6

st r7, (r6)

- Implication: Storing the RIP to external memory is a common debug method, but rarely used in actual applications. Of course, user software should never modify (write) the RIP directly. Section 7.2 "Modifying the PFP Register" in the user's manual, revision -001 (dated November 1995) describes the recommended way to change the processor's context.

- **Workaround:** Use an intermediate register to write the RIP from *r*<sup>2</sup> to an external address.

This workaround does not necessarily have to be removed after this errata is corrected in silicon.

**Status:** NoFix. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 11. WAIT# Pin Asserts During NXDA Wait States

- **Problem:** The WAIT# pin toggles true (low) during internally generated NXDA wait states. These extra WAIT# signals occur only when a bus request requires multiple bus accesses.

- Implication: Applications that use WAIT# to derive a write data strobe can generate sporadic strobes between valid memory accesses.

- **Workaround:** If your application uses WAIT# to qualify write strobes, modify your write strobe logic to ignore any WAIT# signals after BLAST# and before ADS#. A 1-bit state machine is sufficient. Add the equivalent of the following ABEL logic equations to your strobe logic:

| write_en   | := | ads # (write_en & !blast);        |

|------------|----|-----------------------------------|

| write0_out | =  | <pre>write0 &amp; write_en;</pre> |

| writel_out | =  | write1 & write_en;                |

| write2_out | =  | write2 & write_en;                |

| write3_out | =  | write3 & write_en;                |

|            |    |                                   |

Status: Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).

| 12.          | Software Interrupts Can Access the Wrong Handler Address                                                                                                                                                                                                                                                                   |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | Posting a <i>sysctl</i> software interrupt to a vector ending in 0xa while vector caching is enabled causes the processor to begin executing at an undefined address, which usually results in an OPERATION fault. The processor fetches an interrupt handler address from the internal vector cache, where it should not. |

|              | This behavior occurs every time vector caching is enabled and the vector least significant nibble is 0xa, i.e., the set of "bad" vectors is:                                                                                                                                                                               |

|              | 0x0a, 0x1a, 0x2a, 0x3a, 0x4a, 0x5a, 0x6a, 0x7a,                                                                                                                                                                                                                                                                            |

|              | 0x8a, 0x9a, 0xaa, 0xba, 0xca, 0xda, 0xea, 0xfa                                                                                                                                                                                                                                                                             |

|              | This failure does not occur when either of the above conditions is false when vector caching is disabled or another vector besides 0xa is used.                                                                                                                                                                            |

|              | Interrupt vectors ending in 0xa are not cacheable, so the processor should read the external interrupt vector table even though vector caching is enabled. When the failure occurs, the processor doesn't read the handler address from the external interrupt vector table.                                               |

|              | Expanded or mixed hardware interrupts can use these vectors with impunity. For example, vector 0xaa has been shown to work correctly as an expanded hardware interrupt vector.                                                                                                                                             |

| Implication: | Sixteen (16) software interrupt vectors (all vectors ending in 0xa) are unavailable while vector caching is enabled. The remaining 224 software interrupt vectors are unaffected.                                                                                                                                          |

| Workaround:  | Disable interrupt vector caching (ICON.vce = $0$ ) when posting software interrupts to vectors ending in $0xa$ . Otherwise, avoid using vectors ending in $0xa$ .                                                                                                                                                          |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                            |

| 13.          | Invalidating the Data Cache Automatically Re-enables It                                                                                                                                                                                                                                                                    |

| Problem:     | Invalidating the data cache ("D_cache") enables the D_cache.                                                                                                                                                                                                                                                               |

|              | Applications that disable the D_cache then invalidate it result in the D_cache being enabled again. This behavior occurs regardless of whether the software directly writes to the CCON (sf2) or uses the <i>dcctl</i> instruction to manipulate the D_cache.                                                              |

| Implication: | The D_cache can be enabled when users do not expect it.                                                                                                                                                                                                                                                                    |

| Workaround:  | Follow one of the sequences below to invalidate and disable the D_cache:                                                                                                                                                                                                                                                   |

|              | 1. Set CCON.dci = 1 to invalidate the D_cache.                                                                                                                                                                                                                                                                             |

|              | 2. Loop on the CCON.dci bit until it clears.                                                                                                                                                                                                                                                                               |

|              | 3. Set CCON.dcgd = 1 to disable the D_cache.                                                                                                                                                                                                                                                                               |

|              | or                                                                                                                                                                                                                                                                                                                         |

|              | 1. Issue the <i>dcctl</i> instruction, mode 2 to invalidate the D_cache first.                                                                                                                                                                                                                                             |

|              | 2. Issue the <i>dcctl</i> instruction, mode 0 to disable the D_cache.                                                                                                                                                                                                                                                      |

|              | This workaround does not necessarily have to be removed after this errata is corrected in silicon.                                                                                                                                                                                                                         |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                            |

| otatus.      | The area when the building state of changes to determine the area to the suppling(s).                                                                                                                                                                                                                                      |

| 14.          | RESET Has Priority Over HOLD                                                                                                                                                                                                                                                                                                                            |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Problem:     | If the RESET and HOLD pins are both true, the processor output and I/O pins assume the RESET state. The output and I/O pins are supposed to remain in the HOLD state regardless of the RESET pin.                                                                                                                                                       |

| Implication: | Single bus master systems are not affected.                                                                                                                                                                                                                                                                                                             |

|              | Multiple bus master systems that require the 80960Hx processor to remain in HOLD mode during RESET must use the workaround.                                                                                                                                                                                                                             |

| Workaround:  | Prevent the RESET and HOLD pins from being active at the same time.                                                                                                                                                                                                                                                                                     |

|              | If a multiple bus master system uses HOLD independent of the system RESET signal, add external logic to qualify the system RESET signal with the HOLD signal.<br>RESET#sys + HOLD = RESET#proc                                                                                                                                                          |

|              | <ul> <li>where:</li> <li>RESET#sys (active low) system RESET signal from the host or other controlling bus master,</li> <li>HOLD (active high) HOLD signal applied to the processor,</li> <li>RESET#proc (active low) processor RESET pin.</li> </ul>                                                                                                   |

|              | If the latter option is used, ensure that RESET#proc remains asserted for at least 16 bus clock cycles after HOLD goes away to provide enough time to properly reset the processor.                                                                                                                                                                     |

|              | This workaround does not necessarily have to be removed after this errata is corrected in silicon.                                                                                                                                                                                                                                                      |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                         |

| 15.          | Data Cache Global Disable Bit (CCON.dci, sf2) May Take 1 Extra Clock Cycle<br>To Complete                                                                                                                                                                                                                                                               |

| Problem:     | Sometimes the CCON.dci bit stays high one extra clock cycle. The processor randomly appears to take an extra clock cycle to invalidate the data cache. Functionally, the bit still works as specified; it may simply take longer.                                                                                                                       |

|              | A hardware race condition in the processor causes the bit to discharge in 2 clock cycles. Setting this bit is not affected.                                                                                                                                                                                                                             |

| Implication: | Probably no impact. In normal use, user software sets CCON.dci and polls it until it is cleared by the processor, signaling that the invalidation has completed (see Section 4.5.1 in the user's manual, revision -001, dated November 1995). Since most software does not measure the elapse time of those operations, you may not see this condition. |

| Workaround:  | Do not count the number of cycles required to invalidate the data cache. Otherwise, no workaround is required.                                                                                                                                                                                                                                          |

| Status:      | Fixed. Refer to Summary Table of Changes to determine the affected stepping(s).                                                                                                                                                                                                                                                                         |

### 16. Low Temperature Operating Limit Increased to 25°C Problem: At low temperatures (about -5°C), the on-chip PLL clock circuitry has been observed to lose lock

- **oblem:** At low temperatures (about -5°C), the on-chip PLL clock circuitry has been observed to lose lock and oscillate unpredictably on a portion of units tested. When this failure condition occurs, the processor behavior becomes unpredictable.

- Implication: Unpredictable processor behavior.

Workaround: Avoid operating the processor below 25°C case temperatures.

**Status:** Fixed. This limitation was screened during production testing at the factory and fixed on all steppings after the A-0 step. (Refer to Summary Table of Changes to determine the affected stepping(s).)

#### 17. IPND Register Not Cleared Automatically

**Problem:** Sometimes the processor does not automatically clear the Interrupt Pending (IPND) register when servicing a dedicated interrupt. The interrupt itself is still handled correctly. When the failure condition occurs, the interrupt service routine (ISR) keeps executing repeatedly without further interrupt requests until the Interrupt Mask (IMSK) or IPND are cleared.

This failure condition does not appear on every device, and is more pronounced at high  $V_{CC}$  voltages. This behavior has been observed at  $V_{CC}$  as low as 3.33 V.

Implication: Unless corrected, ISRs can be invoked indefinitely by one dedicated interrupt event.

- **Workaround:** Manually clear the IPND register during the dedicated interrupt ISR. Intel recommends all applications that use dedicated interrupts implement this workaround since the failure condition may appear on some but not all devices.

- **Status:** Fixed. This failure condition has been fixed on the A-1 and all subsequent steps. Refer to Summary Table of Changes to determine the affected stepping(s).

#### 18. Cycle Type Bits (CT3:0) Do Not Indicate Some Fault Types

Problem:

Bit CT2 does not go high for certain types of faults.

The table below summarizes the fault conditions when the CT2 bit does and does not work. All cases of each fault subtype are implied to either work correctly or not unless otherwise noted.

The table below summarizes fault conditions when the CT2 bit does and does not work.

| AULT TYPE     | CT2 BIT WORKS FOR                                                                                         |                                                                                                                                     |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0H Parallel   | PARALLEL                                                                                                  |                                                                                                                                     |  |  |  |

|               | INSTRUCTION                                                                                               | PRERETURN                                                                                                                           |  |  |  |

|               | BRANCH                                                                                                    |                                                                                                                                     |  |  |  |

|               | CALL                                                                                                      |                                                                                                                                     |  |  |  |

| 1H Trace      | RETURN                                                                                                    |                                                                                                                                     |  |  |  |

| III IIdee     | SUPERVISOR                                                                                                |                                                                                                                                     |  |  |  |

|               | MARK/BREAKPOINT                                                                                           | MARK/BREAKPOINT                                                                                                                     |  |  |  |

|               | breakpoint always works correctly, mark when                                                              | mark when Mark Trace Mode is set in the TC                                                                                          |  |  |  |

|               | Mark Trace Mode is not set in the TC register.                                                            | register, fmark.                                                                                                                    |  |  |  |

|               | INVALID_OPCODE                                                                                            |                                                                                                                                     |  |  |  |

|               | UNIMPLEMENTED                                                                                             | UNIMPLEMENTED                                                                                                                       |  |  |  |

|               |                                                                                                           | <i>sysctl</i> message type 04H                                                                                                      |  |  |  |

| 2H Operation  | UNALIGNED                                                                                                 |                                                                                                                                     |  |  |  |

|               | INVALID_OPERAND                                                                                           | INVALID_OPERAND                                                                                                                     |  |  |  |

|               | non-existent <i>sfr</i> , unaligned long-, triple-, or quad-register, undefined register, writing to RIP. | undefined sysctl, icctl, dcctl, or intctl operand.                                                                                  |  |  |  |

|               | INTEGER OVERFLOW                                                                                          | INTEGER OVERFLOW                                                                                                                    |  |  |  |

| 3H Arithmetic |                                                                                                           | integer divide overflow ( <i>divi</i> )                                                                                             |  |  |  |

|               | ZERO DIVIDE                                                                                               |                                                                                                                                     |  |  |  |

|               | RANGE                                                                                                     | RANGE                                                                                                                               |  |  |  |

| 5H Constraint | all other cases.                                                                                          | only if a <i>fault<cc></cc></i> test evaluates true.                                                                                |  |  |  |