# 80960 QUICK val Quick Reference Card

#### Where Do I Start?

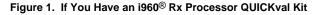

All chapter references refer to "Getting Started with the 80960 QUICKval Kit."

See "For i960 Rx Processor Developers: Which Strategy Do You Use?" on Page 4 for more information.

Figure 2. If You Have an i960 Hx, Jx, Cx, Sx Processor QUICKval Kit

All chapter references refer to "Getting Started with the 80960 QUICKval Kit."

# For i960<sup>®</sup> Rx Processor Developers: Which Strategy Should You Use?

When writing software for the i960 RP/RD processors, you have two choices for the architecture setting that you use when generating code. You can specify the Rx architecture ("Rx Strategy"), or you can specify the i960 JF architecture ("Jx Strategy"). Use these questions to help you decide which of the two development paths you should follow:

- How important is forward-compatibility with future I960 processors? Use the Rx Strategy if you wish to minimize the effort involved in moving to future i960 Rx processors.

- Will you be writing your code from scratch? When writing new applications, follow the Rx Strategy when possible. Tests have shown that there is seldom a significant performance or code size penalty.

- How important is backward-compatibility with other I960 core processors (e.g., Kx, Cx, Jx)? If you have legacy code that you wish to use with the I960 Rx processors, you may wish to use the Jx Strategy. This gives the most flexibility in terms of available instructions and addressing modes.

- How much low-level processor access do you need? If you need access to low-level processor resources beyond that provided in the updated assembler pseudo-instructions, you must use the Jx Strategy.

#### Writing Assembly with the Rx Strategy

- Use -ARx (e.g., -ARP) switch to get CTOOLS Rx Strategy enhancements.

- If migrating code written for other I960 core processors, use the xlate960 utility as a starting point.

xlate960: generates i960 Rx Strategy compatible code to replace instructions and addressing modes that appear in the i960 JF processor only.

If you need to use some i960 JF processor specific features not supported in the Rx Strategy, use the new assembler pseudoinstructions whenever possible. The assembler pseudo instructions provide an architecture-independent method of performing some of the more common low-level processing operations.

Benefit: The pseudo-instructions should not require modification when the source code is re-assembled for future i960 Rx processors.

#### Writing Assembly without the Rx Strategy

- Use -AJF switch to write code that is designed for the I960 JFbased Rx (e.g., RP, RD) processors only. You can still simplify future migration efforts by staying within the boundaries of the Rx Strategy whenever possible.

- For low-level processor functionality, you may wish to use the new assembler pseudo-instructions. This eases future migration without excluding use of Jx-Specific constructs.

Please refer to the *i960 Processor Assembler User's Guide* for more information.

#### QUICKreference Contact Guide

#### Important Phone Numbers:

Technical Support Group

1-800-628-8686

Intel Literature Center

1-800-548-4725

**FaxBACK**

1-800-628-2283 or 916-356-3105

Document #-\_\_\_\_

Press '2' for Development Tools

Press '3' for Catalog

Intel Bulletin Board

1-916-356-3600

### Important E-Mail Addresses:

80960 Technical Support Group

960tools@intel.com

#### Important Internet Sites:

Embedded Design Products

http://developer.intel.com/design/product.htm

Technical Support Page

http://developer.intel.com/design/i960/swsup/

i960 Processor Software Tools Patches Page

http://developer.intel.com/design/i960/patches/

Electronic Benchmark Facility

http://developer.intel.com/design/i960/testcntr/

## **QUICKval Example Programs**

| Description                                                                                                                                                                                                                                                                    | Source Files Needed                                                                                                                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Hello World:</b> Uses simple printf statement to verify system integrity.                                                                                                                                                                                                   | hello.c: source file system.c: system file                                                                                                                                             |

| <b>Memory Test:</b> Used for system verification of external memory. The programs perform byte, short, or word writes to external memory, and then they check the addresses written for correctness.                                                                           | memtst8.c: 8 bit<br>memory test<br>memtst16.c: 16 bit<br>memory test<br>memtst32.c: 32 bit<br>memory test<br>system.c: system file                                                     |

| Data Cache: Uses the Minimum Edit Distance Algorithm to demonstrate the effectiveness of the on-chip data cache. This example also shows how to enable and disable the data cache; furthermore, it demonstrates how to configure an area of memory for caching.                | dcache.c: source file system.c: system file                                                                                                                                            |

| Instruction Cache: Uses simple loop to demonstrate how to enable and disable the instruction cache. It also highlights the performance advantage obtained when using the on-chip instruction cache.                                                                            | loop.c: source file system.c: system file                                                                                                                                              |

| External Interrupts: Shows how to configure the Cyclone board timers to trigger hardware interrupts. This is also an example of using interrupt handlers and placing the handlers in the interrupt table.                                                                      | cyint.c: source file<br>asm_fns.s: interrupt<br>handler-SX<br>int_proc.s: interrupt<br>handler-all<br>processors but SX<br>t85c36.c: eval board<br>timer file system.c:<br>system file |

| Internal Interrupts: Simple timer example that is used to show how to overlay the memory mapped registers with a structure to program the on-chip timers. It also includes routines to instruct you on how to set up interrupt routines using the timers.                      | timrcntr.c: source file<br>timers.c: on-chip timer<br>file<br>system.c: system file                                                                                                    |

| Halt Mode: This program shows how to make the processor enter halt mode, a power saving state that reduces energy consumption and heat dissipation as it waits to continue code execution. The example uses the on-chip timers to trigger interrupts and "wake" the processor. | halt.c: source file<br>incremen.s: interrupt<br>handler<br>system.c: system file                                                                                                       |

| Fault Handling: Shows the steps taken in setting up the fault handling procedures in the fault and system procedure tables. The faults shown are: arithmetic, constraint, operation, protection, parallel, & type.                                                             | fault.c: source file flt_proc.c: fault procedures asm_flt.s: assembly functions to help generate faults system.c: system file                                                          |

| Processors          | Compile Line                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Supported           | <arch> = RD, RP, HD, JF, CF, or SA</arch>                                                                                                    |

| ALL                 | gcc960 -Fcoff -A <arch> -c hello.c system.c</arch>                                                                                           |

| ALL                 | gcc960 -Fcoff -A <arch> -c memtst*.c system.c</arch>                                                                                         |

|                     | NOTE: * refers to 8, 16, or 32.                                                                                                              |

| Rx, Hx, Jx,<br>& Cx | gcc960 -Fcoff -A <arch> -c dcache.c system.c</arch>                                                                                          |

| Rx, Hx, Jx,<br>& Cx | gcc960 -Fcoff -A <arch> -c loop.c system.c</arch>                                                                                            |

| Hx, Jx, Sx,<br>Cx   | Sx: gcc960 -Fcoff -ASA -c cyint.c asm_fns.s t85c36.c system.c  Other: gcc960 -Fcoff -A <arch> -c cyint.c int_proc.s t85c36.c system.c</arch> |

| Hx & Jx             | gcc960 -Fcoff -A <arch> -c<br/>timrcntr.c timers.c system.c</arch>                                                                           |

| Jx                  | gcc960 -Fcoff -A <arch> -c<br/>halt.c incremen.s system.c</arch>                                                                             |

| Hx, Jx, & Cx        | gcc960 -Fcoff -A <arch> -c fault.c flt_proc.c asm_flt.s system.c</arch>                                                                      |

| · · ·                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Register Cache:</b> Demonstrates the use of the on-chip register cache in reducing the interrupt latency for high priority interrupts.                                                                                                                                                                                                                 | reg_int.c: source file<br>low_int.s: interrupt<br>handler for low priority<br>high_int.s: interrupt<br>handler for high<br>priority<br>system.c: system file |

| CheckSum: Uses typical checksum routine to show how to add benchmarking routines into source code. It is then used to show you the performance advantage of optimizing compilers and two-pass compilations.                                                                                                                                               | chksum.c: source file system.c: system file                                                                                                                  |

| DMA (i960 Cx): Provides an example of programming the DMA controller of the 80960 CX microprocessor. This example is setup for block mode chaining transfer.                                                                                                                                                                                              | dma.c: source file int_rout.c: DMA interrupt handling routine sdma.s: will configure DMA channel 0 and provide chained linked buffers. system.c: system file |

| DMA (i960 Rx) Tutorial: Demonstrates how to set-up the DMA controller, the Primary Address Translation Unit (ATU), the Secondary ATU, and the PCI-To-PCI Bridge Unit.                                                                                                                                                                                     | rpdma.c: source file                                                                                                                                         |

| <b>Messaging Unit Tutorial:</b> Demonstrates the messaging unit of the i960 Rx processor                                                                                                                                                                                                                                                                  | hostcode.c: source file rp_code.c: source file                                                                                                               |

| Cave Tutorial: Uses a tic tac toe game to show how to reduce target memory requirements. The text sections of compressed and uncompressed tic tac toe executables are compared. Additionally, this example demonstrates how to specify functions for compression.                                                                                         | ttt.c: source file                                                                                                                                           |

| <b>Profiling Lab:</b> Teaches you how to use some of CTOOLS advanced profiling features.                                                                                                                                                                                                                                                                  | chksum.c: Source file                                                                                                                                        |

| Self-Contained Profile Tutorial: Teaches you how to create a self-contained profile that captures the program structure and associates it with the program counters from a raw profile. When the source program changes, the global decision making step interpolates or stretches the counters in the self-contained profile to fit the changed program. | quick.c: Source file                                                                                                                                         |

|         | Example i rograms (continued)                                             |

|---------|---------------------------------------------------------------------------|

| Hx & Jx | gcc960 -Fcoff -A <arch> -c reg_int.c low_int.s high_int.s system.c</arch> |

| ALL     | gcc960 -Fcoff -A <arch> -O* -c chksum.c system.c</arch>                   |

|         | NOTE:  * refers to [0-4] depending on the level of static optimization.   |

| Cx ONLY | gcc960 -Fcoff -ACF -c dma.c int_rout.c sdma.s system.c                    |

| Rx ONLY | NA                                                                        |

| Rx ONLY | NA                                                                        |

| ALL     | NA                                                                        |

| ALL     | NA                                                                        |

| ALL     | NA                                                                        |

| - Colorital Example : 10g.ame (ee.                                                                                                                                                                                                                       | ,                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| Incremental Profiling Tutorial: Teaches you how to profile a program in pieces and then re-combine them later, a useful methodology when the target execution environment is memory limited.                                                             | fault.c flt_proc.c asm_flt.s system.c: Source files |

| <b>Local Optimizations:</b> Shows how to use the C compiler with high levels of static optimization for improved runtime performance.                                                                                                                    | chksum.c system.c:<br>Source files                  |

| <b>Global Optimizations:</b> Shows how to use program-wide optimizations of the C compiler for increased performance.                                                                                                                                    | chksum.c system.c:<br>Source files                  |

| <i>C++ Local Optimizations:</i> Shows how to use the C++ compiler with high levels of static optimization for improved runtime performance.                                                                                                              | optimize.cpp: Source file                           |

| <b>C++ Global Optimizations:</b> Shows how to use program-wide optimizations of the C++ compiler for increased performance.                                                                                                                              | optimize.cpp: Source file                           |

| C++ Virtual Function Optimizations: In many situations, a call to a virtual function can be replaced by a direct call to a member function, and, if possible, it may be inlined at the call site. This improves the runtime performance of the code.     | optimize.cpp: Source file                           |

| C++ Cave Tutorial: Uses a C++ program to show how to reduce target memory requirements. The text sections of compressed and uncompressed C++ executables are compared. Additionally, this example demonstrates how to specify functions for compression. | cavecpp.cpp: Source file                            |

| xlate960 Assembly Language Converter Tutorial: Shows you how you can use xlate960 to convert assembly language code written for one i960 processor family member to that of another.                                                                     | xlt.s: Source file                                  |

| i960 Processor Assembler Pseudo-<br>Instruction Support Tutorial: A tutorial that shows you how to use the new pseudo-ops that have been added to the assembler.                                                                                         | pseudop.c: Source file                              |

| <b>Linker Directive Language:</b> A hyperlinked manual that describes the linker command options.                                                                                                                                                        |                                                     |

| QUIUITVAI           | Example i rograms (continuca) |

|---------------------|-------------------------------|

| Hx, Jx, & Cx        | NA                            |

|                     |                               |

| ALL                 | NA                            |

| Rx, Jx              | NA                            |

| Rx, Hx, Jx,<br>& Cx | NA                            |

| ALL                 | NA                            |

| QUICKVai Example Programs (COI                                                                                                                                       | illiueu)                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Linker Consumption Tutorial: Shows the ability of the linker, gld960, to consume b.out-format, COFF, or ELF object files and libraries in any combination.           | cyint.c int_proc.s<br>t85c36.c system.c:<br>Source files |

| <b>Debugging with gdb960 Tutorial:</b> Uses the Go Fish card game to teach a few useful debugger commands.                                                           | fish.c: source file system.c: system file                |

| ELF/DWARF Debugging Format Tutorial: Demonstrates that at the highest level of module-local optimization, it is possible to set a breakpoint on an in-line function. | swap.c: Source file                                      |

| C++ DWARF-2 Debugging Format Tutorial: Demonstrates that at the highest level of module-local optimization, it is possible to debug a C++ application.               | cppdwarf.cpp: Source file                                |

| Retargeting MON960: The Retargeting MON960 chapter is hyperlinked for your convenience.                                                                              |                                                          |

| Writing Flash Tutorial: Demonstrates how to update the version of MON960 on your evaluation board.                                                                   |                                                          |

| i960 Rx Processor Initialization Code:<br>Shows the Memory Controller, System Init,<br>and Hardware Init Code.                                                       |                                                          |

| 80960 Family Benchmark: Used to compare your processor's performance with other i960 family members.                                                                 | chksum.c system.c:<br>Source files                       |

| <b>Remote Evaluation Facility:</b> Guides you through the use of this new benchmarking facility on the World-Wide Web.                                               |                                                          |

| QUICKVai          | Example Frograms (continued)                          |

|-------------------|-------------------------------------------------------|

| Hx, Jx, & Cx      | NA                                                    |

| ALL               | gcc960 -Fcoff -A <arch> -c<br/>fish.c system.c</arch> |

| ALL               | NA                                                    |

| RP                | NA                                                    |

| Hx, Jx, Cx,<br>Sx | NA                                                    |

| Hx, Jx, Cx,<br>Sx | NA                                                    |

### i960 Cx, Jx, Hx Processor Features Summary

| Feature                               | 80960Cx                                                                        | 80960Jx                                                                                                    | 80960Hx                                                                        |

|---------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| Core                                  | Superscalar<br>(maximum 3<br>inst/clk)                                         | Scalar,clock<br>doubled, clock<br>tripled                                                                  | Superscalar<br>(max 3<br>inst/clk), clock<br>doubled, clock<br>tripled         |

| External Bus                          | 32-bit demulti-<br>plexed address<br>and data                                  | 32-bit<br>multiplexed<br>address/data                                                                      | 32-bit demulti-<br>plexed address<br>and data,<br>parity on data               |

| Instruction<br>Cache                  | CA:<br>1 Kbyte,<br>2-way<br>CF:<br>4 Kbyte,<br>2-way                           | JA/JF/JD:<br>4 Kbytes,<br>2-way<br>JT:<br>16 Kbytes,<br>2-way                                              | 16 Kbytes,<br>4-way                                                            |

| Data Cache                            | CA: None<br>CF: 1Kbyte,<br>direct map,<br>write-through                        | JA/JF/JD:<br>2 Kbytes, direct<br>map, write-<br>through<br>JT:<br>4 Kbytes<br>direct map,<br>write-through | 8 Kbytes,<br>4-way, write-<br>through                                          |

| Data RAM                              | 1 Kbyte,<br>mapped from<br>000H to 3FFH                                        | 1 Kbyte,<br>mapped from<br>000H to 3FFH                                                                    | 2 Kbytes,<br>mapped from<br>000H to 7FFH                                       |

| Register Cache                        | 5 frames,<br>programmable<br>to 15 frames<br>(more than 5<br>used Data<br>RAM) | 8 frames                                                                                                   | 5 frames,<br>programmable<br>to 15 frames<br>(more than 5<br>uses Data<br>RAM) |

| Memory-<br>mapped<br>Registers        | No                                                                             | Yes                                                                                                        | Yes                                                                            |

| Direct Memory Access (DMA) Controller | Yes                                                                            | No                                                                                                         | No                                                                             |

| Interrupt<br>Controller               | Yes                                                                            | Yes                                                                                                        | Yes                                                                            |

| Guarded<br>Memory Unit                | No                                                                             | No                                                                                                         | Yes                                                                            |

| Timers                                | None                                                                           | Two                                                                                                        | Two                                                                            |

| Power Supply                          | 5V                                                                             | 5V, 3.3V, or<br>3.3V with 5V<br>tolerant                                                                   | 3.3V, 5V<br>tolerant                                                           |

| JTAG                                  | No                                                                             | Yes                                                                                                        | Yes                                                                            |

### i960 Rx Processor Features Summary

| Frequencies               | • 33 MHz, 3.3 Volt Version (80960RP 33/3.3)                                                  |

|---------------------------|----------------------------------------------------------------------------------------------|

| Supported                 | 66 MHz, 3.3 Volt Version (80960RD 66/3.3)     Clock Doubled 80960JF Core                     |

|                           | - Clock Doubled 80980JF Cole                                                                 |

| Compatibility             | Complies with PCI Local Bus Specification<br>Revision 2.1                                    |

| High Performance          | Sustained One Instruction/Clock Execution                                                    |

| 80960Jx Core              | 4 Kbyte Two-Way Set-Associative<br>Instruction Cache                                         |

|                           | 2 Kbyte Direct-Mapped Data Cache                                                             |

|                           | Sixteen 32-Bit Global Registers                                                              |

|                           | Sixteen 32-Bit Local Registers                                                               |

|                           | <ul><li>Programmable Bus Widths:</li><li>8-, 16-, 32-Bit</li></ul>                           |

|                           | 1 Kbyte Internal Data RAM                                                                    |

|                           | <ul> <li>Local Register Cache<br/>(Eight Available Stack Frames)</li> </ul>                  |

|                           | Two 32-Bit On-Chip Timer Units                                                               |

| PCI-to-PCI Bridge<br>Unit | Primary and Secondary PCI Interfaces                                                         |

|                           | Two 64-Byte Posting Buffers                                                                  |

|                           | Delayed and Posted Transaction Support                                                       |

|                           | <ul> <li>Forwards Memory, I/O, Configuration<br/>Commands from PCI Bus to PCI Bus</li> </ul> |

| Two Address               | Connects Local Bus to PCI Buses                                                              |

| Translation Units         | <ul> <li>Inbound/Outbound Address Translation<br/>Support</li> </ul>                         |

|                           | Direct Outbound Addressing Support                                                           |

| Messaging Unit            | Four Message Registers                                                                       |

|                           | Two Doorbell Registers                                                                       |

|                           | Four Circular Queues                                                                         |

|                           | 1004 Index Registers                                                                         |

| Memory Controller         | 256 Mbytes of 32- or 36-Bit DRAM                                                             |

|                           | Interleaved or Non-Interleaved DRAM                                                          |

|                           | Fast Page-Mode DRAM Support                                                                  |

|                           | Extended Data Out and Burst                                                                  |

|                           | Extended Data Out DRAM Support                                                               |

|                           | Two Independent Banks for SRAM / ROM /<br>Flash (16 Mbytes/Bank; 8- or 32-Bit)               |

|                           |                                                                                              |

## i960 Rx Processor Features Summary (continued)

| DMA Controller                 | Three Independent Channels                                                                                  |

|--------------------------------|-------------------------------------------------------------------------------------------------------------|

|                                | PCI Memory Controller Interface                                                                             |

|                                | 32-Bit Local Bus Addressing                                                                                 |

|                                | 64-Bit PCI Bus Addressing                                                                                   |

|                                | Independent Interface to Primary and<br>Secondary PCI Buses                                                 |

|                                | 132Mbyte/sec Burst Transfers to PCI and<br>Local Buses                                                      |

|                                | Direct Addressing to and from PCI Buses                                                                     |

|                                | Unaligned Transfers Supported in<br>Hardware                                                                |

|                                | Two Channels Dedicated to Primary PCI Bus                                                                   |

|                                | One Channel Dedicated to Secondary PCI Bus                                                                  |

| I/O APIC Bus<br>Interface Unit | Multiprocessor Interrupt Management for<br>Intel Architecture CPUs (Pentium® and<br>Pentium Pro Processors) |

|                                | Dynamic Interrupt Distribution                                                                              |

|                                | Multiple I/O Subsystem Support                                                                              |

| I2C Bus Interface              | Serial Bus                                                                                                  |

| Unit                           | Master/Slave Capabilities                                                                                   |

|                                | System Management Functions                                                                                 |

| Secondary PCI                  | Supports Six Secondary PCI Devices                                                                          |

| Arbitration Unit               | Multi-priority Arbitration Algorithm                                                                        |

|                                | External Arbitration Support Mode                                                                           |

| Private PCI                    | SuperBGA* Package                                                                                           |

| Device Support                 | 352Ball-Grid Array (HL-PBGA)                                                                                |