# i960® Processor Assembler User's Guide

Order Number: 485276-006

| Revision | Revision History                                   | Date  |

|----------|----------------------------------------------------|-------|

| -001     | Original Issue.                                    | 12/92 |

| -002     | Minor corrections.                                 | 09/93 |

| -003     | Revised for CTOOLS960 R4.5 and GNU/960 Tools R2.4. | 05/94 |

| -004     | Revised for Release 5.0.                           | 02/96 |

| -005     | Revised for Release 5.1.                           | 01/97 |

| -006     | Revised for Release 6.0.                           | 12/97 |

In the United States, additional copies of this manual or other Intel literature may be obtained by writing:

Literature Distribution Center Intel Corporation PO Box 5937 Denver, CO 80217-9808

Or you can call the following toll-free number:

1-800-548-4725

In locations outside the United States, obtain additional copies of Intel documentation by contacting your local Intel sales office.

Information in this document is provided in connection with Intel products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's Software License Agreement, or in the case of software delivered to the government, in accordance with the software license agreement as defined in FAR 52.227-7013.

Copyright a 1988, 1989, 1990, 1991, 1992, 1993, 1994, 1995 Free Software Foundation, Inc.

Permission is granted to make and distribute verbatim copies of this manual provided the copyright notice and this permission notice are preserved on all copies.

Permission is granted to copy and distribute modified versions of this manual under the conditions for verbatim copying, provided also that the entire resulting derived work is distributed under the terms of a permission notice identical to this one.

Permission is granted to copy and distribute translations of this manual into another language, under the above conditions for modified versions.

\* Other brands and names are the property of their respective owners.

Copyright © 1992 - 1994, 1996, 1997. Intel Corporation. All rights reserved.

# **Contents**

| Chapter 1 | Overview                                      |     |

|-----------|-----------------------------------------------|-----|

|           | What's New in the Assembler for CTOOLS 6.0    | 1-1 |

|           | i960® Processor Assembler and Related Tools   | 1-1 |

|           | Compatibility and Standards                   | 1-2 |

|           | About This Manual                             | 1-3 |

|           | Target Audience                               | 1-3 |

|           | Conventions                                   | 1-3 |

|           | Customer Service                              | 1-5 |

| Chapter 2 | Writing Assembly Language Code                |     |

| •         | for the i960 Rx Processor                     |     |

|           | Introduction                                  | 2-1 |

|           | What is the "Rx Strategy?"                    | 2-1 |

|           | How Do I Use the Rx Strategy?                 | 2-1 |

|           | How Do I Use the Jx-Specific Strategy?        | 2-2 |

|           | How Do I Decide Which Strategy to Use?        | 2-2 |

|           | Writing Assembly Code With the Rx Strategy    | 2-3 |

|           | Writing Assembly Code Without the Rx Strategy | 2-4 |

|           | Details of the Rx Strategy                    | 2-4 |

|           | 80960 Instruction Set Support                 | 2-4 |

|           | Big-Endian Support                            | 2-7 |

|           | b.out OMF Support                             | 2-7 |

|           | 80960 Assembly Language Converter (xlate960)  | 2-8 |

|           | Improved Assembler Pseudo-instruction Support | 2-8 |

|           | Introduction                                  | 2-8 |

| Chapter 3 | Invoking the Assembler                       |      |

|-----------|----------------------------------------------|------|

|           | Invocation Command                           | 3-1  |

|           | Specifying Option Arguments                  | 3-2  |

|           | Specifying Single and Multiple Options       | 3-2  |

|           | Using Uppercase and Lowercase                | 3-3  |

|           | Naming the Object File                       | 3-4  |

|           | Providing Source Input                       | 3-5  |

|           | Environment Variables                        | 3-6  |

|           | Selecting the Instruction Set and Libraries  | 3-7  |

|           | Defining a Base Directory Path               | 3-8  |

|           | Defining an Identification String            | 3-8  |

|           | Redirecting Error and Warning Message Output | 3-8  |

|           | Building a Search Path for Include Files     | 3-8  |

|           | Building the Search Path for the Assembler   |      |

|           | Executable                                   | 3-9  |

| Chapter 4 | Option Reference                             |      |

|           | A: Architecture                              | 4-3  |

|           | D: Define symbol                             | 4-4  |

|           | d: Debug symbols                             | 4-6  |

|           | G: Big-endian target                         | 4-7  |

|           | I: Include-file search path                  | 4-8  |

|           | i: Input from stdin                          | 4-9  |

|           | L: Generate a listing                        | 4-10 |

|           | n: No compare-and-branch replacement         | 4-16 |

|           | o: Object filename                           | 4-17 |

|           | p: Position independence                     | 4-18 |

|           | t: Translate                                 | 4-19 |

|           | V, v960: Version                             | 4-20 |

|           | W: Warnings                                  | 4-21 |

|           | x: Allow mixed architectures                     | 4-21 |

|-----------|--------------------------------------------------|------|

|           | z: Time stamp                                    | 4-23 |

| Chapter 5 | Directives                                       |      |

| -         | Syntax                                           | 5-2  |

|           | Specifying the Input                             | 5-3  |

|           | Controlling the Location Counter                 | 5-3  |

|           | Setting the Location Counter to a Specific Value | 5-3  |

|           | Moving the Location Counter to a Section         | 5-4  |

|           | Initializing Data                                | 5-5  |

|           | Initializing Byte, Ordinal, and Integer Data     | 5-6  |

|           | Initializing Floating-point Data                 | 5-6  |

|           | Initializing String Data                         | 5-6  |

|           | Initializing Blocks of Memory                    | 5-7  |

|           | Defining Symbols                                 | 5-7  |

|           | Providing Debugger Information                   | 5-8  |

|           | Optimizing                                       | 5-9  |

|           | Marking Position Independence                    | 5-10 |

|           | Controlling the Listing                          | 5-10 |

|           | Directives Reference                             | 5-10 |

| Chapter 6 | Messages                                         |      |

| Chapter 7 | Assembly Language                                |      |

|           | Assembly Language Statement Format               | 7-1  |

|           | Character Set                                    | 7-2  |

|           | Tokens and Separators                            | 7-3  |

|           | Identifiers                                      | 7-3  |

|           | Constants                                        | 7-3  |

|           | Simple Constants                                 | 7-3  |

|           | Representing Floating-Point Numbers              | 7-4  |

|           | Character Constants                              | 7-5  |

|           | String Constants                                 | 7-6  |

| Labels                             | 7-6  |

|------------------------------------|------|

| Name (Global) Labels               | 7-7  |

| Numeric (Local) Labels             | 7-7  |

| Expressions                        | 7-7  |

| Operators                          | 7-8  |

| Expression Types                   | 7-10 |

| Type Propagation in Expressions    | 7-13 |

| Comments                           | 7-14 |

| Summary of Core Instructions       | 7-15 |

| Data Movement                      | 7-15 |

| Load                               | 7-16 |

| Store                              | 7-16 |

| Move                               | 7-17 |

| Select                             | 7-17 |

| Ordinal and Integer Arithmetic     | 7-18 |

| Basic Arithmetic                   | 7-18 |

| Extended Arithmetic                | 7-19 |

| Conditional Arithmetic             | 7-19 |

| Remainder and Modulo               | 7-21 |

| Shift and Rotate                   |      |

| Logical                            | 7-22 |

| Bit, Bit Field, Byte               | 7-24 |

| Bit Operations                     |      |

| Bit Field Operations               | 7-25 |

| Byte Operations                    | 7-25 |

| Comparison                         |      |

| Compare and Conditional Compare    | 7-26 |

| Compare and Increment or Decrement |      |

|           | Branch                                   | 7-27 |

|-----------|------------------------------------------|------|

|           | Unconditional Branch                     | 7-28 |

|           | Conditional Branch                       | 7-28 |

|           | Compare and Branch                       | 7-29 |

|           | Call and Return                          | 7-30 |

|           | Fault                                    | 7-31 |

|           | Debug                                    | 7-32 |

|           | Processor Management                     | 7-32 |

|           | Synchronous (K-series only)              | 7-34 |

|           | Atomic                                   | 7-35 |

|           | Summary of On-chip Numerics Instructions | 7-35 |

|           | Data Movment                             | 7-35 |

|           | Sign Copying                             | 7-37 |

|           | Data Type Conversion                     | 7-37 |

|           | Basic Arithmetic                         | 7-38 |

|           | Decimal                                  | 7-39 |

|           | Comparison and Classification            | 7-40 |

|           | Trigonometric Functions                  | 7-41 |

|           | Logarithmic, Exponential, and Scale      | 7-42 |

| Chapter 8 | Pseudo-instructions                      |      |

|           | Syntax                                   | 8-1  |

|           | Branch Pseudo-instructions               | 8-2  |

|           | Migration-enabling Pseudo-instructions   | 8-2  |

|           | Conditional Faults Pseudo-instructions   | 8-4  |

|           | Load Pseudo-instructions                 | 8-4  |

|           | Call Pseudo-instructions                 | 8-4  |

|           | Compare-and-jump Pseudo-instructions     | 8-4  |

|           | Pseudo-instructions Reference            | 8-7  |

| Chapter 9 | Exa                                     | mple Programs                                        |   |  |  |  |  |

|-----------|-----------------------------------------|------------------------------------------------------|---|--|--|--|--|

|           | Exar                                    | mples Using the Core Instruction Set9-1              |   |  |  |  |  |

|           | Е                                       | nable and Count Interrupts From 8259A9-2             |   |  |  |  |  |

|           | S                                       | end an IAC to the Processor9-8                       |   |  |  |  |  |

|           | Р                                       | erform a BitBlt Operation9-9                         |   |  |  |  |  |

|           | Р                                       | erform Matrix Multiplication9-1                      | 1 |  |  |  |  |

|           | С                                       | ompare Strings9-1                                    | 3 |  |  |  |  |

|           | Exar                                    | mples Using Floating-point Instructions9-1           | 4 |  |  |  |  |

|           | О                                       | ptimize a Numerics Application9-1                    | 4 |  |  |  |  |

|           | Р                                       | erform Matrix Multiplication9-10                     | 3 |  |  |  |  |

|           |                                         | Assembly Code9-1                                     | 6 |  |  |  |  |

|           |                                         | C Code                                               | 8 |  |  |  |  |

|           | Perform Basic Numerics Operations       |                                                      |   |  |  |  |  |

|           | Exponentiate With an Arbitrary Exponent |                                                      |   |  |  |  |  |

|           | С                                       | onvert Between Coordinate Systems9-2                 | 0 |  |  |  |  |

|           |                                         | etrieve Fault Record Pointer 9-2                     |   |  |  |  |  |

| Glossary  |                                         |                                                      |   |  |  |  |  |

| Index     |                                         |                                                      |   |  |  |  |  |

| Examples  |                                         |                                                      |   |  |  |  |  |

|           | 7-1                                     | Example of Constants and Literal Values7-5           |   |  |  |  |  |

|           | 7-2                                     | Forward-reference External Symbol in Expressions 7-8 |   |  |  |  |  |

|           | 7-3                                     | Example of Register Usage7-1                         | 3 |  |  |  |  |

| Figures   |                                         |                                                      |   |  |  |  |  |

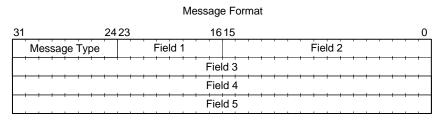

|           | 9-1                                     | IAC Message Structure 9-8                            |   |  |  |  |  |

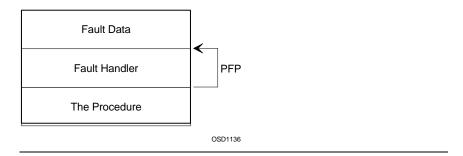

|           | 9-2                                     | Stack For Fault Handler9-2                           | 1 |  |  |  |  |

# **Tables**

| 2-1  | New Assembler Pseudo-Ops                    | 2-9    |

|------|---------------------------------------------|--------|

| 3-1  | Assembler Environment Variables             | . 3-7  |

| 4-1  | Assembler Options                           | 4-1    |

| 4-2  | CORE0-3 Architecture Compatibilities        | 4-4    |

| 5-1  | Functions Performed by Directives           | . 5-1  |

| 7-1  | Assembly Language Character Set             | 7-2    |

| 7-2  | Prefixes for Floating-point Constants       | . 7-4  |

| 7-3  | Floating-point Literals                     | 7-5    |

| 7-4  | Character Constants                         | 7-6    |

| 7-5  | Expression Operators                        | 7-9    |

| 7-6  | Operator Precedence                         | 7-9    |

| 7-7  | Predefined Register Symbols                 | 7-12   |

| 7-8  | Unary Operation                             | . 7-23 |

| 7-9  | Binary Operations                           | 7-23   |

| 7-10 | Binary Operations Continued                 | . 7-23 |

| 7-11 | Supported Processor Management Instructions | . 7-33 |

| 8-1  | Branch Real Pseudo-instructions             | 8-2    |

| 8-2  | New Assembler Pseudo-Instructions           | . 8-3  |

| 8-3  | Compare-and-jump Pseudo-instructions        | . 8-6  |

| 8-4  | Breakpoint Resource Status Word Bits        | . 8-10 |

| 8-7  | Compare and Jump Substitutions              | . 8-18 |

| 8-8  | Data Cache Status Word Bits                 | 8-20   |

| 8-9  | Instruction Cache Status Word Bits          | 8-24   |

Overview

This chapter of the *i960*<sup>®</sup> *Processor Assembler User's Guide* introduces you to the i960 processor assembler and to this manual.

This chapter describes:

- new features in the assembler

- using the assembler with other i960 processor software tools

- the standards and conventions used by the assembler and in this manual

- the trademarks and copyrights pertaining to this manual

#### What's New in the Assembler for CTOOLS 6.0

This release features enhanced support for developing assembly language code for the Intel i960 Rx processor. This includes:

- Writing assembly language code for the i960 Rx processor.

- xlate960, 80960 assembly language translator

- Improved pseudo-instruction support for gas960/asm960

See Chapter 2 for information on these topics.

#### i960® Processor Assembler and Related Tools

The i960 processor assembler is part of a complete set of software and hardware tools for developing embedded applications for the i960 processors. Use ic960 or gcc960, the i960 processor assembler, and the i960 processor software utilities to translate, link, and format source text into executable or PROM-programmable code. You can write assembly source text directly in a text editor or compile a C/C++ program to produce assembly output. To create object files, you can assemble your source text

or the assembly output from the C/C++ compiler. Disassembled text from the dumper is for debugging only and cannot be reassembled. For more information on how the software tools work together, see the Getting Started manual.

## **Compatibility and Standards**

The assembler described in this manual supports the i960 Sx, Kx, Cx, Jx, Hx, and Rx processors.

The assembler accepts output from Release 3.0 and later of the CTOOLS960 compiler and from Release 1.2 and later of the GNU/960 compiler.

You can specify the assembler object file output format as either common object file format (COFF), b.out or ELF format. The output format depends on the assembler invocation command, as shown:

- For b.out format, invoke the assembler with the gas960 command.

- For COFF format, invoke the assembler with the gas960c or asm960 command.

- For ELF format, invoke the assembler with the gas960e command.

For backwards compatibility with your existing script or batch files, the directory structures and search paths used by the assembler depend on the invocation name, as shown:

- For behavior similar to the GNU/960 (Release 1.2 or later) assembler, invoke the assembler with gas960, gas960c, or gas960e.

- For behavior similar to the CTOOLS960 (Release 3.5) assembler, invoke the assembler with asm960.

Note that when you invoke the assembler as asm960 you can generate the COFF output format only.

#### **About This Manual**

This manual, the *i960 Processor Assembler User's Guide*, is part of the i960 processor software development tools manual set. See *Getting Started with the i960 Processor Software Development Tools* for a list of all manuals in the i960 processor development tools library.

The *i960 Processor Assembler User's Guide* provides operating instructions for the assembler. This manual does not teach development techniques.

#### **Target Audience**

To use the assembler effectively, you must be familiar with the i960 architecture and the development process.

This manual does not provide detailed information about the target processor. The processor manuals listed in *Getting Started with the i960 Processor Software Development Tools* contain information such as:

- a description of the i960 architecture

- the processor theory of operation and descriptions of the on-chip devices

- information about low-level programming for particular processors

For additional information about these topics, order the relevant publications listed in *Getting Started with the i960 Processor Software Development Tools*.

#### **Conventions**

In addition to the standard typographical conventions listed on the front inside cover, this manual uses the following notation and format conventions.

Case is significant for directives, functions, options, and option arguments. On UNIX\*, case is also significant for invocation names and filenames.

Arguments and operands are in italics. The operand names indicate the function of the operands (for example, filename, expr).

Directive and pseudo-instruction operands use the following notation:

addr represents an address.

align represents an exponent of 2, used as an alignment

factor.

data represents ordinal, integer, or floating-point data;

the format of the data depends on the instruction

or directive.

int represents a positive integer.

name represents a symbol or label.

size represents an integer, used as a size factor.

string represents a sequence of ASCII characters.

expr indicates an expression.

Special characters, delimiters, and other punctuation used with the operands, such as quotation marks and commas, are explicitly shown.

Notation for registers is one or more letters indicating the kind of register and a number between 0 and 15, as follows:

global register a register g0 through g14, and fp.

local register a register pfp, sp, rip, and r3 through r15.

special function register a register available only on the i960 Cx and

Hx processors: sf0-sf2 (Cx) and

sf0-sf4 (Hx).

floating-point register a register available only with on-chip floating-

point support: fp0, fp1, fp2, and fp3.

For more information on the registers, see the processor manuals listed in *Getting Started with the i960 Processor Software Development Tools*.

Target expressions (*targ*) representing a memory address are assembled as a signed displacement value representing an IP-relative address:

| Format | Displacement                          | Target (targ)                                 |  |

|--------|---------------------------------------|-----------------------------------------------|--|

| COBR   | -2 <sup>10</sup> : 2 <sup>10</sup> -1 | -2 <sup>12</sup> : 2 <sup>12</sup> -4 from IP |  |

| CTRL   | -2 <sup>21</sup> : 2 <sup>21</sup> -1 | -2 <sup>23</sup> : 2 <sup>23</sup> -4 from IP |  |

For convenience in cross-referencing material, the notation used in the reference sections follows that of the processor manuals listed in *Getting Started with the i960 Processor Software Development Tools*.

#### **Customer Service**

If you need service or assistance, see *Getting Started with the i960 Processor Software Development Tools*.

# Writing Assembly Language Code for the i960 Rx Processor

#### Introduction

This chapter provides information on designing assembly language code for use with the i960 Rx family of microprocessors, including the RP and RD processors. It describes the two possible paths to follow in designing assembly-language solutions for i960 Rx processors. The first of these paths is the "Rx Strategy", designed to ease transition to i960 Rx processors beyond the RP and RD. The other path is the "Jx-Specific Strategy", designed specifically for Rx processors that are based on the i960 Jx core (such as the RP and RD) and providing maximum low-level processor control.

## What is the "Rx Strategy?"

The "Rx Strategy" refers to a set of CTOOLS enhancements implemented to help you move from existing i960 RP and RD processors to possible future implementations of the i960 Rx family. CTOOLS added the new -ARP and -ARD architecture switches, which allow only those instructions that are most likely to be supported on future i960 Rx processor offerings. In addition, CTOOLS provides enhancements that have no effect on today's i960 Rx processors, but that may be used on future processors.

# How Do I Use the Rx Strategy?

Using the Rx strategy is as simple as specifying the -ARP or -ARD option when invoking the CTOOLS utilities. (You can also set the \$1960ARCH or \$G960ARCH environment variables to RP or RD.)

#### How Do I Use the Jx-Specific Strategy?

If you decide not to follow the Rx strategy, use the -AJF architecture option when creating code for use with i960 RP and RD processors. For information on specific differences between the -ARX switches and the -AJF switch, please see *Details of the "Rx Strategy"*. For help deciding if the Rx strategy is the best choice for your application, please read the next section.

#### **How Do I Decide Which Strategy to Use?**

Use these questions to help you decide which of the two development paths you should follow:

- How important is backward-compatibility with other i960 core processors (e.g., KA, CF, JF)? If you have legacy code that you wish to use with the i960 Rx processors, you may want to use the -AJF switch. Doing so gives you the most flexibility in terms of available instructions and addressing modes.

- How important is forward-compatibility with future i960 processors? If you wish to minimize the effort involved in moving to future Rx processors, you should use the Rx strategy.

- Will you be writing my applications from scratch? When writing new applications, follow the Rx strategy when possible. Tests have shown that there is seldom a significant performance or code size penalty, and you may actually see an improvement in either area.

- How much low-level processor access do you need? If you need

access to low-level processor resources such as the PC (Process

Control) or TC (Trace Control) registers beyond that provided in the

updated assembler pseudo-instructions (see Improved Assembler

Pseudo-instruction Support for gas960/asm960), you cannot use the

Rx strategy.

Based on your answers to the questions above, you should now be able to decide which path to follow: the Rx strategy or the Jx-specific strategy. After you make your decision, read the corresponding section below for specific tips on making the most of your programming environment. If

you choose to follow the Rx strategy, please read *Writing Assembly Code With the Rx Strategy*. If you choose to follow the Jx-specific strategy, please read *Writing Assembly Code Without the Rx Strategy*.

#### Writing Assembly Code With the Rx Strategy

To take advantage of CTOOLS enhancements supporting the Rx strategy, simply use the Rx architecture switches (e.g., -ARP, -ARD) for all applicable CTOOLS applications. You can also set the \$I960ARCH or \$G960ARCH environment variables to RP or RD. If you are migrating code written for other i960 core processors (e.g., KA, CF, HA), you can use xlate960, the 80960 translation utility as a starting point for your migration. The translator generates Rx-compatible code sequences to replace instructions and addressing modes that appear in the JF processor but not the Rx strategy. See *xlate960*, 80960 Assembly Language Translator for information on using this application.

If you need to use some of the JF-specific features not supported in the Rx strategy, such as disabling interrupts, cache control, or atomic accesses, you can use the new assembler pseudo-instructions. The primary benefit of using these instructions is that they should not require modification when assembled for future i960 Rx processors. Information on these new pseudo-instructions is available in *Improved Assembler Pseudo-instruction Support for gas960/asm960*. Note that if you use any of the new i960 processor pseudo-instructions you are required to re-assemble your source before running it on i960 Rx processors that are not based on the i960 JF core. This is because the instruction sequence generated for the new pseudo-instructions is not guaranteed to be compatible with future Rx processors.

Finally, specific information on the architectural implications of the -ARP and -ARD switches are in *Details of the Rx Strategy*.

#### Writing Assembly Code Without the Rx Strategy

To write code that is designed for i960 JF-based Rx processors only, use the JF architecture switch (-AJF) for all CTOOLS that require you to specify an architecture. (You can also set the \$1960ARCH or \$G960ARCH environment variables to JF.) You can still simplify future migration efforts by staying within the boundaries of the -ARP switch whenever possible. See *Details of the Rx Strategy* for information on the requirements.

For low-level processor functionality such as disabling interrupts, cache control, or atomic accesses you may wish to use the new assembler pseudo-instructions detailed in *Improved Pseudo-instruction Support for gas960/asm960*. This, too, may ease future migration without excluding use of JF-specific constructs.

# **Details of the Rx Strategy**

#### **80960 Instruction Set Support**

The implementation of the -ARX architecture options have been redefined in CTOOLS to represent a subset of the i960 Jx processor instruction set chosen for performance and future compatibility reasons. These restrictions are enforced by the assembler and other tools when an -ARX switch is used or when an i960 Rx architecture is specified using the I960ARCH or G960ARCH environment variables.

The following i960 Jx processor instructions are not supported with the i960 Rx architectures:

| addi            | halt   | remo           |

|-----------------|--------|----------------|

| addi <cc></cc>  | intctl | shli           |

| atadd           | ldt    | shrdi          |

| atmod           | mark   | spanbit        |

| cmpdeci         | modac  | stib           |

| cmpdeco         | modi   | stis           |

| cmpinci         | modify | stt            |

| cmpinco         | modtc  | subi           |

| concmpi         | movl   | subi <cc></cc> |

| concmpo         | movq   | sysctl         |

| eshro           | movt   | test <cc></cc> |

| extract         | notor  | xnor           |

| fault <cc></cc> | remi   |                |

In addition, the following addressing mode restrictions exist for MEM format instructions when specifying an i960 Rx processor-based target:

- Indexed addressing modes are not available.

- IP-relative addressing is not available.

- Two-word MEM-format is not available for the following instructions:

- ldl

- ldq

- stq

- bх

- callx

- The balx instruction may only use register-indirect addressing (no offsets or displacements allowed).

Other consequences of using the 80960Rx output architectures are:

- The calls instruction may use register g13 or a literal as its target only.

- For the modpc instruction, the mask cannot specify the same register as the src/dst register.

- The Process Controls register is undefined in the Rx architecture, so use of the modpc instruction is not recommended.

- The scanbit instruction is not guaranteed to set the condition code. The following instruction sequence duplicates the functionality of the scanbit instruction and is guaranteed to set the condition code:

scanbit src1,dst

notbit 31,dst,dst

chkbit 31,dst,dst

notbit 31,dst,dst

- The calljx pseudo-instruction requires a second argument, a temporary register into which the address of the first argument can be loaded.

- The assembler recognizes call4, call8, and call12 instructions.

These instructions are identical to the traditional call instruction except that the two low-order (reserved) bits of the instruction word are set as shown:

| Instruction | Bit 1 | Bit 0 |

|-------------|-------|-------|

| call4       | 0     | 1     |

| call8       | 1     | 0     |

| call12      | 1     | 1     |

• The assembler recognizes call4j, call8j, and call12j pseudo-instructions. They are treated by the assembler identically to the callj pseudo-op except they set the low-order bits as indicated in the table above if they are optimized into corresponding call4, call8, or call12 instructions.

In addition, a new assembler pseudo-op has been added:

```

b_960a label

```

This pseudo-op is reserved and should not be used by application software. The assembler generates an instruction, a no-op instruction, whose execution effectively leaves the state of the existing 80960Rx, 80960Jx, and 80960Hx processors unchanged. It is uncertain if this pseudo-op will continue to function in the same manner on future 80960 processors.

The assembler will generate the following no-op instruction for a b\_960a label pseudo-op:

```

addino TARG,fp,fp where TARG is (label-IP-4)/4 and 0 \le \text{TARG} \le 15

```

#### **Big-Endian Support**

Big endian byte order is not supported when code is being generated for the i960 Rx processors.

## **b.out OMF Support**

gas960, the b.out assembler, does not support an i960 Rx target.

## 80960 Assembly Language Converter (xlate960)

To ease the task of converting legacy assembly language code for use with the new i960 Rp/Rd processors, CTOOLS 6.0 includes xlate960. The xlate960 program converts assembly language code from 80960 core processors (e.g., i960 Cx, Jx, and Hx processors) to its CORE0 (e.g., 80960Rx) equivalent. xlate960 performs both instruction translations and addressing-mode translations. Instruction translation occurs when the target architecture does not support a translatable instruction from the source architecture (e.g., movt). Addressing mode translation occurs when the target architecture supports a restricted form of an instruction from the source architecture (e.g., callx). For more information on xlate960, see the *i960 Processor Software Utilities Manual*.

## **Improved Assembler Pseudo-instruction Support**

#### Introduction

A number of pseudo-instructions have been added to the CTOOLS assembler to ease migration between processors. These pseudo-ops provide an architecture-independent method for performing some of the more common low-level processing operations. Using these pseudo-ops should reduce the number of changes required when moving assembly code from one i960 processor to another. Table 2-1 lists all of the new pseudo-instructions supported by the CTOOLS assembler. See Chapter 8 for descriptions of the new pseudo-ops and instructions on using them.

Table 2-1 New Assembler Pseudo-Ops

| Instruction          | Action                                 |

|----------------------|----------------------------------------|

| atomic_add           | Atomic add                             |

| atomic_modify        | Atomic add Atomic modify               |

| ·                    | •                                      |

| bkpt_request         | Request breakpoint resources           |

| cc_read              | Read condition code                    |

| cc_scanbit           | Scan for bit, modifying condition code |

| dc_disable           | Disable data cache                     |

| dc_enable            | Enable data cache                      |

| dc_invalidate        | Invalidate data cache                  |

| em_read              | Read execution mode                    |

| ic_disable           | Disable instruction cache              |

| ic_enable            | Enable instruction cache               |

| ic_invalidate        | Invalidate instruction cache           |

| ic_load_lock         | Load and lock instruction cache        |

| insn_trace_mode_read | Read instruction trace mode            |

| insn_trace_mode_set  | Set instruction trace mode             |

| interrupt_state      | Read interrupt state                   |

| ip_read              | Read instruction pointer               |

| pri_read             | Read execution priority                |

| sw_reinit            | Reinitialize processor                 |

| trace_enable_set     | Set trace enable bit                   |

Invoking the Assembler

3

This chapter discusses the assembler invocation syntax, options, input, and output and explains how to automate assembly. You can invoke the assembler from the operating system prompt or from a script or batch file.

# **Invocation Command**

Invoke the assembler as follows:

| occurry occurry involved the accompliants are at COFF at                                                                                                    |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| invokes the assembler to generate COFF output The dual syntax provides backwards compatibility with previous versions of the iC-960 and gcc960 C compilers. | t. |

| gas960 invokes the assembler to generate b.out format output.                                                                                               |    |

| gas960e invokes the assembler to generate ELF format output.                                                                                                |    |

| is an invocation option (described in Chapter 4) affecting assembler input, operation, and output Arguments can follow some options. Case is significant.   |    |

| Precede the options with a hyphen (-). In Windows, you can use a slash (/) instead of the hyphen.                                                           | ;  |

| is an assembly source filename. You can provi<br>a complete path name for each source file. The<br>default search path is the current directory.            |    |

You can interleave options and source filenames.

**NOTES.** On UNIX, case is significant for all parts of the assembler invocation syntax. In Windows, case is significant only for the options and option arguments.

Examples throughout this manual use a UNIX host system and the gas960e invocation command and directory structures, unless otherwise noted.

The b.out assembler does not support the i960 RD/RP Processors.

## **Specifying Option Arguments**

Some options require arguments. The assembler interprets any string following such an option as the option argument. Omitting an option argument at the end of the command line causes an error. For example:

```

gas960e myprog.as -o

gas960: Expected a filename after -o.

```

You can put a space between an option and its argument. The following are both correct:

```

gas960e myprog.as -omyprog.o

gas960e myprog.as -o myprog.o

```

An incorrect argument causes an error message appropriate to the option. See Chapter 4, Option Reference, for information on the valid arguments for each option.

# **Specifying Single and Multiple Options**

```

Precede options with a hyphen (-):

gas960e myprog.as -o myprog.obj -W -V

```

On Windows\* 95/Windows NT\*-based machines, you can use a slash (/) instead of the hyphen.

Any string that does not begin with a hyphen and is not positioned as an option argument is interpreted as a source filename. The following example shows the message caused when the v option is specified without a hyphen and no file named v is in the search path:

```

gas960e -W V myprog.as

Can't open V for reading.

No such file or directory.

```

Some options consist of a single character with no arguments. You can specify two or more such options as an option group with a single hyphen:

```

gas960e myprog.as -o myprog.obj -WV

```

#### **Using Uppercase and Lowercase**

Depending on your host system, case can be significant in the assembler invocation name. For example, on Windows, entering ASM960 is the same as entering asm960. On UNIX, you can invoke the assembler with asm960 but not with ASM960.

Regardless of your host system, case is significant in the options and arguments. For example, an uppercase w is valid, but a lowercase w causes the following message:

Unrecognized option: w

#### Naming the Object File

After a successful assembly, the assembler produces an object file in common object file format (COFF), b.out or ELF format. To generate a COFF object file, invoke the assembler with asm960 or gas960c. To generate a b.out format object file, invoke the assembler with gas960. To generate an ELF file, use gas960e. For a description of the COFF file format, see your utilities user's guide. For a description of ELF, see the Intel 80960 EABI specification (Intel Literature order number 631999) listed in *Getting Started*.

When you specify a source file with the .s or .as extension, the assembler creates an object file with the extension .o. When you specify a file with any other extension (or none) the assembler creates an object file with full source filename (including its original extension) with .o appended.

When you provide the first block of input interactively, the object filename is a .out for COFF output, b .out for b.out format output, and e .out for ELF output. For example, the following produces a single object file named ex1.o:

#### gas960e ex1.s ex2.s ex3.s

To specify the object filename, use the  $\circ$  option. For example, the following creates or replaces an object file named ex1. $\circ$ :

```

gas960e example.src -o ex1.o

```

The assembler can overwrite an existing file unless the filename ends in .s, .as, or .asm. To ensure your source files are not accidentally overwritten, use the protected filename extensions. For example, if ex1.s exists, the following stops assembly with an error:

#### gas960e example.s -o ex1.s

FATAL: Output file will overwrite existing protected file.

Additional software utilities are available to read and reformat the object file, as described in the *i960 Processor Software Utilities User's Guide*.

#### **Providing Source Input**

You must provide source text from at least one of:

- a file named in the assembler invocation command

- stdin, such as the keyboard or the redirected output of another command

For information on stdin, see your host operating system documentation.

An assembly source file is an ASCII file of assembly language instructions and assembler directives. You can write the assembly source using a text editor or generate an assembly file with the C compiler.

For interactive input, specify the i option and provide lines of assembly source from stdin (for example, lines entered from the keyboard or piped from another application). The following example pipes the output of a script named mybuild (invoked with the UNIX C shell primitive source command) into the assembler:

```

source mybuild | gas960e -i

```

For information on piping, see your host operating system documentation.

To end keyboard input, type the Ctrl-d key combination on a new line. The following keyboard-entry example assembles five lines, naming the output object file e.out:

```

gas960e -i

roundr g0, fp0

subr fp0, g0, g0

expr g0, g0

addr 1.0, g0, g0

scaler g1, g0, g0

```

In the invocation command, list sources in the order in which you want them assembled. The assembler concatenates all source files and interactive input, then assembles instructions and data into sections by order of appearance in the source text. The following example assembles source from ex1.s, then from interactive input (the i option), then from ex2.s. Program elements from any one block of the input (for example, ex1.s) are available to any other block of the input (for example, ex2.s) as if all the input were in a single, sequential file.

#### gas960e ex1.s -i ex2.s

You can use other assembler options and source files with interactive input. The following example displays the assembler version and begins interactive input from the keyboard:

#### asm960 -V -i

To ensure your source files are not accidentally overwritten, use the .s, .as, or .asm protected filename extensions, as described in Naming the Object File on page 3-4.

#### **Environment Variables**

Environment variables set default operating parameters, such as search paths and the target architecture. For a list of environment variables and their uses, see your *Getting Started* manual. Define the environment variables before invoking the assembler.

The assembler supports all 1960 and G960 environment variables, preferring those that match the invocation style. For example, when you invoke the assembler as asm960, the assembler looks first for 1960 environment variables, and for those settings not found, looks for G960 environment variables. The environment variables used by the assembler are listed in Table 3-1.

Table 3-1 Assembler Environment Variables

| gnu Tools Name | CTOOLS Name | Purpose                                   |

|----------------|-------------|-------------------------------------------|

| G960ARCH       | I960ARCH    | Specifies target architecture.            |

| G960IDENT      | I960IDENT   | Allows use of the COFF .ident directive.  |

| G960INC        | 1960INC     | Specifies include directory path.         |

| G960BASE       | I960BASE    | Specifies base environment directory.     |

| G960XLT        | I960XLT     | Specifies translator (xlate960) location. |

For more information on environment variables, see your host operating system documentation.

#### **Selecting the Instruction Set and Libraries**

The assembler reports an error for any instruction in your source text that is not valid for your target processor instruction set. To assemble for a specific i960 processor, you can define the I960ARCH or G960ARCH architecture environment variable. Then, you need use the A option (described in Chapter 4) only to override the environment variable. Leaving the environment variable undefined and omitting the A option assembles for the i960 KB architecture.

To specify the default instruction set, define the architecture environment variable as SA, SB, KA, KB, CA, CF, JA, JD, JF, JT, RD, RP, HA, HD or HT. For example, the following specify SA instructions unless a different processor is specified with the A option:

csh setenv I960ARCH SA

sh or ksh I960ARCH=SA; export I960ARCH

Other i960 processor software tools also use the architecture environment variable, as described in *Getting Started*.

#### **Defining a Base Directory Path**

You can set an environment variable to the assembler and utilities base directory. Such a value can be useful for setting other search-path environment variables. The following defines a base-directory environment variable named G960BASE:

csh setenv G960BASE /usr/local/intel960

sh or ksh G960BASE=/usr/local/intel960;export G960BASE

#### **Defining an Identification String**

To put assembler identification and information from the .ident directive into a COFF object file, define the I960IDENT or G960IDENT environment variable to any non-null value, as shown in the following example:

csh setenv I960IDENT 1

sh or ksh I960IDENT=1;export I960IDENT

#### **Redirecting Error and Warning Message Output**

The I960ERR variable lets you specify whether messages are directed to stdout or stderr. When I960ERR is not set, messages go to stdout. When I960ERR is set to a non-null string, the output goes to stderr. This variable functions under Windows only.

# **Building a Search Path for Include Files**

You can extend the search path as follows for files included with .include:

- The assembler always searches the current directory first.

- You can specify additional directories with the I option, described in Chapter 4, Option Reference.

- You can specify a default list of directories, separated with colons (:), with I960INC or G960INC. When you do not use the I option, the assembler searches the directories specified by I960INC or G960INC.

Note that when you use both the I option and the I960INC or G960INC variables, the environment variable setting takes precedence.

The following commands set G960INC to /usr/local/intel960/include:

csh setenv G960INC /usr/local/intel960/include

sh or ksh G960INC=/usr/local/intel960/include;export G960INC

# **Building the Search Path for the Assembler Executable**

To invoke the assembler from any directory, add the assembler directory to your PATH environment variable. Once the directory is in your PATH, you need not use the directory path name to invoke the assembler.

For example, with I960BASE set to your assembler base directory, you can augment your PATH as follows:

csh setenv PATH \$1960BASE/bin:\$PATH

sh or ksh PATH=\$1960BASE/bin:\$PATH;export PATH

# Option Reference

This chapter describes the assembler options alphabetically. Table 4-1 summarizes the option names, arguments, effects, and defaults.

The following notation is used in this chapter:

$\{item | item\}$  Select one of the items listed between braces. A

vertical bar (|) separates the items.

[items] Items enclosed in brackets are optional.

Table 4-1 Assembler Options

| Option                                                                                                            | Effect of the Option                                                                                        | Default Action of the<br>Assembler                                                                                               |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| A { SA SB <br>KA KB <br>CA CF JA <br>JD JF JT <br>RD RP <br>HA HD HT <br>CORE0 <br>CORE1 <br>CORE2 <br>CORE3 ANY} | selects the instruction set.                                                                                | uses the instruction set<br>specified by the I960ARCH or<br>G960ARCH environment<br>variable, if defined; otherwise,<br>uses KB. |

| D sym[=value]                                                                                                     | defines an absolute symbol.<br>Symbols defined in this way<br>can be used in .if and .ifdef<br>expressions. | symbols must be defined in the source text.                                                                                      |

| d                                                                                                                 | retains debug information for local symbols beginning with L or a dot (.).                                  | discards symbolic information<br>for local symbols beginning<br>with L or a dot (.).                                             |

| G                                                                                                                 | generates big-endian COFF or ELF code.                                                                      | generates little-endian code.                                                                                                    |

continued 🗢

Table 4-1

Assembler Options (continued)

| Option                     | Effect of the Option                                                                           | Default Action of the Assembler                                                         |

|----------------------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|

|                            | Effect of the Option                                                                           | 7.000                                                                                   |

| h                          | Help: prints a brief description of each option.                                               | no help text is printed.                                                                |

| I directory path           | adds directories to the search path for include files.                                         | searches in the current directory and uses the I960INC or G960INC environment variable. |

| i<br>L <i>list_options</i> | reads source from stdin. generates a listing. Listing sub-options modify the listing behavior. | reads source from files. no listing is generated.                                       |

| n                          | do not replace compare-<br>and-branch instructions.                                            | replaces compare-and-branch instructions.                                               |

| o <i>objfile</i>           | specifies an object filename.                                                                  | uses a.out, b.out, e.out, or a filename derived from the first source filename.         |

| p {c   d   b}              | generates position-independent instructions and/or data.                                       | generates position-dependent code and data.                                             |

| V                          | displays a version message and continues the assembly.                                         | displays no version message.                                                            |

| v960                       | displays a version message and stops the assembly.                                             | displays no version message; the assembly proceeds.                                     |

| W                          | suppresses the warning messages.                                                               | displays the warning messages.                                                          |

| X                          | generates warnings about architecture mismatches.                                              | generates error message when it encounters architecture mismatch.                       |

| z                          | suppresses the object file header time-and-date stamp for COFF assembler.                      | writes the assembly time and date in the object file header.                            |

### A: Architecture

Select the architecture (instruction set)

A arch

arch

is SA, SB, KA, KB, CA, CF, JA, JD, JF, JT, RD, RP, HA, HD, HT, COREO, CORE1, CORE2, CORE3, or ANY.

#### **Discussion**

To select your i960 processor instruction set, specify the  $\mathbb A$  option. The assembler displays an error message for each instruction in the source text that is invalid for the selected architecture, or a warning when you use the  $\mathbb X$  option.

Without the A option, the assembler uses the instruction set specified by the I960ARCH or G960ARCH environment variable. If the architecture environment variable is undefined, the assembler uses the KB instruction set.

### **New CORE Architecture Options**

With CTOOLS release 5.1 and later, the assembler supports architecture settings to allow the generation of code that is compatible with multiple i960 processor types. These settings are referred to as *core* architectures. Table 4-2 shows the types of i960 processors that are supported by each core architecture.

Table 4-2 CORE0-3 Architecture Compatibilities

| -A Switch Used | Compatible Architectures |  |  |

|----------------|--------------------------|--|--|

| CORE 0         | Jx, Hx, Rx               |  |  |

| CORE1          | Kx, Sx, Cx, Jx, Hx       |  |  |

| CORE2          | Jx, Hx                   |  |  |

| CORE3          | Cx, Jx, Hx               |  |  |

# D: Define symbol

Define an absolute symbol from the command line

D symbol[=value]

is the name of the symbol you want to create.

value is any valid non-relocatable expression.

#### **Discussion**

This option is intended to be used with the .if and .ifdef directives for conditional assembly. It resembles the similar compiler preprocessor option. If =value is left blank, then the value of name is set to 1. If you want to include spaces anywhere with symbol=value, then the entire symbol=value must be quoted.

### **Examples**

```

The following creates a symbol called foo and sets its value to 1:

gas960 -D foo file.s

Within file.s, both of the following would evaluate to true:

.if foo

.ifdef foo

gas960 -D "foo = bar * 12" file.s

Within file.s, the symbol bar must be defined and be non-relocatable.

gas960 -D foo=0 file.s

Within file.s, the expression

.ifdef foo

is true, but the expression

.if foo

is false. (See the discussion of .if and .ifdef in Chapter 5.)

```

# d: Debug symbols

Keep debugging information about assembler temporary symbols

d

#### **Discussion**

The assembly output from the compiler contains local symbols beginning with an L, as generated by a gcc960 invocation of the compiler, or a dot (.), as generated by an ic960 invocation of the compiler. To retain such symbols in the object-file symbol table, specify the d option. Without d, the assembler removes all such local symbols.

### **Examples**

The following shows the original C source text and the corresponding assembly output with the local symbols generated by a gcc960 invocation of the compiler:

```

if (a==b)

hi=b;

else

hi=c;

```

The compiler assembly output (in the file cmset.s) is:

```

cmpi g0,g1

be L1

b L2

L1: st g1,hi

b A1

L2: st r6,hi

A1:

```

The following puts L1 and L2 in the object-file symbol table:

```

gas960c -d cmset.s

```

# G: Big-endian target

Produce a COFF or ELF file for a bigendian target

G

#### **Discussion**

You can configure COFF or ELF program text-type and data-type sections in either big-endian or little-endian byte order. For big-endian instructions and data, specify the G option when:

- assembling for the C-series, J-series, or H-series architecture

- invoking the assembler with asm960 or gas960c (COFF only) or gas960e (ELF only)

Note that the i960 RD/RP processors do not support big-endian byte order, even though their core processor is an 80960Jx.

For byte-order information, see *C*: A Reference Manual.

### **Example**

The following produces a COFF file for a big-endian target. The .text- and .data-style sections of the COFF file is in the host byte order, regardless of the G option.

gas960c -G -ACA big.a

### I: Include-file search path

Augment the search path for include files

I path

path

is a directory pathname.

#### **Discussion**

The assembler always searches the current directory for .include filenames. You can augment the search path by:

- defining the I960INC or G960INC environment variable (described in Chapter 3) before invoking the assembler

- using the I option once or more when invoking the assembler

The search path sequence is:

- 1. the current working directory

- 2. any directories specified by 1960INC or G960INC, in the order defined

- 3. any directories specified with I, in the order on the command line

### **Example**

The following line in the mathr.s source file includes the /mylib/fp.s source file:

```

.include "fp.s"

```

when invoked as:

asm960 mathr.s -I/mylib

# i: Input from stdin

Include keyboard or redirected input

i

#### **Discussion**

You must provide source text from at least one of:

- a filename specified on the command line

- the keyboard, the redirected output of another command, or any other device designated as stdin

For stdin input, use the i option once in the assembler invocation. To assemble keyboard input, after entering the command line, enter lines of source text from the keyboard. To end the keyboard input, enter the Ctrl-d key sequence on a new line. To assemble redirected output from another application, pipe the application output into the assembler invocation. You need not enter Ctrl-d to end the redirected input.

You can use both the i option and zero or more source filenames. The assembler processes the stdin input in sequence with any source files.

When stdin is the first or only source specified on the command line, the default object filename is a .out for a COFF object file, b.out for a b.outformat object file, and e.out for an ELF format objet file. Use the o option to specify a different object filename.

For information on piping and on stdin, see your host system manual.

### **Examples**

1. The following assembles several lines of code from the keyboard after the source text from the predef.s file:

```

gas960e predef.s -i

roundr g0, fp0

subr fp0, g0, g0

expr g0, g0

addr 1.0, g0, g0

scaler g1, g0, g0

^d

```

2. The following assembles the output from the getpatch script (invoked with the csh primitive source command) between src1.s and src2.s:

```

source getpatch | gas960e src1.s -i src2.s

```

# L: Generate a listing

Print an assembly listing on the screen or into a file

L [option [option-arg]]

| option |   | is one of the following:                                                                                                                          |

|--------|---|---------------------------------------------------------------------------------------------------------------------------------------------------|

|        | a | list all lines, ignoring .nolist directives.                                                                                                      |

|        | е | list text and data in target-endian byte order.                                                                                                   |

|        | f | print the listing into a file. option-arg is the name of the file.                                                                                |

|        | n | do not list files included with .include.                                                                                                         |

|        | t | use option-arg as the listing title. If the title contains spaces, then it must be quoted. This option overrides .title directives in the source. |

|        | Z | do not print the listing header.                                                                                                                  |

#### **Discussion**

With no options, the listing is printed on the standard output and all listing defaults are in effect. Options that do not take arguments can be catenated together (with no spaces) after a single  ${\tt L}$  option. Space is optional between an option that takes an argument and the argument.

The byte order of the listing is always target-endian when listing data sections. For text sections, instructions are printed big-endian ("left-to-right") unless you specify Le, and then they are printed in target-endian byte order.

### **Examples**

Several example listings follow. Where appropriate, the contents of the assembly language file is also shown. The first example shows the simplest listing invocation.

The file listex1.s contains:

```

.title "Listing Example 1"

.text

mov g0,g1

.data

.short 0x1234

```

The assembler invocation command is:

```

$ gas960e -L listex1.s

```

```

Listing Example 1

ASSEMBLER VERSION: Intel 80960 ELF Assembler, 6.0.6011, Thu Sep 26

23:25:43 MST 1997

TIME OF ASSEMBLY: Mon Oct 21 23:48:16 1997 COMMAND LINE: gas960e -L

listex1.s

Number of errors:

Number of warnings: 0

Source File: listex1.s

1 000000

.title

"Listing Example 1"

2 000000

.text

3 000000 5c881610

mov

g0,g1

4 000004

.data

5 000004 3412

0x1234

.short

The next example shows -Lz, (don't print the listing header), and -Lf,

(print listing in a file).

$ gas960 -Lz -Lf listex1.L listex1.s

The file listex1.L contains:

Source File: listex1.s

1 000000

.title "Listing Example 1"

2 000000

.text

3 000000 5c881610

mov g0,g1

4 000004

.data

.short 0x1234

5 000004 3412

The next example shows the effect of the .nolist directive on the listing.

The file listex2.s contains:

.title "Listing Example 2"

.text

mov g0,g1

.data

.short 0x1234

.nolist

.asciz "Skip strings in the listing"

.asciz "Skip this one too"

.list

.word 0x12345678

```

#### The assembler command is:

#### \$ gas960e -L listex2.s

```

Listing Example 2

ASSEMBLER VERSION: Intel 80960 ELF Assembler, 6.0.6011, Thu Sep 26

23:25:43 MST 1997

TIME OF ASSEMBLY: Mon Oct 21 23:51:23 1997 COMMAND LINE: gas960e -L

listex2.s

Number of errors:

Number of warnings: 0

Source File: listex2.s

1 000000

"Listing Example 2"

.title

2 000000

.text

3 000000 5c881610

mov

g0,g1

4 000004

.data

5 000004 3412

.short

0x1234

6 000006

.nolist

7 000006

.list

8 000006

7856 3412

0x12345678

.word

```

The .nolist directive can be defeated from the command line with -La:

#### \$ gas960c -Lza listex2.s

```

Source File: listex2.s

1 000000

.title "Listing Example 2"

2 000000

.text

3 000000

5c881610

mov g0,g1

4 000004

.data

5 000004

3412

.short 0x1234

6 000006

.nolist

536b 69702073

7 000006

.asciz "Skip strings in the

listing"

7 00000c 7472696e 67732069

7 000014 6e207468 65206c69

7 00001c 7374696e 6700

8 000022

.asciz "Skip this one too"

536b

8 000024 69702074 68697320

8 00002c 6f6e6520 746f6f00

9 000034

.list

10 000034 78563412

.word 0x12345678

```

Normally, text sections are listed in big-endian byte order. This matches left-to-right ordering of instructions in manuals. You can override this behavior on the command line with -Le. Note in the next example that the listing show the exact ordering of bytes in the object file:

#### \$ gas960c -Lze listex2.s

```

Source File: listex2.s

1 000000

.title "Listing Example 2"

2 000000

.text

3 000000 1016885c

mov g0,g1

4 000004

.data

5 000004 3412

.short 0x1234

6 000006

.nolist

9 000034

.list

10 000034 78563412

.word 0x12345678

```

Here is another example that shows big-endian byte order in both the text and data sections:

#### \$ gas960c -ACA -G -Lze listex2.s

```

Source File: listex2.s

1 000000

.title "Listing Example 2"

2 000000

.text

3 000000 5c881610

mov g0,g1

4 000004

.data

.short 0x1234

5 000004 1234

6 000006

.nolist

000034

.list

10 000034 12345678

.word 0x12345678

```

The next example shows the effect of the .include directive on the listing. The file listex3.s contains:

```

.title "Listing Example 3"

.text

mov g0,g1

.ifdef INCLUDE4

.include "listex4.s"

.endif

.data

.short 0x1234

```

The file listex4.s contains:

foo

ldconst -1, g6

The assembler command is:

#### \$ gas960 -Lz -D INCLUDE4 listex3.s

```

Source File: listex3.s

1 000000

.title "Listing Example 3"

2 000000

.text

3 000000 5c881610

mov g0,g1

4 000004

.ifdef INCLUDE4

5 000004

.include "listex4.s"

Source File: ./listex4.s

1 000004

foo:

2 000004 59b01901

ldconst -1, g6

Source File: listex3.s

.endif

6 000008

7 000008

.data

8 000008 3412

.short 0x1234

```

You can tell the assembler to not list include files with -Ln:

#### \$ gas960 -Lzn -D INCLUDE4 listex3.s

```

Source File: listex3.s

1 000000

.title "Listing Example 3"

2 000000

.text

3 000000 5c881610

mov g0,g1

4 000004

.ifdef INCLUDE4

5 000004

.include "listex4.s"

6 000008

.endif

7 000008

.data

8 000008 3412

.short 0x1234

```

The last example shows how to override the .title directive from the command line with -Lt:

#### \$ gas960e -Lt "LISTING EXAMPLE 247" listex3.s

```

LISTING EXAMPLE 247

ASSEMBLER VERSION: Intel 80960 ELF Assembler, 6.0.6002, Thu Sep 26

23:25:43 MST 1997

TIME OF ASSEMBLY: Mon Oct 21 23:54:54 1997

COMMAND LINE: gas960e -Lt LISTING EXAMPLE 247 listex3.s

Number of errors:

Number of warnings: 0

Source File: listex3.s

.title

1 000000

"Listing Example 3"

2 000000

.text

3 000000 5c881610

mov g0,g1

4 000004

.ifdef INCLUDE4

5

000004

.include "listex4.s"

6 000004

.endif

7 000004

.data

8 000004 3412

0x1234

.short

```

### n: No compare-and-branch replacement

Do not replace compare-and-branch instructions

n

#### **Discussion**

For short conditional branches and jumps, you can save execution time and space by using a single compare-and-branch (COBR) instruction. The branch address can be any expression that evaluates to a 13-bit value.

To stop the assembler with an error when the branch address is out of range, specify the n option. Without n, the assembler replaces the short-range compare-and-branch instruction with two instructions.

#### **Examples**

1. In the following, n prevents the assembler from expanding the cmpibe instruction for the undefined external m1. The assembler displays an error message.

```

$ gas960e -i -n

cmpibe g0,g1,ml

^D

can't use COBR format with external label

```

2. Without n, and with the s option, the following replaces empibe:

```

0: 5a046090 cmpi g0,g1

4: 12fffffc be m1

```

### o: Object filename

Name the object file

```

o objfile is a valid filename.

```

#### **Discussion**

To specify the object filename, use the o option with a filename or a complete pathname. The default object filename is in the current directory:

- a filename based on the first source filename on the command line, replacing any .s or .as source-filename extension with .o or appending .o to any other source filename after the extension.

- a.out, when you invoke the assembler with asm960 or gas960c (for COFF output) with interactive input as the first or only source.

- b.out, when you invoke the assembler with gas960 (for b.out-format output) with interactive input as the first or only source.

- e.out, when you invoke the assembler with gas960e (for ELF output) with interactive input as the first or only source.

To avoid accidentally overwriting your source files, use a protected .s, .as, or .asm source-filename extension (the assembler does not overwrite existing files with one of these extensions).

#### **Example**

The following names the output file progl.o:

```

asm960 myprog.asm -o prog1.o

```

### p: Position independence

Mark the COFF or ELF object file as containing position-independent code or data

p type

type is one of the following:

c indicates position-independent code.

d indicates position-independent data.

b indicates both position-independent code and data.

#### **Discussion**

To indicate position-independent code or data in the COFF or ELF file, use the p option. You can also use the .pic, .pid, and .link\_pix directives, described in Chapter 5.

### **Example**

The following marks the object file as position-independent:

```

asm960 -pb mypi23.s

```

### t: Translate

Process all source files with the xlate960 translation utility before assembly

t

#### **Discussion**

To first process the input source file with xlate960, use t. xlate960 attempts to translate the source file to its COREO (e.g., 80960Rx) equivalent. If any errors occur during the translation process, the assembler does not attempt to process the xlate960 output file. This includes instances where the translator output file requires manual adjustments.

#### **Example**

The following shows an example invocation of xlate960 from the assembler command-line:

```

$ cat myprog.s

addino r5,r6,r7

$ gas960e myprog.s -t -ARP

$ gdmp960 myprog.o

Section '.text':

0: 78398005 addono r5,r6,r7

Section '.data':

```

In this example, the translator converted the 80960 CORE instruction addino with the 80960 CORE0-compatible instruction addono.

**NOTE.** The t (translate with xlate960) option is incompatible with the i (process input from stdin) command-line option.

# V, v960: Version

Display the assembler version number and creation date

#### **Discussion**

To display a version message on stdout during assembly, use v. After displaying the message, the assembler continues. For information on stdout, see your host system manual.

To display the message without assembling, use v960. After displaying the message, the assembler stops.

The message includes the assembler version number and the assembler creation date and time.

### **Example**

The following shows a sample version message:

```

$ gas960e myprog.asm -v960

```

Intel 80960 ELF Assembler, 6.0.6002, Thu Sep 26 23:25:43

MST 1997

# W: Warnings

Suppress the warning messages

W

#### **Discussion**

To suppress the warning messages, use w. The error messages continue to appear on stderr. For information about the message formats, see Chapter 6. For information on stderr, see your host system manual.

### x: Allow mixed architectures

Allow architecture mismatches

х

#### **Discussion**

Using the x option causes the assembler to generate warnings (not errors) when it encounters mixed architectures (e.g., opcode not in target architecture).

### **Example**

The following shows how using the x command-line switch affects the assembler's treatment of architecture-specific instruction mismatches:

```

$ cat myprog.s

xnor

r5,r6,r8

r8,r10(g10)[g4*4]

stl

$ gas960e myprog.s -ARP

myprog.s:1: Opcode is not in target architecture: "xnor".

myprog.s:2: indexed addressing mode not available

$ ls myprog.o

ls: myprog.o: No such file or directory

$ gas960e myprog.s -ARP -x

myprog.s:1: Warning: Opcode is not in target architecture: "xnor".

myprog.s:2: Warning: indexed addressing mode not available

$ ls myprog.o

myprog.o

$

```

# z: Time stamp

Suppress the time stamp in the COFF output file

Z

#### **Discussion**

The assembler puts the current time and date in the file header of the COFF output file. On most UNIX systems, to put Time Zero in place of the current time stamp, specify z. Time Zero is 4:00, 31 December, 1969.

The z option has no effect on b.out or ELF format output.

### **Example**

The following command specifies Time Zero for the time stamp:

gas960e -z file1.s