# AP-716 APPLICATION NOTE

# 80960Cx/80960Jx/80960Hx Architectural Comparison

**Tom Johnson** SPG 80960 Systems Engineer Intel Corporation Mail Stop CH6-311 5000 W. Chandler Blvd. Chandler, Arizona 85226

January 29, 1996

Order Number: 272694-001

Information in this document is provided solely to enable use of Intel products. Intel assumes no liability whatsoever, including infringement of any patent or copyright, for sale and use of Intel products except as provided in Intel's Terms and Conditions of Sale for such products.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local Intel sales office or your distributor to obtain the latest specifications before placing your product order

MDS is an ordering code only and is not used as a product name or trademark of Intel Corporation.

Intel Corporation and Intel's FASTPATH are not affiliated with Kinetics, a division of Excelan, Inc. or its FASTPATH trademark or products.

$\ensuremath{^{\star}}\xspace \mbox{Other}$  brands and names are the property of their respective owners.

Additional copies of this document or other Intel literature may be obtained from:

Intel Corporation Literature Sales P.O. Box 7641 Mt. Prospect, IL 60056-7641 or call 1-800-879-4683

© INTEL CORPORATION 1995

## 80960Cx/80960Jx/80960Hx ARCHITECTURAL COMPARISON

| 1.0 | Introduction        | 1                                                                        | 1    |

|-----|---------------------|--------------------------------------------------------------------------|------|

| 1.1 | i960 <sup>®</sup> F | Processor Family                                                         | 1    |

| 1.1 |                     | 80960Cx Processor Family                                                 |      |

| 1.1 | .2 The              | 80960Jx Processor Family                                                 | 2    |

| 1.1 |                     | 80960Hx Processor Family                                                 |      |

| 2.0 | Initialization      | ٠                                                                        | 3    |

| 2.1 | Initializ           | ration Data Structures                                                   | 3    |

| 2.1 |                     | alization Boot Record (IBR)                                              |      |

| 2.1 |                     | cessor Control Block (PRCB)                                              |      |

| 2.1 |                     | ılt Table                                                                |      |

| 2.1 | .4 Cor              | ntrol Table                                                              | 9    |

| 2.1 | .5 Aritl            | hmetic Control Register Initial Image                                    | 11   |

| 2.1 | .6 Fau              | ılt Configuration Word                                                   | 11   |

| 2.1 |                     | rrupt Table                                                              |      |

| 2.1 |                     | tem Procedure Table                                                      |      |

| 2.1 | .9 Inte             | rrupt Stack Pointer                                                      | 12   |

| 2.1 | .10 Inst            | ruction Cache Configuration Word                                         | 12   |

| 2.1 |                     | gister Cache Configuration Word                                          |      |

| 2.2 | Registe             | er Values after Reset/Reinitialization                                   | 12   |

| 2.2 | .1 Con              | nmon Reset/Reinitialized States                                          | 12   |

| 2.2 | .2 Diffe            | erences in the Reset/Reinitialized State                                 | 14   |

| 2.3 | Initial E           | Bus Configuration                                                        | 16   |

| 2.3 |                     | 60Cx Processor                                                           |      |

| 2.3 | .2 809              | 60Jx Processor                                                           | 16   |

| 2.3 | .3 809              | 60Hx Processor                                                           | 17   |

| 2.3 | .4 Exte             | ernal Bus Configuration                                                  | 18   |

| 2.  | 3.4.1               | External Memory Configuration on the 80960Cx Processor                   |      |

|     | 3.4.2               | External Memory Configuration on the 80960Jx Processor                   |      |

| 2.  | 3.4.3               | External Memory Configuration on the 80960Hx Processor                   | 23   |

| 3.0 | New and E           | xtended Instructions                                                     | . 27 |

| 3.1 | New In              | structions Supported by the 80960Jx and 80960Hx Processors               | 27   |

| 3.1 | .1 Cor              | nditional Integer/Ordinal Add and Subtract and Select Value Instructions | 28   |

| 3.  | 1.1.1               | Operation of Conditional Add Instruction                                 |      |

| _   | 1.1.2               | Operation of Conditional Subtract Instruction                            |      |

|     | 1.1.3               | Operation of Select Value Instruction                                    |      |

| 3.1 |                     | e Swap Instruction (bswap)                                               |      |

| 3.1 |                     | npare Integer/Ordinal Byte and Short Instructions                        |      |

| 3.1 |                     | a Cache Control Instruction (dcctl)                                      |      |

|     | 1.4.1               | Function Zero - Disable the Data Cache (src1 == 0)                       |      |

| 3.  | 1.4.2               | Function One - Enable the Data Cache (src1 == 1)                         | 29   |

| 3.1.4.3  | , , , , , , , , , , , , , , , , , , , ,                       | 29 |  |  |  |  |

|----------|---------------------------------------------------------------|----|--|--|--|--|

| 3.1.4.4  |                                                               |    |  |  |  |  |

|          | External Memory (src1 == 3)                                   | 29 |  |  |  |  |

| 3.1.4.5  |                                                               | 29 |  |  |  |  |

| 3.1.4.6  | , ,                                                           |    |  |  |  |  |

| 3.1.5    | Instruction Cache Control Instruction (icctl)                 |    |  |  |  |  |

| 3.1.5.1  |                                                               |    |  |  |  |  |

| 3.1.5.2  | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

| 3.1.5.3  | ,                                                             |    |  |  |  |  |

| 3.1.5.4  | <b>'</b>                                                      |    |  |  |  |  |

| 3.1.5.5  |                                                               |    |  |  |  |  |

| 3.1.5.6  | 3                                                             |    |  |  |  |  |

| 3.1.5.7  | , ,                                                           |    |  |  |  |  |

| 3.1.6    | Interrupt Control Instruction                                 |    |  |  |  |  |

| 3.1.6.1  | , , , , , , , , , , , , , , , , , , , ,                       |    |  |  |  |  |

| 3.1.6.2  | , ,                                                           |    |  |  |  |  |

| 3.1.6.3  | ,                                                             |    |  |  |  |  |

| 3.1.7    | Global Interrupt Disable                                      |    |  |  |  |  |

| 3.1.8    | Global Interrupt Enable                                       | 33 |  |  |  |  |

| 3.1.9    | Halt Instruction                                              |    |  |  |  |  |

| 3.1.9.1  |                                                               |    |  |  |  |  |

| 3.1.9.2  | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

| 3.1.9.3  | , ,                                                           |    |  |  |  |  |

| 3.1.10   | Flush Data Cache Contents by Address Instruction (dcflusha)   | 33 |  |  |  |  |

| 3.1.11   | Give Address to Data Cache as Hint Instruction (dchint)       | 34 |  |  |  |  |

| 3.1.12   | Data Cache Invalidate by Address Instruction (dcinva)         | 34 |  |  |  |  |

| 3.2      | Extended Instructions                                         | 34 |  |  |  |  |

| 3.2.1    | System Control Instruction (sysctl)                           | 34 |  |  |  |  |

| 3.2.1.1  | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

| 3.2.1.2  | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

| 3.2.1.3  |                                                               |    |  |  |  |  |

| 3.2.1.4  | , , , , , , , , , , , , , , , , , , , ,                       |    |  |  |  |  |

| 3.2.1.5  | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

| 3.2.1.6  | Function Five - Modify One Memory-mapped Control Register     |    |  |  |  |  |

|          | (Message Type 05H)                                            | 35 |  |  |  |  |

| 3.2.1.7  | Function Six - Breakpoint Resource Request (Message Type 06H) | 35 |  |  |  |  |

| 4.0 Regi | ster Cache/Stack Frames                                       | 35 |  |  |  |  |

|          | Register Cache Configuration on the 80960Cx Processor         |    |  |  |  |  |

|          | · · · · · · · · · · · · · · · · · · ·                         |    |  |  |  |  |

|          |                                                               |    |  |  |  |  |

|          | Register Cache Configuration on the 80960Hx Processor         |    |  |  |  |  |

|          | kpoint Resource Sharing Mechanism                             |    |  |  |  |  |

|          | Breakpoint Resources on the 80960Cx Processor                 |    |  |  |  |  |

| 5.2      | 5.2 Breakpoint Resources on the 80960Jx Processor             |    |  |  |  |  |

| inte | <b>.</b> |

|------|----------|

|      | 7        |

| 5.3       | Breakpoint Resources on the 80960Hx Processor              | 38 |

|-----------|------------------------------------------------------------|----|

| 6.0 Inte  | egrated Peripherals                                        | 39 |

| 6.1       | Direct Memory Access Control Unit on the 80960Cx Processor | 39 |

| 6.2       | Guarded Memory Unit on the 80960Hx Processor               | 40 |

| 6.3       | Interrupt Control Unit                                     | 40 |

| 6.3.1     | 80960Cx Processor Interrupt Control Unit                   | 40 |

| 6.3.1.    |                                                            |    |

| 6.3.1.    | 2 Interrupt Mapping Registers (IMAP0-IMAP2)                | 41 |

| 6.3.1.    | 3 3 3 4 7 7                                                |    |

| 6.3.2     | 80960Jx/80960Hx Processor Interrupt Control Unit           | 43 |

| 6.3.2.    |                                                            |    |

| 6.3.2.    | =                                                          |    |

| 6.3.2.    | 3 3 3 4 7 7                                                |    |

| 6.3.2.    | 4 Improvements to Interrupt Latency                        | 46 |

| 6.4       | Timer Unit                                                 | 46 |

| 7.0 Mei   | mory-mapped Control Registers                              | 47 |

| 7.1       | Special Function Registers and Memory-mapped Counterparts  |    |

| 7.1.1     | Special Function Registers on the 80960Cx Processor        |    |

| 7.1.2     | Special Function Registers on the 80960Hx Processor        |    |

| 7.1.2     | Openal Full of the Cooper IX From Cooper III               | 10 |

| 8.0 Mei   | mory-mapped Control Register Address Space                 | 49 |

| 9.0 809   | 960Hx/80960Cx Pin Compatibility                            | 54 |

| 10.0 Cor  | nclusion                                                   | 56 |

| 4405      |                                                            |    |

| 11 () Rel | ated Information                                           | 56 |

| FIGURES    |                                                                                       |    |

|------------|---------------------------------------------------------------------------------------|----|

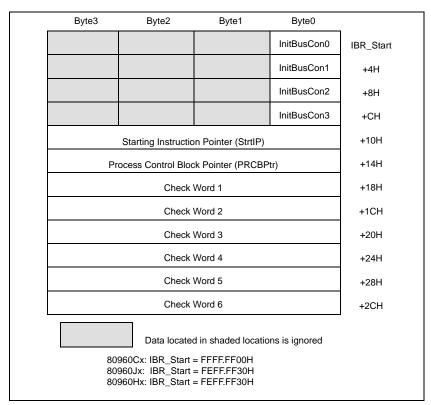

| Figure 1.  | Initialization Boot Record (IBR) Structure                                            | 4  |

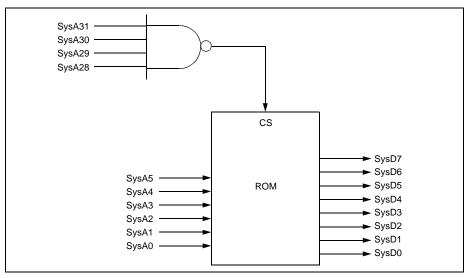

| Figure 2.  | Simplified Typical Memory Decoding Logic                                              | 5  |

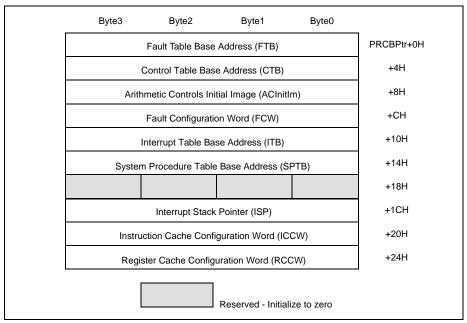

| Figure 3.  | Processor Control Block (PRCB) Structure                                              | 6  |

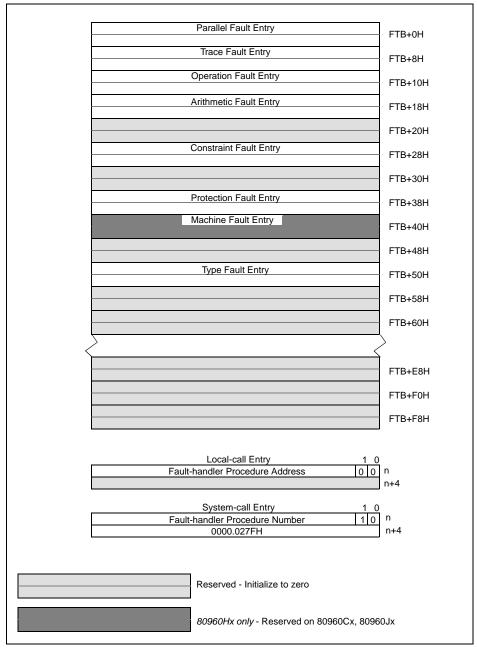

| Figure 4.  | 80960Cx 80960Jx, and 80960Hx Fault Table and Fault Table Entries                      | 7  |

| Figure 5.  | 80960Cx MCON Register Format                                                          | 18 |

| Figure 6.  | 80960Cx BCON Register                                                                 | 19 |

| Figure 7.  | PMCON Register Format for the 80960Jx Processor                                       | 20 |

| Figure 8.  | Format of LMARx and LMMRx Pairs on the 80960Jx Processor                              | 21 |

| Figure 9.  | Format of the DLMCON Register on the 80960Jx                                          | 22 |

| Figure 10. | Format of the BCON Register on the 80960Jx                                            | 23 |

| Figure 11. | PMCON Register Format for the 80960Hx Processor                                       | 24 |

| Figure 12. | LMARx and LMMRx Registers on the 80960Hx Processor (LMCONx Pair)                      | 25 |

| Figure 13. | DLMCON Register on the 80960Hx                                                        | 26 |

| Figure 14. | Format of the BCON Register on the 80960Hx                                            | 26 |

| Figure 15. | Register Cache Configuration Word (RCCW) for the 80960Cx Processor                    | 36 |

| Figure 16. | Register Cache Configuration Word (RCCW) for the 80960Jx Processor                    | 36 |

| Figure 17. | Register Cache Configuration Word (RCCW) for the 80960Hx Processor                    | 37 |

| Figure 18. | Interrupt Control Register on the 80960Cx Processor                                   | 41 |

| Figure 19. | Interrupt Mapping Registers on the 80960Cx Processor                                  | 42 |

| Figure 20. | Interrupt Pending (sf0) and Interrupt Mask (sf1) on the 80960Cx Processor             | 43 |

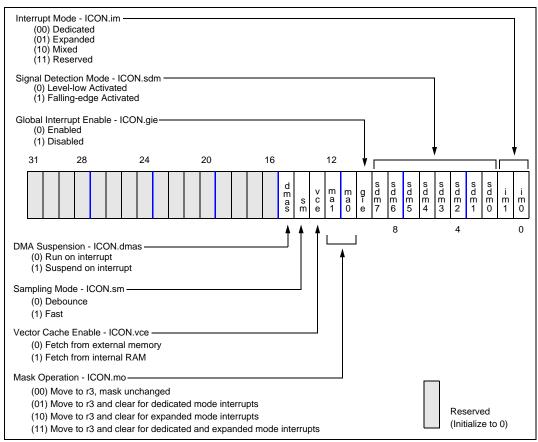

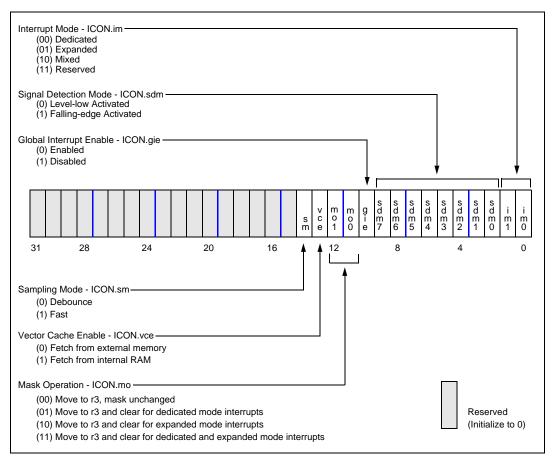

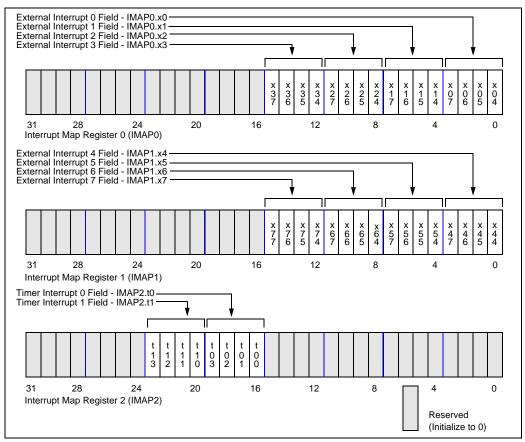

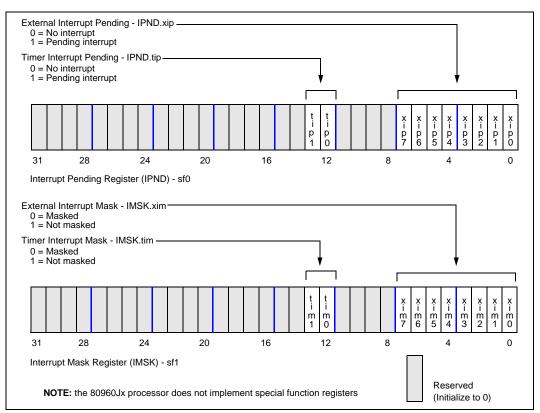

| Figure 21. | Interrupt Control Register (ICON) on the 80960Jx and 80960Hx Processors               | 44 |

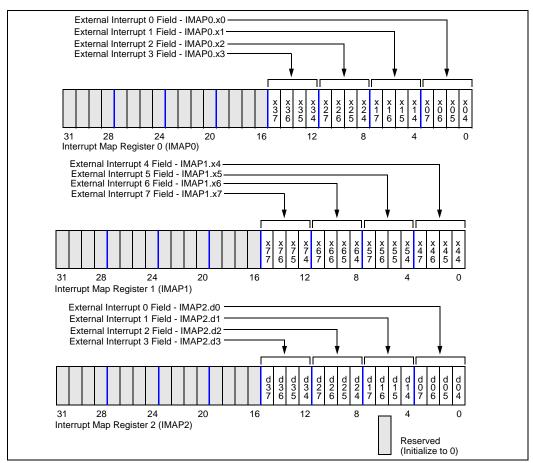

| Figure 22. | Interrupt Mapping Registers on the 80960Jx and 80960Hx Processors                     | 45 |

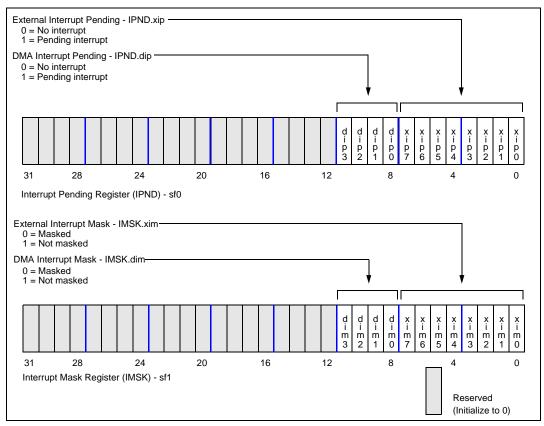

| Figure 23. | Interrupt Pending (sf0) and Interrupt Mask (sf1) on the 80960Jx and 80960Hx Processor | 46 |

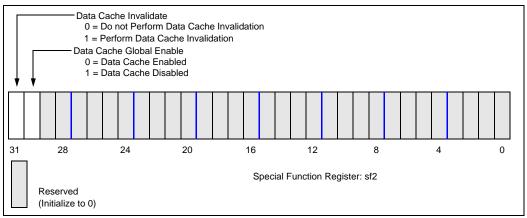

| Figure 24. | 80960Hx Processor Data Cache Control Register                                         | 48 |

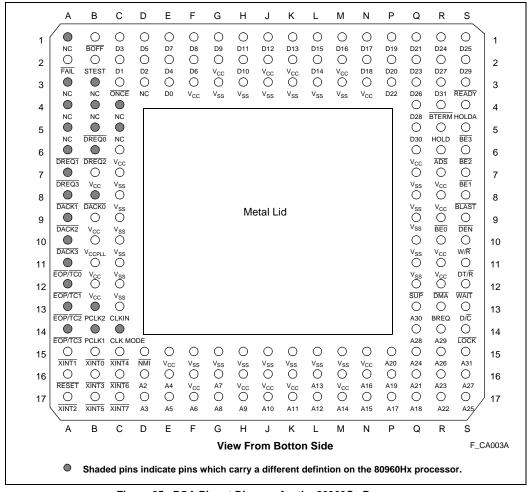

| Figure 25. | PGA Pinout Diagram for the 80960Cx Processor                                          |    |

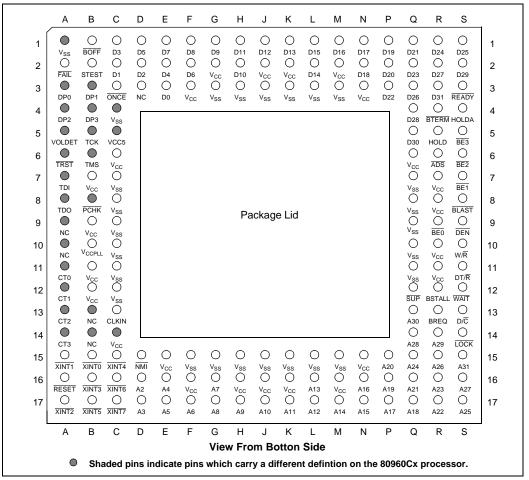

| Figure 26. | PGA Pinout Diagram for the 80960Hx Processor                                          | 55 |

| TABLES     |                                                                                       |    |

| Table 1.   | Feature Summary of the 80960Cx, 80960Jx, and 80960Hx Processors                       | 1  |

| Table 2.   | 80960Cx, 80960Jx, and 80960Hx Fault Types and Subtypes                                | 8  |

| Table 3.   | Control Table for the 80960Cx, 80960Jx, and 80960Hx Processors                        |    |

| Table 4.   | Common State of the i960 <sup>®</sup> Processors after Reset/Reinitialization         |    |

| Table 5.   | Differences in State of the i960® Processors after Reset/Reinitialization             |    |

| Table 6.   | New 80960Jx and 80960Hx Instructions                                                  | 27 |

| Table 7.   | Condition Code Masks                                                                  |    |

| Table 8.   | Format of Data Cache Status                                                           |    |

| Table 9.   | Function Six - Store Data Cache Sets to Memory (src1 == 6)                            | 30 |

| Table 10. | Function Three - Load and Lock Code into the Instruction Cache (src1 == 3) | 31 |

|-----------|----------------------------------------------------------------------------|----|

| Table 11. | Format of Instruction Cache Status                                         | 31 |

| Table 12. | Format of Instruction Cache Locking Status                                 | 32 |

| Table 13. | Function Six - Store Instruction Cache Sets to Memory (src1 == 6)          | 32 |

| Table 14. | src/dst Field Definitions for Breakpoint Resource Request                  | 35 |

| Table 15. | Integrated Peripherals on the 80960Cx, 80960Jx, and 80960Hx Processors     | 39 |

| Table 16. | Sample Application with Restricted Memory Partitions                       | 40 |

| Table 17. | Timer Control Registers on the 80960Jx and 80960Hx Processors              | 47 |

| Table 18. | Special Function Registers of the 80960Hx Processor                        | 48 |

| Table 19. | Memory-mapped Control Registers                                            | 49 |

AP-716 intel.

viii

### 1.0 Introduction

This document describes three implementations of the  $i960^{\text{@}}$  architecture: the 80960Cx, 80960Jx, and 80960Hx microprocessors.

During the 80960Jx and 80960Hx definition process, every attempt was made to maintain backward compatibility with the 80960Cx processor. To a large extent, this compatibility is maintained; most application code will run on each processor without modification. Due to enhancements to the bus interface, instruction set, and other refinements, complete compatibility was not maintained. This document discusses in detail those differences between the 80960Cx, 80960Jx, and 80960Hx microprocessors. Suggestions are given for mitigating their impact on future designs.

This document also provides hints for developing applications which the 80960Cx processor can use now, and can be 80960Hx-ready in the future. The reader should note that the 80960Hx processor is **not drop-in compatible** with the

80960Cx processor. However, system hardware can be designed such that it will accept both the 80960Cx and 80960Hx processors in the same socket.

This document contains condensed information from the  $i960^{\circ}$  Cx Microprocessor User's Manual (Intel Literature Order No. 270710), Application Note 506, Designing for 80960Cx and 80960Hx Compatibility (Intel Literature Order No. 272556), the  $i960^{\circ}$  Jx Microprocessor User's Manual (Intel Literature Order No. 272483), and the  $i960^{\circ}$  Hx Microprocessor User's Manual, (Intel Literature Order No. 272484). The reader should refer to these documents for more detailed information.

## 1.1 i960<sup>®</sup> Processor Family

Table 1 summarizes the features of the 80960Cx, 80960Jx, and 80960Hx microprocessor families. Subsections which follow further describe each processor's features.

Table 1. Feature Summary of the 80960Cx, 80960Jx, and 80960Hx Processors (Sheet 1 of 2)

| Feature                                  | Processor                                                             |                                        |                                                                       |  |  |

|------------------------------------------|-----------------------------------------------------------------------|----------------------------------------|-----------------------------------------------------------------------|--|--|

| reature                                  | 80960Cx                                                               | 80960Jx                                | 80960Hx                                                               |  |  |

| Core                                     | Superscalar (maximum 3 inst/clk)                                      | Scalar, clock doubled                  | Superscalar (max 3 inst/clk), clock doubled, clock tripled            |  |  |

| External Bus                             | 32-bit demultiplexed address and data                                 | 32-bit multiplexed address/data        | 32-bit demultiplexed address and data, parity on data                 |  |  |

| Instruction Cache                        | CA: 1 Kbyte, 2-way<br>CF: 4 Kbytes, 2-way                             | 4 Kbytes, 2-way                        | 16 Kbytes, 4-way                                                      |  |  |

| Data Cache                               | CA: None<br>CF: 1 Kbyte, direct map,<br>write-through                 | 2 Kbytes, direct map,<br>write-through | 8 Kbytes, 4-way, write-<br>through                                    |  |  |

| Data RAM                                 | 1 Kbyte, mapped from 000H to 3FFH                                     | 1 Kbyte, mapped from<br>0000H to 3FFH  | 2 Kbytes, mapped from 000H to 7FFH                                    |  |  |

| Register Cache                           | 5 frames, programmable<br>to 15 frames (more than 5<br>uses Data RAM) | 8 frames                               | 5 frames, programmable<br>to 15 frames (more than 5<br>uses Data RAM) |  |  |

| Memory-mapped<br>Registers               | No                                                                    | Yes                                    | Yes                                                                   |  |  |

| Direct Memory Access<br>(DMA) Controller | Yes                                                                   | No                                     | No                                                                    |  |  |

1

Table 1. Feature Summary of the 80960Cx, 80960Jx, and 80960Hx Processors (Sheet 2 of 2)

| Feature              |         | Processor  |                   |

|----------------------|---------|------------|-------------------|

| reature              | 80960Cx | 80960Jx    | 80960Hx           |

| Interrupt Controller | Yes     | Yes        | Yes               |

| Guarded Memory Unit  | No      | No         | Yes               |

| Timers               | None    | Two        | Two               |

| Power Supply         | 5V      | 5V or 3.3V | 3.3V, 5V tolerant |

| JTAG                 | No      | Yes        | Yes               |

### 1.1.1 The 80960Cx Processor Family

The 80960Cx family of processors are superscalar implementations of the i960 microprocessor architecture, and feature demultiplexed, 32-bit address and data buses. The two members of this family, the CA and CF, can execute up to three instructions per clock cycle. Due to the high degree of parallelism and on-chip caches, these processors are well suited for high performance applications such as networking and high-end imaging.

The 80960CA includes a 1 Kbyte, two-way set associative instruction cache and 1 Kbyte of on-chip data RAM. Data RAM is located in the processor's address space from locations 0000.0000H to 0000.03FFH. The CF processor enhances the CA feature set by increasing the instruction cache size to 4 Kbytes, and adding a 1 Kbyte direct-mapped write-through data cache. As with the CA, the CF contains 1 Kbyte of on-chip data RAM located from 0000.0000H to 0000.03FFH.

The upper 16 Mbytes of the address space (FF00.0000H through FFFF.FFFFH) are reserved for implementation-specific functions. In general, an application must not access this space unless specifically required by the implementation. In the case of the CA and CF processors, the application must locate the Initialization Boot Record (IBR) at address FFFF.FF00H.

Integrated peripherals include the Interrupt Controller and Direct Memory Access (DMA) Controller. The DMA peripheral is not available on the 80960Jx and 80960Hx processors.

### 1.1.2 The 80960Jx Processor Family

The 80960Jx family of microprocessors represent the next generation of high-performance, low-cost processors based

on the i960 architecture. 80960Jx processors feature a 32-bit multiplexed address and data bus; the core issues one instruction per clock cycle. The 80960Jx processor family supports 5V and 3.3V operation.

These processors provide a maximum 4 Kbyte, two-way set associative instruction cache, and a maximum 2 Kbyte, direct-mapped write-through data cache. The 80960Jx features 1 Kbyte of on-chip data RAM located from address 0000.0000H to 0000.03FFH.

The upper 16 Mbytes of the address space (FF00.0000H through FFFF.FFFFH) are reserved for implementation-specific functions. In general, an application must not access this space unless specifically required by the implementation. Memory-mapped control registers are located within this address space:

- user/supervisor accessible control registers are located from address FF00.0000H to FF00.7FFFH

- supervisor only accessible control registers from address FF00.8000H to FFFF.FFFH

The application must locate the Initialization Boot Record (IBR) at address FEFF.FF30H.

Integrated peripherals include a 80960Cx-compatible Interrupt Controller, and two 80960Hx-compatible 32-bit timers. The 80960Jx does not implement a DMA peripheral.

### 1.1.3 The 80960Hx Processor Family

The 80960Hx family of microprocessors represent the next generation of very high-performance superscalar processors based on the i960 architecture. 80960Hx processors feature 32-bit demultiplexed address and data buses; the core may issue up to three instructions per clock cycle. The 80960Hx processor family is fabricated on a 3.3V process. All internal logic and memories operate at 3.3V; however, the pad-ring may be biased at 5V, meaning that the 80960Hx can operate in a 5V system. To do so, the system must provide a low-current 5V supply to bias the I/O buffers. In any case, the system must provide a 3.3V supply.

These processors provide a 16 Kbyte, four-way set associative instruction cache, and 8 Kbyte, four-way set-associative write-through data cache. The 80960Hx includes 2 Kbytes of on-chip data RAM located from address 0000.0000H to 0000.07FFH.

The upper 16 Mbytes of the address space (FF00.0000H through FFFF.FFFFH) are reserved for implementation-specific functions. In general, an application must not access this space unless specifically required by the implementation. Memory-mapped control registers are located within this address space:

- user/supervisor accessible control registers are located from address FF00.0000H to FF00.7FFFH

- supervisor only accessible control registers from address FF00.8000H to FFFF.FFFFH

The application must locate the Initialization Boot Record (IBR) at address FEFF.FF30H.

Integrated peripherals include a 80960Cx-compatible Interrupt Controller, two 80960Jx-compatible 32-bit timers, and the Guarded Memory Unit (GMU). The 80960Hx does not implement a DMA peripheral.

### 2.0 Initialization

This section outlines differences in initialization data structures and initialization procedures of the 80960Cx, 80960Jx, and 80960Hx. Only differences between these processor families are highlighted.

#### 2.1 Initialization Data Structures

This section describes the differences between the necessary initialization data structures. Subsections include Section 2.1.1, Initialization Boot Record (IBR), Section 2.1.2, Processor Control Block (PRCB), Section 2.1.3, Fault Table, Section 2.1.4, Control Table, Section 2.1.5, Arithmetic Control Register Initial Image, and the rest.

### 2.1.1 Initialization Boot Record (IBR)

The 80960Cx, 80960Jx, and 80960Hx share similar initialization mechanisms. All processors fetch an Initialization Boot Record (IBR) from a fixed location in memory. The IBR contains the address of the first instruction to fetch and the pointer to the Processor Control Block (PRCB), which is the same format for all processors. The IBR structure is identical for the 80960Cx, 80960Jx, and 80960Hx, and is given in Figure 1. However, it is important to note that the interpretation of the **InitBusConx** bytes varies across implementations.

#### InitBusConx initializes:

- MCON0 on the 80960Cx

- PMCON14:15 on the 80960Jx

- PMCON15 on the 80960Hx

Figure 1. Initialization Boot Record (IBR) Structure

As indicated in Figure 1, the IBR contains the address of the first instruction to be fetched (**StrtIPx**), and the pointer to the PRCB (**PRCBPtrx**). The IBR also contains the initial bus configuration (**InitBusConx**), and check words for the bus confidence test. The algorithm used for the bus confidence test is identical for all processors.

The 80960Cx locates the IBR structure at address **FFFF.FF00H**; the 80960Jx and 80960Hx locate the IBR

structure at address **FEFF.FF30H**. This was done so that a single boot ROM could hold two separate IBRs; one IBR for the 80960Cx, and one IBR for the 80960Jx or 80960Hx. This scheme works because of the way accesses to system memory are typically performed. Separate IBRs are necessary because of differences in initial register images, interpretation of the **InitBusConx** bytes, and control table structures. To clarify, refer to Figure 2.

Figure 2. Simplified Typical Memory Decoding Logic

As can be seen from the figure above, system designers typically do not decode all high-order address pins when accessing memory. This allows for addresses to be aliased; logically different addresses will access the same physical memory.

Assume that the ROM in the figure above contains 64 Kbytes. In this case, when the 80960Cx accesses its IBR at FFFF.FF00H, address FF00H in the ROM is physically accessed. Likewise, when the 80960Jx or 80960Hx access the IBR at FEFF.FF30H, address FF30H in the ROM is physically accessed. Hence, both IBRs may be conveniently contained in the same ROM device. In the figure above, A24 can be ignored with the same results.

### 2.1.2 Processor Control Block (PRCB)

PRCB structure, illustrated in Figure 3, is identical for the 80960Cx, 80960Jx, and 80960Hx. Even though the PRCB structures are identical, the application designed to accommodate the 80960Cx and 80960Hx can be designed to provide separate control structures for each. This allows the application to define which control structures are common to the 80960Cx and 80960Hx, and which are unique.

Figure 3. Processor Control Block (PRCB) Structure

As shown in Figure 1. Initialization Boot Record (IBR) The fault tables for the 80960Cx, 80960Jx, and 80960Hx Structure, the **PRCBPtr** is found in the IBR. processors are identical, with the exception that the

#### 2.1.3 Fault Table

As indicated in Figure 3, the pointer to the fault table is found in the PRCB at offset 0H and is referred to as **FTB** (fault table base address). It may be initialized to any valid, non-reserved location in memory. The **FTB** points to the beginning of the fault table, which contains entries for the beginning address of each fault handler.

The fault tables for the 80960Cx, 80960Jx, and 80960Hx processors are identical, with the exception that the 80960Hx adds an entry for machine faults and an additional fault sub-type to support the Guarded Memory Unit. Machine faults are generated in response to parity errors. This is illustrated in Figure 4.

Figure 4. 80960Cx 80960Jx, and 80960Hx Fault Table and Fault Table Entries

The fault types and subtypes are summarized for the 80960Cx, 80960Jx, and 80960Hx processors. Each processor's users manual provides information on each fault type.

Table 2. 80960Cx, 80960Jx, and 80960Hx Fault Types and Subtypes

| Fau                | ılt Type                                                   |                                                                      | Fault Subtype                                                                                                     |                                                                                         |  |

|--------------------|------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|

| Number             | Name                                                       | Number/Bit<br>Position                                               | Name/Description                                                                                                  | Fault Record<br>(Hex)                                                                   |  |

| 00H                | Parallel                                                   | 02H through<br>FFH                                                   | 02H through Indicates the number of faults that occur in parallel                                                 |                                                                                         |  |

| 01H                | Trace                                                      | Bit 0<br>Bit 1<br>Bit 2<br>Bit 3<br>Bit 4<br>Bit 5<br>Bit 6<br>Bit 7 | Reserved Instruction Trace Branch Trace Call Trace Return Trace Prereturn Trace Supervisor Trace Breakpoint Trace | XX01 XX02<br>XX01 XX04<br>XX01 XX08<br>XX01 XX10<br>XX01 XX20<br>XX01 XX40<br>XX01 XX80 |  |

| 02H                | Operation                                                  | 01H<br>02H<br>03H<br>04H                                             | Invalid Opcode<br>Unimplemented<br>Unaligned<br>Invalid Operand                                                   | XX02 XX01<br>XX02 XX02<br>XX02 XX03<br>XX02 XX04                                        |  |

| 03H                | Arithmetic 01H Integer Overflow O2H Arithmetic Zero-divide |                                                                      | XX03 XX01<br>XX03 XX02                                                                                            |                                                                                         |  |

| 04H Reserved       |                                                            |                                                                      |                                                                                                                   |                                                                                         |  |

| 05H                | Constraint                                                 | 01H<br>02H                                                           | Constraint Range<br>Privileged                                                                                    | XX05 XX01<br>XX05 XX02                                                                  |  |

| 06H                | Reserved                                                   |                                                                      |                                                                                                                   |                                                                                         |  |

| 07H                | Protection                                                 | Bit 1<br>Bit 5                                                       | Length<br>Bad Access <sup>1</sup>                                                                                 | XX07 XX01<br>XX07 XX20                                                                  |  |

| 08H                | Machine <sup>2</sup>                                       | Bit 1                                                                | Parity Error                                                                                                      | XX08 XX02                                                                               |  |

| 09H                | 09H Reserved                                               |                                                                      |                                                                                                                   |                                                                                         |  |

| 0AH                | Туре                                                       | 01H                                                                  | Type Mismatch                                                                                                     | XX0A XX01                                                                               |  |

| 0BH through<br>0FH | Reserved                                                   |                                                                      |                                                                                                                   |                                                                                         |  |

### NOTES:

- 80960Hx only. Added the Bad Access fault sub-type to support illegal memory accesses detected by the Guarded Memory Unit (GMU).

- 2. 80960Hx only. Added the Machine fault, with the Parity Error fault sub-type due to data parity supported on the 80960Hx data bus.

### 2.1.4 Control Table

As shown in Figure 3, the pointer to the control table is found in the PRCB at offset 4H and is referred to as **CTB** (control table base address). It may be initialized to any valid, non-reserved location in memory. **CTB** points to the beginning of the control table, which contains entries for the initial values of the memory configuration, breakpoint, interrupt control, and additional registers.

The control table for the 80960Cx, 80960Jx, and 80960Hx processors is shown in Table 3 Unique control tables are required for each processor, due to differences in the region and bus control registers. Refer to each processor's users manual for additional details

Table 3. Control Table for the 80960Cx, 80960Jx, and 80960Hx Processors (Sheet 1 of 3)

| Offset    | Description                                                                                                                                                                | Group |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| CTB + 00H | 80960Cx: Instruction Breakpoint 0 (IPB0)<br>80960Jx: Reserved<br>80960Hx: Reserved                                                                                         |       |

| CTB + 04H | 80960Cx: Instruction Breakpoint 1 (IPB1)<br>80960Jx: Reserved<br>80960Hx: Reserved                                                                                         | OH    |

| CTB + 08H | 80960Cx: Data Address Breakpoint 0 (DAB0)<br>80960Jx: Reserved<br>80960Hx: Reserved                                                                                        | — UH  |

| CTB + 0CH | 80960Cx: Data Address Breakpoint 1 (DAB1)<br>80960Jx: Reserved<br>80960Hx: Reserved                                                                                        |       |

| CTB + 10H | 80960Cx: Interrupt Map 0 (IMAP0)<br>80960Jx: Same<br>80960Hx: Same                                                                                                         |       |

| CTB + 14H | 80960Cx: Interrupt Map 1 (IMAP1)<br>80960Jx: Same<br>80960Hx: Same                                                                                                         | 1H    |

| CTB + 18H | 80960Cx: Interrupt Map 2 (IMAP2)<br>80960Jx: Same<br>80960Hx: Same                                                                                                         |       |

| CTB + 1CH | 80960Cx: Interrupt Control (ICON)<br>80960Jx: Same<br>80960Hx: Same                                                                                                        |       |

| CTB + 20H | 80960Cx: Memory Region 0 Configuration (MCON0)<br>80960Jx: Physical Memory Region 0:1 Configuration (PMCON0:1)<br>80960Hx: Physical Memory Region 0 Configuration (PMCON0) |       |

| CTB + 24H | 80960Cx: Memory Region 1 Configuration (MCON1)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 1 Configuration (PMCON1)                       | 2H    |

| CTB + 28H | 80960Cx: Memory Region 2 Configuration (MCON2)<br>80960Jx: Physical Memory Region 2:3 Configuration (PMCON2:3)<br>80960Hx: Physical Memory Region 2 Configuration (PMCON2) | Zn    |

| CTB + 2CH | 80960Cx: Memory Region 3 Configuration (MCON3)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 3 Configuration (PMCON3)                       |       |

Table 3. Control Table for the 80960Cx, 80960Jx, and 80960Hx Processors (Sheet 2 of 3)

| Offset    | Description                                                                                                                                                                        | Group |  |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

| CTB + 30H | 80960Cx: Memory Region 4 Configuration (MCON4)<br>80960Jx: Physical Memory Region 4:5 Configuration (PMCON4:5)<br>80960Hx: Physical Memory Region 4 Configuration (PMCON4)         |       |  |  |

| CTB + 34H | 80960Cx: Memory Region 5 Configuration (MCON5)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 5 Configuration (PMCON5)                               | 3H    |  |  |

| CTB + 38H | 80960Cx: Memory Region 6 Configuration (MCON6)<br>80960Jx: Physical Memory Region 6:7 Configuration (PMCON6:7)<br>80960Hx: Physical Memory Region 6 Configuration (PMCON6)         | 311   |  |  |

| CTB + 3CH | 80960Cx: Memory Region 7 Configuration (MCON7)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 7 Configuration (PMCON7)                               |       |  |  |

| CTB + 40H | 80960Cx: Memory Region 8 Configuration (MCON8)<br>80960Jx: Physical Memory Region 8:9 Configuration (PMCON8:9)<br>80960Hx: Physical Memory Region 8 Configuration (PMCON8)         |       |  |  |

| CTB + 44H | 80960Cx: Memory Region 9 Configuration (MCON9)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 9 Configuration (PMCON9)                               | 4H    |  |  |

| CTB + 48H | 80960Cx: Memory Region 10 Configuration (MCON10)                                                                                                                                   |       |  |  |

| CTB + 4CH | 80960Cx: Memory Region 11 Configuration (MCON11)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 11 Configuration (PMCON11)                           |       |  |  |

| CTB + 50H | 80960Cx: Memory Region 12 Configuration (MCON12)<br>80960Jx: Physical Memory Region 12:13 Configuration (PMCON12:13)<br>80960Hx: Physical Memory Region 12 Configuration (PMCON12) |       |  |  |

| CTB + 54H | 80960Cx: Memory Region 13 Configuration (MCON13)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 13 Configuration (PMCON13)                           | 5H    |  |  |

| CTB + 58H | 80960Cx: Memory Region 14 Configuration (MCON14)<br>80960Jx: Physical Memory Region 14:15 Configuration (PMCON14:15)<br>80960Hx: Physical Memory Region 14 Configuration (PMCON14) | 1 5H  |  |  |

| CTB + 5CH | 80960Cx: Memory Region 15 Configuration (MCON15)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Physical Memory Region 15 Configuration (PMCON15)                           |       |  |  |

| Table 3. | Control | Table for the | 80960Cx, | 80960Jx, | and 80960H | x Processors | (Sheet 3 of 3) |

|----------|---------|---------------|----------|----------|------------|--------------|----------------|

|          |         |               |          |          |            |              |                |

| Offset    | Description                                                                                                                | Group |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-------|--|

| CTB + 60H | 80960Cx: Reserved (initialize to zero)<br>80960Jx: Reserved (initialize to zero)<br>80960Hx: Reserved (initialize to zero) |       |  |

| CTB + 64H | 80960Cx: Breakpoint Control (BPCON)<br>80960Jx: Same<br>80960Hx: Same                                                      | - 6H  |  |

| CTB + 68H | 80960Cx: Trace Controls (TC)<br>80960Jx: Same<br>80960Hx: Same                                                             |       |  |

| CTB + 6CH | 80960Cx: Bus Configuration Control (BCON)<br>80960Jx: Same<br>80960Hx: Same                                                |       |  |

#### NOTES:

- 1. CTB = Control Table Base address, found in the Processor Control Block (PRCB).

- 2. Differences exist between the processors in the format of the IMAPx and ICON registers.

- 3. Differences exist between the processors in the format of the BCON, MCON, and PMCON registers.

Note that MCON0, PMCON14:15, and PMCON15 are initialized from the IBR at reset.

### 2.1.5 Arithmetic Control Register Initial Image

The arithmetic control register (AC) is defined identically for the 80960Cx, 80960Jx, and 80960Hx processors. The AC initial image is programmed in the PRCB at offset 8H, and is shown as **ACInitlm** in Figure 3, Processor Control Block (PRCB) Structure (pg. 6).

### 2.1.6 Fault Configuration Word

The fault configuration word is defined identically for the 80960Cx, 80960Jx, and 80960Hx processors. The fault configuration word is programmed in the PRCB at offset CH, and is shown as **FCW** in Figure 3, Processor Control Block (PRCB) Structure (pg. 6).

### 2.1.7 Interrupt Table

Recall that the pointer to the interrupt table base address is found in the PRCB at offset 10H. The interrupt table base address pointer is identified as **ITB** (interrupt table base address), and may be initialized to any valid, non-reserved location in memory. **ITB** points to the beginning of the interrupt table, which contains entries for the starting addresses (interrupt vectors) of all interrupt service routines.

The formats of the interrupt tables for the 80960Cx, 80960Jx, and 80960Hx processors are identical. Interrupt vectors may be internally cached in on-chip data RAM in the same manner as well. The system may provide unique versions of the interrupt table for the 80960Cx and 80960Hx processors, so that the interrupt enable (**inten**) and disable (**intdis**) instructions may be used, which are not available on the 80960Cx processor.

### 2.1.8 System Procedure Table

As shown in Figure 3, Processor Control Block (PRCB) Structure (pg. 6), the pointer to the system procedure table is found in the PRCB at offset 14H. It is identified as **SPTB** (system procedure table base address), and may be initialized to any valid, non-reserved location in memory. **SPTB** points to the beginning of the system procedure table, which contains entries for the starting addresses system procedures. System procedures may be invoked by executing the call system (**calls**) instruction, or by the fault generator

The system procedure table formats for all three processors are identical.

### 2.1.9 Interrupt Stack Pointer

The interrupt stack pointer is defined identically for all three processors; its initial image is programmed in the PRCB at offset 1CH, and is shown as **ISP** in Figure 3, Processor Control Block (PRCB) Structure (pg. 6).

# 2.1.10 Instruction Cache Configuration Word

The instruction cache configuration word (ICCW) is defined identically for all three processors. The ICCW initial image is programmed in the PRCB at offset 20H, and is shown as **ICCW** in Figure 3.

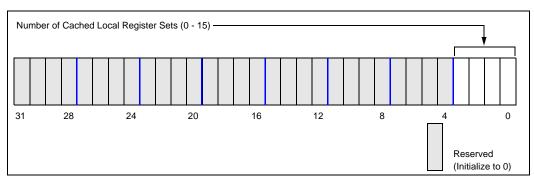

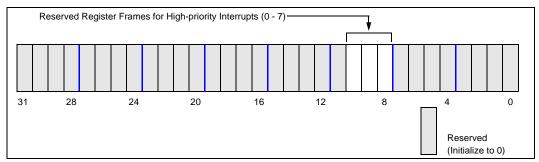

### 2.1.11 Register Cache Configuration Word

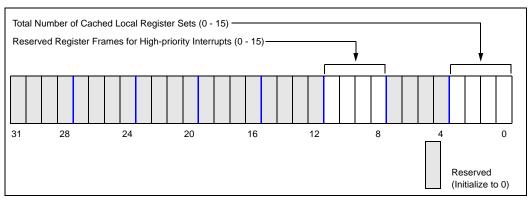

The register cache configuration word (RCCW) initial image is programmed in the PRCB at offset 24H, and is shown as **RCCW** in Figure 3, Processor Control Block (PRCB) Structure (pg. 6). The 80960Jx and 80960Hx processors add additional programmability in addition to

that provided for by the 80960Cx processor, to allow local register frames in the on-chip register cache to be reserved for use by high-priority interrupts. This involves the implementation of bits in the RCCW which are reserved on the 80960Cx processor. However, since the 80960Cx ignores these bits, one value can be programmed in the PRCB which will work properly for all three processors. Refer to section 4.0 Register Cache/Stack Frames, for more information.

# 2.2 Register Values after Reset/Reinitial-

This section describes the values of the architectural state of the 80960Cx, 80960Jx, and 80960Hx processors after hardware reset and software reinitialization.

#### 2.2.1 Common Reset/Reinitialized States

Table 4 shows the inital state values held in common by all three processors after hardware reset and software reinitialization

Table 4. Common State of the i960® Processors after Reset/Reinitialization (Sheet 1 of 2)

| Register                                                   | Value after Hardware Reset        | Value after Software Reinitialization  |

|------------------------------------------------------------|-----------------------------------|----------------------------------------|

| g0                                                         | Device ID                         | Device ID                              |

| AC                                                         | AC initial image at PRCBptr + 8H  | AC initial image at PRCBPtr + 8H       |

| TC                                                         | TC initial image at CTB + 68H     | TC initial image at CTB + 68H          |

| FP (g15)                                                   | ISP (PRCBPtr + 1CH)               | ISP (PRCBPtr + 1CH)                    |

| PFP (r0)                                                   | Undefined                         | Value before Software Reinitialization |

| SP (r1)                                                    | ISP + 40H ([PRCBPtr + 1CH] + 40H) | ISP + 40H ([PRCBPtr + 1CH] + 40H)      |

| RIP (r2)                                                   | Undefined                         | Undefined                              |

| IPND                                                       | Undefined                         | Value before Software Reinitialization |

| IMSK                                                       | 00H                               | 00H                                    |

| IMAP0                                                      | CTB + 10H                         | CTB + 10H                              |

| IMAP1                                                      | CTB + 14H                         | CTB + 14H                              |

| IMAP2                                                      | CTB + 18H                         | CTB + 18H                              |

| ICON                                                       | CTB + 1CH                         | CTB + 1CH                              |

| 80960Cx: MCON0<br>80960Jx: PMCON0:1<br>80960Hx: PMCON0     | CTB + 20H                         | CTB + 20H                              |

| 80960Cx: MCON1<br>80960Hx: PMCON1                          | CTB + 24H                         | CTB + 24H                              |

| 80960Cx: MCON2<br>80960Jx: PMCON2:3<br>80960Hx: PMCON2     | CTB + 28H                         | CTB + 28H                              |

| 80960Cx: MCON3<br>80960Hx: PMCON3                          | CTB + 2CH                         | CTB + 2CH                              |

| 80960Cx: MCON4<br>80960Jx: PMCON4:5<br>80960Hx: PMCON4     | CTB + 30H                         | CTB + 30H                              |

| 80960Cx: MCON5<br>80960Hx: PMCON5                          | CTB + 34H                         | CTB + 34H                              |

| 80960Cx: MCON6<br>80960Jx: PMCON6:7<br>80960Hx: PMCON6     | CTB + 38H                         | CTB + 38H                              |

| 80960Cx: MCON7<br>80960Hx: PMCON7                          | CTB + 3CH                         | CTB + 3CH                              |

| 80960Cx: MCON8<br>80960Jx: PMCON8:9<br>80960Hx: PMCON8     | CTB + 40H                         | CTB + 40H                              |

| 80960Cx: MCON9<br>80960Hx: PMCON9                          | CTB + 44H                         | CTB + 44H                              |

| 80960Cx: MCON10<br>80960Jx: PMCON10:11<br>80960Hx: PMCON10 | CTB + 48H                         | CTB + 48H                              |

Table 4. Common State of the i960® Processors after Reset/Reinitialization (Sheet 2 of 2)

| Register                                                   | Value after Hardware Reset | Value after Software Reinitialization |

|------------------------------------------------------------|----------------------------|---------------------------------------|

| 80960Cx: MCON11<br>80960Hx: PMCON11                        | CTB + 4CH                  | CTB + 4CH                             |

| 80960Cx: MCON12<br>80960Jx: PMCON12:13<br>80960Hx: PMCON12 | CTB + 50H                  | CTB + 50H                             |

| 80960Cx: MCON13<br>80960Hx: PMCON13                        | CTB + 54H                  | CTB + 54H                             |

| 80960Cx: MCON14<br>80960Jx: PMCON14:15<br>80960Hx: PMCON14 | CTB + 58H                  | CTB + 58H                             |

| 80960Cx: MCON15<br>80960Hx: PMCON15                        | CTB + 5CH                  | CTB + 5CH                             |

| BCON                                                       | CTB + 6CH                  | CTB + 6CH                             |

### 2.2.2 Differences in the Reset/Reinitialized State

Table 5 shows the differences in the state of the 80960Cx, 80960Jx, and 80960Hx processors after hardware reset and software reinitialization.

Table 5. Differences in State of the i960<sup>®</sup> Processors after Reset/Reinitialization (Sheet 1 of 2)

| Decistor   | Value after Hardware Reset                                                                   | Value after Software Reinitial-                                        | Processor |    |    |

|------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-----------|----|----|

| Register   | value after hardware Reset                                                                   | ization                                                                |           | Jx | Нх |

| PC         | C01F.2002H                                                                                   | C01F.2002H                                                             | Χ         |    |    |

| PC         | 001F.2002H                                                                                   | 001F.2002H                                                             |           | Х  | Х  |

| DMAC (sf2) | 00H                                                                                          | 00H                                                                    | Х         |    |    |

| CCON (sf2) | TBD <sup>1</sup>                                                                             | TBD <sup>1</sup>                                                       |           |    | Х  |

| BPCON      | CTB + 64H CTB + 64H                                                                          |                                                                        | Х         |    |    |

| BPCON      | 0000.0000H                                                                                   | 0000.0000H                                                             |           | Х  | Х  |

| LMARx      | Undefined                                                                                    | Value before Software Reinitialization                                 |           | Х  | Х  |

| LMMRx      | Bit 0 = 0; bits 1 - 31 = undefined                                                           | Bit 0 = 0; bits 1 - 31 = undefined $^{3}$                              |           | Х  | Х  |

| DLMCON     | Bit 0 = bit 7 of byte <b>InitBusCon</b> <sub>3</sub> ;<br>bit 1 = 0; bits 2 - 31 = undefined | Bit 0 = value before warm reset;<br>bit 1 = 0; bits 2 - 31 = undefined |           |    | Х  |

| TRRx       | Undefined                                                                                    | Value before software reinitial-<br>ization                            | х х       |    | Х  |

| TCRx       | Undefined                                                                                    | Value before software reinitial-<br>ization                            | X X       |    | Х  |

| TMRx       | Bits 1 - 6 = 0; bits 0, 7 - 31 = undefined <sup>2</sup>                                      | = Bits 1 - 6 = 0; bits 0, 7 - 31 = undefined <sup>2</sup>              |           | Х  | Х  |

Table 5. Differences in State of the i960<sup>®</sup> Processors after Reset/Reinitialization (Sheet 2 of 2)

| Dominton                 | Value after Handware Proof              | Value after Software Reinitial-             | Processor |    |    |

|--------------------------|-----------------------------------------|---------------------------------------------|-----------|----|----|

| Register                 | Value after Hardware Reset              | ization                                     | Сх        | Jx | Нх |

| GCR (sf4)                | Bits 0 - 7 = 0; bits 8 - 31 = undefined | Bits 0 - 7 = 0; bits 8 - 31 = undefined     | Х         |    | Х  |

| MPAR0 thru<br>MPAR1      | Undefined                               | Value before Software Reinitial-<br>ization |           |    | Х  |

| MPMR0 thru<br>MPMR1      | Undefined                               | Value before Software Reinitial-<br>ization |           |    | Х  |

| MDUB0 thru<br>MDUB5      | Undefined                               | Value before Software Reinitial-<br>ization |           | Х  |    |

| MDLB0 thru<br>MDLB5      | Undefined                               | Value before Software Reinitial-<br>ization |           |    | Х  |

| IDDO                     | CTB + 00H                               | CTB + 00H                                   | Х         |    |    |

| IPB0                     | 0000.0000H                              | 0000.0000H                                  |           | Х  | Х  |

| IPB1 CTB + 04H CTB + 04H |                                         | CTB + 04H                                   | Χ         |    |    |

| IPBI                     | 0000.0000H                              | 0000.0000H                                  |           | Х  | Х  |

| DADO                     | CTB + 08H                               | CTB + 08H                                   | Χ         |    |    |

| DAB0                     | 0000.0000H                              | 0000.0000H                                  |           | Х  | Х  |

| DAB1                     | CTB + 0CH                               | CTB + 0CH                                   | Χ         |    |    |

| DABI                     | 0000.0000                               | 0000.0000H                                  |           | Х  | Х  |

| IPB2 thru IPB5           | 0000.0000H                              | Value before Software Reinitial-<br>ization | х         |    | Х  |

| DAB2 thru<br>DAB5        | 0000.0000H                              | Value before Software Reinitial-<br>ization |           |    | Х  |

| XBPCON                   | 0000.0000H                              | Value before Software Reinitial-<br>ization |           |    | Х  |

| DEVICEID                 | Device Identification                   | Device Identification                       |           | Х  | Х  |

### NOTES:

- 1. Bit 31 = 1, all others = 0

- 2. Bits 1-5 = 0, bits 0, 6-31 = undefined

- 3. LMMRx retains value (Jx only) otherwise, bit 0 = 0, bits 1-31 = undefined

### 2.3 Initial Bus Configuration

As indicated in Figure 1, Initialization Boot Record (IBR) Structure, The **InitBusConx** bytes are used for the initial configuration of the bus controller. These bytes configure the bus controller during the interim period from the beginning of initialization until the remainder of the configuration data structures are loaded from external memory to fully configure the bus controller. Each processor uses these bytes to initialize the appropriate memory control register. Since each processor has unique memory control register formats, these bytes are interpreted differently for each processor. For more information on memory control, refer to Section 2.3.4, External Bus Configuration.

### 2.3.1 80960Cx Processor

The first four words of the IBR are fetched from memory with the most relaxed bus parameters, specifically:

- Non-burst

- · Non-pipelined

- · Ready disabled

- 8-bit bus width

- Little endian byte order

- $N_{RAD} = 31$

- $N_{RDD} = 3$

- $N_{WAD} = 31$

- $N_{WDD} = 3$

- N<sub>XDA</sub> = 3

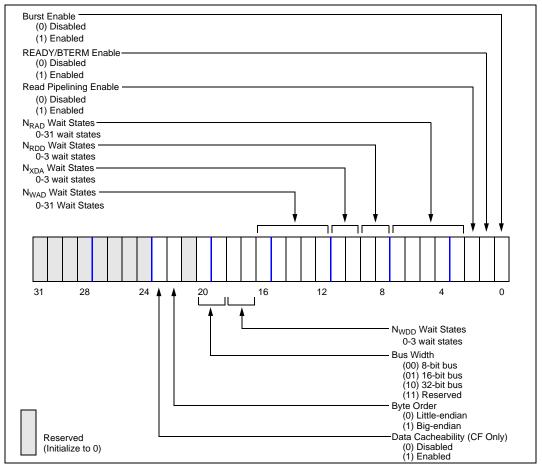

The 80960Cx provides memory control with 16 Memory Control registers, named MCON15:0. The MCON registers define the physical attributes of the external memory system: wait state profiles, bus width, pipelining, bursting, READY enable, etc. MCON0 controls external accesses to addresses 0000.0000H through 0FFF.FFFFH, MCON1 controls accesses 1000.0000H through 1FFF.FFFFH, and so forth. In this manner, the MCON registers control 256 Mbyte regions of memory. The bus controller interface is discussed in further detail in Section 2.3.4.1, External Memory Configuration on the 80960Cx Processor.

As the first four words of the IBR are read from external memory, the low-order byte from each word is loaded into MCON0. The exact order in which these words are read is implementation dependent. This means that **InitBusCon0** is loaded into MCON0<sub>0</sub>, **InitBusCon1** into MCON0<sub>1</sub>, and so forth. The most significant byte of all MCONx registers

is reserved, and must be programmed to zero (InitBusCon3 must be zero). Once MCON0 is configured, all subsequent external bus accesses are controlled by this register until the remaining MCONx and Bus Control (BCON) registers are configured. After the MCONx registers are configured, they are marked valid and then control accesses to their respective memory regions.

Typically, the IBR is located in ROM memory; MCON0 is initially loaded with the appropriate parameters to access this memory.

### 2.3.2 80960Jx Processor

The first four words of the IBR are fetched from memory with the most relaxed bus parameters, specifically:

8-bit bus width

Since there is no internal wait state generator on the 80960Jx, the external memory system must return  $\overline{READY}$  as appropriate.

The 80960Jx allows enhanced memory control by providing eight Physical Memory Control registers (PMCONx:x+1), two Logical Memory Control register pairs (LMCONx), and the Default Logical Memory Control register (DLMCON). The PMCONx:x+1 registers define the bus width of the external memory system. The LMCONx register pairs define the logical characteristics of the external memory system which, in the case of the 80960Jx, is simply cacheability. The DLMCON register defines the default logical characteristics of the external memory system for addresses not specifically covered by the LMCONx register pairs. This means that the DLMCON register controls the default cacheability characteristic of external memory, as well as the globally controlling byte order (big- or little-endian). Byte order on the 80960Jx cannot be controlled by LMCONx register pairs on a region-by-region basis; the memory space is uniformly bigor little-endian.

PMCON0:1 controls the bus width for external accesses to addresses **0000.0000H** through **1FFF.FFFFH**, PMCON2:3 controls accesses **2000.0000H** through **3FFF.FFFFH**, and so forth. In this manner, the PMCONx:x+1 registers control 512 Mbyte regions of memory. The LMCON registers may be programmed to control a variable range of addresses. The bus controller interface is discussed in further detail in Section 2.3.4.2, External Memory Configuration on the 80960Jx Processor.

As the first four words of the IBR are read from external memory, the low-order byte from each word is loaded into memory configuration register 14:15 (PMCON14:15). The exact order in which these words are read is implementation dependent. This means that **InitBusCon0** is loaded into PMCON14:15<sub>0</sub>, **InitBusCon1** into PMCON14:15<sub>1</sub>, and so forth. Once PMCON14:15 is configured, all subsequent external bus accesses are controlled by this register until the remaining PMCONx:x+1 and Bus Control (BCON) registers are initialized. After the PMCONx:x+1 registers are initialized, they are marked valid and then control accesses to their respective memory regions. Bit 7 of **InitBusCon3** is loaded into bit 0 of the DLMCON register; this bit controls data endianess for the entire 32-bit memory space.

Typically, the IBR is located in ROM memory, and PMCON14:15 is initially loaded with the appropriate parameters to access this memory. Note that PMCON14:15 is initialized first from the IBR, as opposed to PMCON0:1 (or as MCON0 is on the 80960Cx). This makes sense since the IBR is fixed in memory region 15; accesses to this memory region are normally controlled by PMCON14:15, not PMCON0:1. On the 80960Cx, system programmers were often required to reconfigure MCON0 (which controls memory region zero) if the memory profile for this region did not match that of memory region 15.

### 2.3.3 80960Hx Processor

The first four words of the IBR are fetched from memory with the most relaxed bus parameters:

- Non-burst

- · Non-pipelined

- · Ready disabled

- 8-bit bus width

- · Little endian byte order

- $N_{RAD} = 31$

- $N_{RDD} = 3$

- $N_{WAD} = 31$

- $N_{WDD} = 3$

- N<sub>XDA</sub> = 15

The possible number of  $N_{XDA}$  wait states is increased from three on the 80960Cx, to fifteen on the 80960Hx.

The 80960Hx allows enhanced memory control by providing:

- 16 Physical Memory Control registers (PMCONx)

- 15 Logical Memory Control register pairs (LMCONx)

- Default Logical Memory Control register (DLMCON)

The PMCONx registers define the physical attributes of the external memory system: wait state profiles, parity, bus width, pipelining, bursting, READY enable, etc. The LMCONx register pairs define the logical characteristics of the external memory system: data endianess, data cache independently invalidatable regions, and cacheability. The DLMCON register defines the default logical characteristics of the memory system for addresses not specifically covered by the LMCONx register pairs.

PMCON0 controls external accesses to addresses 0000.0000H through 0FFF.FFFFH, PMCON1 controls accesses 1000.0000H through 1FFF.FFFFH, and so forth. In this manner, the PMCONx registers control 256 Mbyte regions of memory. The LMCONx register pairs may be programmed to control a variable range of addresses. PMCON registers (80960Hx) and MCON registers (80960Cx) are roughly analogous in functionality, if the endianess and cacheability bits are ignored. The bus controller interface is discussed in further detail in Section 2.3.4.3, External Memory Configuration on the 80960Hx Processor

As the first four words of the IBR are successively read from external memory, the low-order byte from each word of the IBR is successively loaded into each byte of Memory Configuration register 15 (PMCON15). This means that PMCON15<sub>0</sub>, InitBusCon0 loaded into gets InitBusCon1 into PMCON151, and so forth. Once PMCON15 is configured, all subsequent external bus accesses are controlled by this register until the remaining PMCONx and Bus Control (BCON) registers are initialized. After all PMCONx registers are initialized, they are marked valid and then control accesses to their respective memory regions.

Typically, the IBR is located in ROM memory, and PMCON15 is initially loaded with the appropriate parameters to access this memory. Note that PMCON15 is initialized first from the IBR, as opposed to PMCON0 (or as MCON0 is on the 80960Cx). This makes sense since the IBR is fixed in memory region 15; accesses to this memory region are normally controlled by PMCON15, not PMCON0. On the 80960Cx, system programmers were often required to reconfigure MCON0 (which controls

memory region zero) if the memory profile for this region 2.3.4.1 External Memory Configuration on did not match that of memory region 15.

#### 2.3.4 **External Bus Configuration**

This section describes differences in the external bus configuration of the 80960Cx, 80960Jx, and 80960Hx processors. Specifically, this section outlines the differences in programming the Memory Region Configuration (MCON), Physical Memory Region Configuration (PMCON), Logical Memory Template Address (LMAR), Logical Memory Template Mask (LMMR), Default Logical Memory Configuration (DLMCON), and Bus Control (BCON) registers.

# the 80960Cx Processor

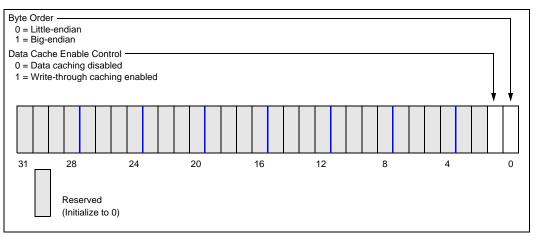

The 80960Cx processor's MCON registers define the physical nature of the memory system (wait state profile, ready enable, burst, pipeline, bus width), and logical nature (byte order, cacheability - CF only). There are 16 MCON registers, one for each 256-Mbyte physical memory region. These registers are labelled MCON0 through MCON15. The format of the MCON register is shown in Figure 5.

Figure 5. 80960Cx MCON Register Format

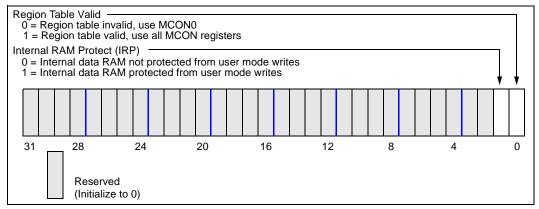

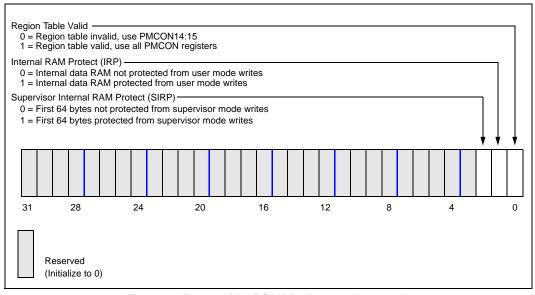

As shown in Figure 6, The Bus Control Register (BCON) mainly serves to validate the values stored in the MCON registers (region table). Immediately after a hardware reset, the region table is marked invalid in the BCON register. Whenever the region table is marked invalid in the BCON register (bit  $0 = bit\ 0$ ), the Bus Control Unit (BCU) uses the

physical memory parameters found in MCON0 for accesses to all regions (Recall that MCON0 is initialized from data found in the IBR). Once the entire region table is loaded by reset microcode, the region table is marked valid in the BCON register (bit 0 = 1), and the BCU uses the appropriate user programmed values.

Figure 6. 80960Cx BCON Register

# 2.3.4.2 External Memory Configuration on the 80960Jx Processor

Control of physical and logical memory characteristics is divided among several registers on the 80960Jx:

- Physical Memory Region Control (PMCON)

- Logical Memory Template Address (LMAR)

- Logical Memory Template Mask (LMMR)

- Default Logical Memory Configuration (DLMCON) registers

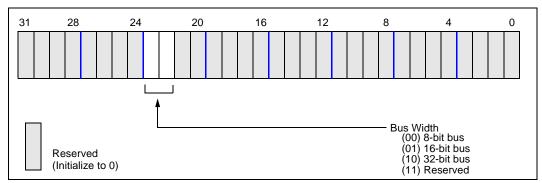

There are eight PMCON registers, one for each 512 Mbyte physical memory region on the 80960Jx (PMCON0:1 through PMCON14:15). There are two pairs of LMAR/LMMR registers (LMAR0, LMAR1, LMMR0, LMMR1), and one DLMCON register.

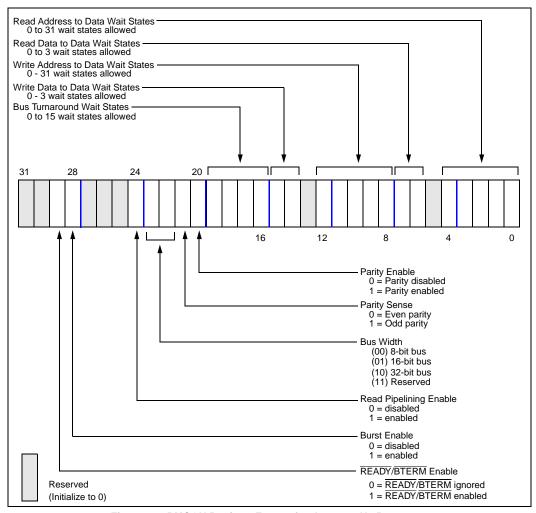

PMCON registers control the bus width on the 80960Jx processor. This is shown in Figure 7.

Figure 7. PMCON Register Format for the 80960Jx Processor

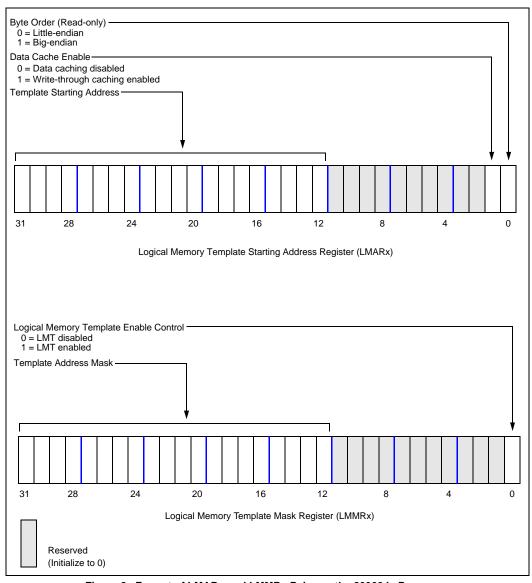

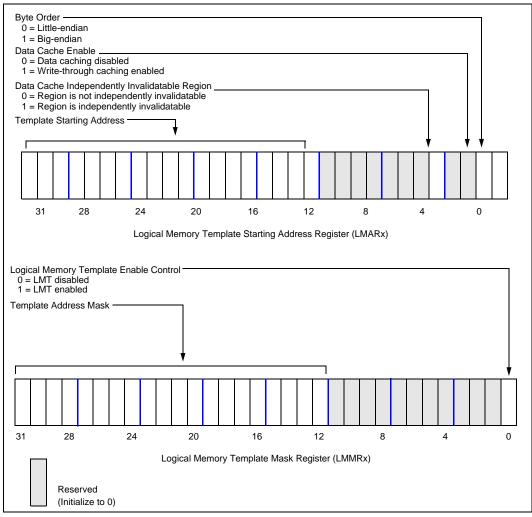

Logical memory control registers (LMARx and LMMRx)

inform the processor logical attributes of external memory.

On the 80960Jx, the only logical attribute controlled by logical memory register pairs is data cacheability. The loworder bit LMARx registers reflects the state byte-order control bit present in DLMCON. In the LMARx registers, this is a read only bit. In other words, the 80960Jx does not support multiple byte-order profiles by logical region; it implements only a homogeneous model. The entire memory map is either big-endian or little-endian.

Logical memory regions are created using the LMAR/LMMR register pair. Either:

- LMAR contains a starting address (4 Kbyte granularity), against which all external accesses are compared, or

- LMMR contains a mask, which indicates which address bits in LMAR are actually compared (compare under mask).

In this manner, one register pair can be used to create multiple logical regions, aliased on an arbitrary power-of-two boundary, by making some combination of upper memory bits "don't care." The format of the LMAR and LMMR registers is shown in Figure 8.

Figure 8. Format of LMARx and LMMRx Pairs on the 80960Jx Processor

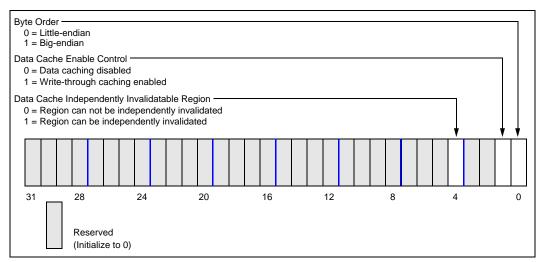

The Default Logical Memory Configuration Register (DLMCON) provides default logical memory control for those accesses which do not fall within a region defined by the logical memory control register pairs. Logical attributes controlled by the DLMCON include data caching enable

and byte ordering. On the 80960Jx, the byte order programmed in the DLMCON register controls byte ordering for the entire 32-bit memory space. The format of the DLMCON is illustrated in Figure 9.

Figure 9. Format of the DLMCON Register on the 80960Jx

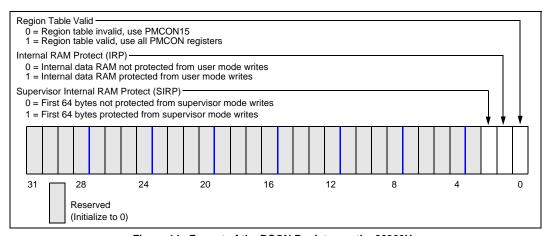

The Bus Control Register (BCON) mainly serves to validate the values stored in the PMCON registers (region table). Immediately after a hardware reset, the region table is marked invalid in the BCON register (bit 0 =0). Whenever the region table is marked invalid in the BCON register, the Bus Control Unit (BCU) uses the physical memory parameters found in PMCON14:15 for accesses to all regions (recall that PMCON14:15 is initialized from data found in the IBR). Once the entire region table is loaded by

reset microcode, the region table is marked valid in the BCON register (bit 0=1), and the BCU uses the appropriate user programmed values. The BCON register format is presented in Figure 10.

Figure 10. Format of the BCON Register on the 80960Jx

# 2.3.4.3 External Memory Configuration on the 80960Hx Processor

Control of physical and logical memory characteristics is divided among several registers on the 80960 Hx:

- Physical Memory Region Control (PMCON)

- Logical Memory Template Address (LMAR)

- Logical Memory Template Mask (LMMR)

- Default Logical Memory Configuration (DLMCON) registers

There are sixteen PMCON registers, one for each 256 Mbyte physical memory region on the 80960Hx (PMCON0 through PMCON15). There are fifteen pairs of LMAR/LMMR registers (LMAR0/LMMR0 through LMAR14/LMMR14), and one DLMCON register.

PMCON registers define the following physical memory attributes for the 80960Hx.

- · Read Address to Data Wait States

- Read Data to Data Wait States

- · Write Address to Data Wait States

- · Write Data to Data Wait States

- Bus Turnaround Wait States

- Data Bus Parity

- Parity Sense

- Bus Width

- Read Pipelining

- Burst Enable

- READY/BTERM Enable

Note that this is a superset of the control found in 80960Cx MCON registers. Also note that the format for the PMCON registers of the 80960Jx and 80960Hx match; 80960Jx PMCON registers select only bus width, but the bit positions are the same.

The PMCON register format is shown in Figure 11.

Figure 11. PMCON Register Format for the 80960Hx Processor

Logical memory control registers (LMARx and LMMRx) inform the processor of the logical attributes of external memory. On the 80960Hx, these registers control byte ordering, data caching, and regions to be marked for quick invalidation in the data cache. Lines in the data cache filled from a "quick invalidation" region may be invalidated by executing the Data Cache Control (dcctl) instruction, without invalidating the entire cache. Note that byte ordering is controlled by logical region on the 80960Hx; the 80960Jx supports only global byte ordering.

Logical memory regions are created using the LMAR/LMMR register pair. LMAR contains a starting address (4 Kbyte granularity), against which all external accesses are compared. LMMR contains a mask, which indicates which address bits in LMAR are actually compared (compare under mask). In this manner, one register pair may be used to create multiple logical regions, aliased on an arbitrary power-of-two boundary, by making some combination of upper memory bits "don't care." LMAR and LMMR register formats are shown in Figure 12.

Figure 12. LMARx and LMMRx Registers on the 80960Hx Processor (LMCONx Pair)