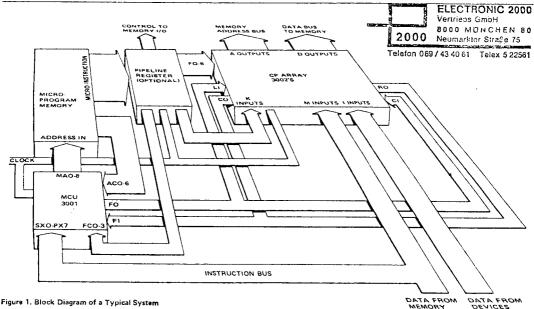

# The INTEL Bipolar Microcomputer Set is a family of Schottky bipolar LSI circuits which simplify the construction of microprogrammed central processors and device controllers. These processors and controllers are truly microprogrammed in the sense that their control logic is organized around a separate read-only memory called the microprogram memory. Control signals for the various processing elements are generated by the microinstructions contained in the microprogram memory. In the implementation of a typical central processor, as shown

below, the microprogram interprets

found in a small computer. For device

controllers, the microprograms directly

a higher level of instructions called

macroinstructions, similar to those

implement the required control

functions.

# SCHOTTKY **BIPOLAR LSI MICROCOMPUTER** SFT

# 3001 **MICROPROGRAM** CONTROL UNIT

The INTEL 3001 Microprogram Control Unit (MCU) controls the sequence in which microinstructions are fetched from the microprogram memory. Its functions include the following:

Maintenance of the microprogram address register.

Selection of the next microinstruction based on the contents of the microprogram address register.

Decoding and testing of data supplied via several input busses to determine the microinstruction execution sequence.

Saving and testing of carry output data from the central processor (CP) array.

Control of carry/shift input data to the CP array.

Control of microprogram interrupts.

High Performance - 85 ns Cycle Time

TTL and DTL Compatible Fully Buffered Three-State and Open Collector Outputs

Direct Addressing of Standard Bipolar PROM or ROM

512 Microinstruction Addressability

Advanced Organization

9-Bit Microprogram Address Register and Bus

4-Bit Program Latch Two Flag Registers

Eleven Address Control Functions Three Jump and Test Latch

Functions

16-way Jump and Test Instruction **Bus Function**

Eight Flag Control Functions Four Flag Input Functions Four Flag Output Functions 40 Pin DIP

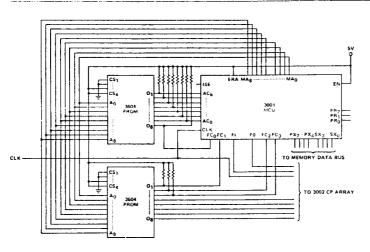

Other members of the INTEL Bipolar Microcomputer Set:

3002 Central Processing Element 3003 Look-Ahead Carry Generator 3212 Multi-Mode Latch Buffer

3214 Priority Interrupt Control Unit 3226 Inverting Bi-Directional Bus Driver 3301 Schottky Bipolar ROM (256 x 4)

3304A Schottky Bipolar ROM (512 x 8) 3601 Schottky Bipolar PROM (256 x 4) 3604 Schottky Bipolar PROM (512 x 8)

# PIN DESCRIPTION

| PIN               | SYMBOL                           | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                      | TYPE (1)       |  |  |  |  |  |

|-------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|--|

| 1-4               | PX <sub>4</sub> -PX <sub>7</sub> | Primary Instruction Bus Inputs  Data on the primary instruction bus is tested by the JPX function to determine the next microprogram address.                                                                                                                                                                                          | active LOW     |  |  |  |  |  |

| 5, 6, 8, 10       | SX <sub>0</sub> -SX <sub>3</sub> | Secondary Instruction Bus Inputs  Data on the secondary instruction bus is synchronously loaded into the PR-latch while the data on the PX-bus is being tested (JPX). During a subsequent cycle, the contents of the PR-latch may be tested by the JPR, JLL, or JRL functions to determine the next microprogram address.              |                |  |  |  |  |  |

| 7,9,11            | PR <sub>0</sub> -PR <sub>2</sub> | PR-Latch Outputs  The PR-latch outputs are asynchronously enabled by the JCE function.  They can be used to modify microinstructions at the outputs of the microprogram memory or to provide additional control lines.                                                                                                                 | open collector |  |  |  |  |  |

| 12, 13, 15,<br>16 | FC <sub>0</sub> -FC <sub>3</sub> | Flag Logic Control Inputs  The flag logic control inputs are used to cross-switch the flags (C and Z) with the flag logic input (FI) and the flag logic output (FO).                                                                                                                                                                   |                |  |  |  |  |  |

| 14                | FO                               | Flag Logic Output  The outputs of the flags (C and Z) are multiplexed internally to form the common flag logic output. The output may also be forced to a logical 0 or logical 1.                                                                                                                                                      |                |  |  |  |  |  |

| 17                | FI                               | Flag Logic Input  The flag logic input is demultiplexed internally and applied to the inputs of the flags (C and Z). Note: the flag input data is saved in the F-latch when the clock input (CLK) is low.                                                                                                                              | active LOW     |  |  |  |  |  |

| 18                | ISE                              | Interrupt Strobe Enable Output  The interrupt strobe enable output goes to logical 1 when one of the JZR functions are selected (see Functional Description, page 6). It can be used to provide the strobe signal required by the INTEL 3214 Priority Interrupt Control Unit or other interrupt circuits.                              |                |  |  |  |  |  |

| 19                | CLK                              | Clock Input                                                                                                                                                                                                                                                                                                                            |                |  |  |  |  |  |

| 20                | GND                              | Ground                                                                                                                                                                                                                                                                                                                                 |                |  |  |  |  |  |

| 21-24<br>37-39    | AC <sub>0</sub> -AC <sub>6</sub> | Next Address Control Function Inputs All jump functions are selected by these control lines.                                                                                                                                                                                                                                           |                |  |  |  |  |  |

| 25                | EN                               | Enable Input When in the HIGH state, the enable input enables the microprogram address, PR-latch and flag outputs.                                                                                                                                                                                                                     |                |  |  |  |  |  |

| 26-29             | $MA_0-MA_3$                      | Microprogram Column Address Outputs                                                                                                                                                                                                                                                                                                    | three-state    |  |  |  |  |  |

| 30-34             | MA <sub>4</sub> -MA <sub>8</sub> | Microprogram Row Address Outputs                                                                                                                                                                                                                                                                                                       | three-state    |  |  |  |  |  |

| 35                | ERA                              | Enable Row Address Input  When in the LOW state, the enable row address input independently disables the microprogram row address outputs. It can be used with the INTEL 3214 Priority Interrupt Control Unit or other interrupt circuits to facilitate the implementation of priority interrupt systems.                              |                |  |  |  |  |  |

| 36                | LD                               | Microprogram Address Load Input When in the active HIGH state, the microprogram address load input inhibits all jump functions and synchronously loads the data on the instruction busses into the microprogram register. However, it does not inhibit the operation of the PR-latch or the generation of the interrupt strobe enable. |                |  |  |  |  |  |

| 40                | vcc                              | +5 Volt Supply                                                                                                                                                                                                                                                                                                                         |                |  |  |  |  |  |

|                   |                                  |                                                                                                                                                                                                                                                                                                                                        |                |  |  |  |  |  |

#### NOTE:

(1) Active HIGH unless otherwise specified.

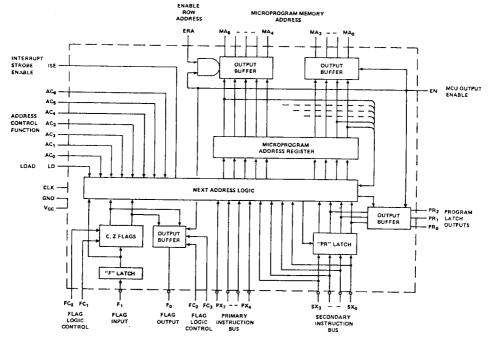

The MCU performs two major control functions. First, it controls the sequence in which microinstructions are fetched from the microprogram memory. For this purpose, the MCU contains a microprogram address register and the associated logic for selecting the next microinstruction address. The second function of the MCU is the control of the two flag flip-flops that are included for interaction with the carry input and carry output logic of the CP array. The logical organization of the MCU is shown in Figure 2.

#### NEXT ADDRESS LOGIC

The next address logic of the MCU provides a set of conditional and unconditional address control functions. These address control functions are used to implement a jump or jump/test operation as part of every microinstruction. That is to say, each microinstruction typically contains a jump operation field that specifies the address control function, and hence, the next microprogram address.

In order to minimize the pin count of the MCU, and reduce the complexity of the next address logic, the microprogram address space is organized as a two dimensional array or matrix. Each microprogram address corresponds to a unit of the matrix at a particular row and column location. Thus, the 9bit microprogram address is treated as specifying not one, but two addresses the row address in the upper five bits and the column address in the lower four bits. The address matrix can therefore contain, at most, 32 row addresses and 16 column addresses for a total of 512 microinstructions.

The next address logic of the MCU makes extensive use of this two component addressing scheme. For example, from a particular row or column address, it is possible to jump unconditionally in one operation anywhere in that row or column. It is not possible, however, to jump anywhere in the address matrix. In fact, for a given location in the matrix, there is a fixed subset of microprogram addresses that may be selected as the next address. These

possible jump target addresses are referred to as a jump set. Each type of MCU address control (jump) function has a jump set associated with it. Appendix C illustrates the jump set for each function.

#### FLAG LOGIC

The flag logic of the MCU provides a set of functions for saving the current value of the carry output of the CP array and for controlling the value of the carry input to the CP array. These two distinct flag control functions are called flag input functions and flag output functions.

The flag logic is comprised of two flip-flops, designated the C-flag and the Z-flag, along with a simple latch, cally the F-latch, that indicates the current state of the carry output line of the CP array. The flag logic is used in conjunction with the carry and shift logic of the CP array to implement a variety of shift/rotate and arithmetic functions.

Figure 2. 3001 Block Diagram

#### ADDRESS CONTROL FUNCTIONS

The address control functions of the MCU are selected by the seven input lines designated ACo-AC6. On the rising edge of the clock, the 9-bit microprogram address generated by the next address logic is loaded into the microprogram address register. The next microprogram address is delivered to the microprogram memory via the nine output lines designated MA<sub>0</sub>-MA<sub>8</sub>. The microprogram address outputs are organized into row and column addresses

> MA8 MA7 MA6 MA5 MA4 row address

> > MA3 MA2 MA1 MA0 column address

Each address control function is specified by a unique encoding of the data on the function input lines. From three to five bits of the data specify the particular function while the remaining bits are used to select part of either the row or column address desired. Function code formats are given in Appendix A. "Address Control Function Summary."

The following is a detailed description of each of the eleven address control functions. The symbols shown below are used throughout the description to specify row and column addresses.

Symbol Meaning

rown

5-bit next row address where n is the decimal row

coln 4-bit next column address where n is the decimal

column address.

#### UNCONDITIONAL ADDRESS CON-TROL (JUMP) FUNCTIONS

The jump functions use the current microprogram address (i.e., the contents of the microprogram address register prior to the rising edge of the clock) and several bits from the address control inputs to generate the next microprogram address.

Mnemonic

JCC

Function Description Jump in current column. ACo-ACa are used to select 1 of 32 row addresses in the current column, specified by

MAn-MA3, as the next address

JZR

Jump to zero row. ACo-AC3 are used to select 1 of 16 column addresses in rowo, as the next address.

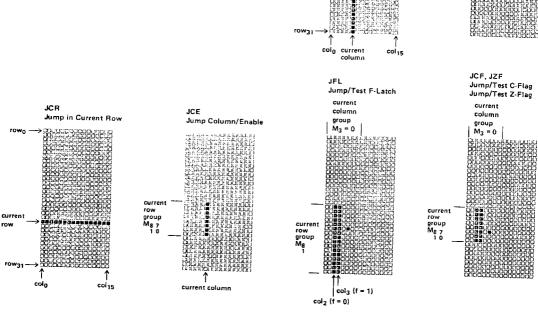

JCR

Jump in current row. AC<sub>0</sub>-AC<sub>3</sub> are used to select 1 of 16 addresses in the current row, specified by MA<sub>4</sub>-MA<sub>8</sub>, as the next address.

JCE

Jump in current column/ row group and enable PR-latch outputs, ACo-AC2 are used to select 1 of 8 row addresses in the current row group, specified by MA7-MA8, as the next row address. The current column is specified by MAn-MA3. The PR-latch outputs are asynchronously enabled.

#### FLAG CONDITIONAL ADDRESS CONTROL (JUMP/TEST) **FUNCTIONS**

The jump/test flag functions use the current microprogram address, the contents of the selected flag or latch, and several bits from the address control function to generate the next microprogram address.

Mnemonic

Function Description

JFL

Jump/test F-Latch. AC0-AC3 are used to select 1 of 16 row addresses in the current row group, specified by MAg, as the next row address. If the current column group, specified by MA3, is colo-col7, the F-latch is used to select colo or colo as the next column address. If MA<sub>3</sub> specifies column group colg-col<sub>15</sub>, the F-latch is used to select col<sub>10</sub> or col<sub>11</sub> as the next column address.

**JCF**

Jump/test C-flag. AC0-AC2 are used to select 1 of 8 row addresses in the current

row group, specified by MA7 and MA8, as the next row address. If the current column group

specified by MA3 is colo-col7, the C-flag is used to select colo or col3 as the next column address. If MA3 specifies column group colg-col15, the C-flag is used to select col<sub>10</sub> or col<sub>11</sub> as the next

JZF

Jump/test Z-flag, Identical to the JCF function described above, except that the Z-flag, rather than the C-flag, is used to select the next column address

column address.

### PX-BUS AND PR-LATCH CONDI-TIONAL ADDRESS CONTROL (JUMP/TEST) FUNCTIONS

The PX-bus jump/test function uses the data on the primary instruction bus (PX4-PX7), the current mircoprogram address, and several selection bits from the address control function to generate the next microprogram address. The PR-latch iump/test functions use the data held in the PR-latch, the current microprogram address, and several selection bits from the address control function to generate the next microprogram address.

Mnemonic

Function Description

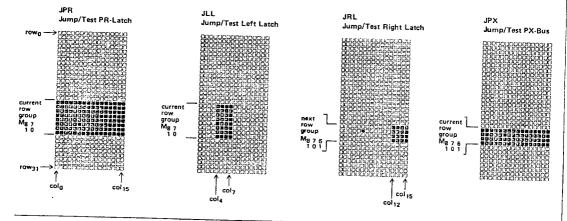

JPR

Jump/test PR-latch. AC0-AC2 are used to select 1 of 8 row addresses in the current row group, specified by MA7 and MA8, as the next row address. The four PR-latch bits are used to select 1 of 16 possible column addresses as the next column address.

Mnemonic

Function Description

JLL

Jump/test leftmost PRlatch bits. ACn-AC2 are used to select 1 of 8 row addresses in the current row group, specified by MA<sub>7</sub> and MA<sub>8</sub>, as the next row address. PR2 and PR3 are used to

select 1 of 4 possible column addresses in cola through col7 as the next column address.

JRL

Jump/test rightmost PRlatch bits. ACn and AC1 are used to select 1 of 4 high-order row addresses in the current row group, specified by MA7 and MA8, as the next row address. PRo and PR1 are used to select 1 of 4 possible column addresses in col<sub>12</sub> through col<sub>15</sub> as the next column address.

Jump/test PX-bus and load PR-latch. ACo and AC<sub>1</sub> are used to select 1 of 4 row addresses in the current row group, specified by MA6-MA8, as the next row address. PXA-PX7 are used to select 1 of 16 possible column addresses as the next column address. SXn-SX3 data is locked in the PR-latch at the rising edge of the clock.

## FLAG CONTROL FUNCTIONS

The flag control functions of the MCU are selected by the four input lines designated FC<sub>0</sub>-FC<sub>3</sub>. Function code formats are given in Appendix B, "Flag Control Function Summary,"

The following is a detailed description of each of the eight flag control functions.

### FLAG INPUT CONTROL FUNCTIONS

The flag input control functions select which flag or flags will be set to the current value of the flag input (FI) line. Data on FI is stored in the F-latch when the clock is low. The content of the Flatch is loaded into the C and/or Z flag on the rising edge of the clock.

| Mnemonic | Function Description                                                                        |

|----------|---------------------------------------------------------------------------------------------|

| SCZ      | Set C-flag and Z-flag to FI. The C-flag and the Z-flag are both set to the value of FI.     |

| STZ      | Set Z-flag to FI. The Z-<br>flag is set to the value of<br>FI. The C-flag is<br>unaffected. |

| STC      | Set C-flag to FI. The C-<br>flag is set to the value of<br>FI. The Z flag is<br>unaffected. |

| HCZ      | Hold C-flag and Z-flag.<br>The values in the C-flag<br>and Z-flag are unaffected.           |

|          |                                                                                             |

#### FLAG OUTPUT CONTROL **FUNCTIONS**

The flag output control functions select the value to which the flag output (FO) line will be forced.

| Mnemonic | Function Description                                    |

|----------|---------------------------------------------------------|

| FF0      | Force FO to 0. FO is forced to the value of logical 0.  |

| FFC      | Force FO to C. FO is forced to the value of the C-flag. |

| FFZ      | Force FO to Z. FO is forced to the value of the Z-flag. |

| FF1      | Force FO to 1. FO is forced to the value of logical 1.  |

#### LOAD AND INTERRUPT STROBE FUNCTIONS

The load function of the MCU is controlled by the input line designated LD. If the LD line is active HIGH at the rising edge of the clock, the data on the primary and secondary instruction busses, PX4-PX7 and SXn-SX3, is loaded into the microprogram address register. PX<sub>4</sub>-PX<sub>7</sub> are loaded into MA<sub>0</sub>-MA<sub>3</sub> and SX<sub>0</sub>-SX<sub>3</sub> are loaded into MA4-MA7. The high-order bit of the microprogram address register MA<sub>8</sub> is set to a logical 0. The bits from the primary instruction bus select 1 of 16 possible column addresses. Likewise. the bits from the secondary instruction bus select 1 of the first 16 row addresses.

The interrupt strobe enable of the MCU is available on the output line design ISE. The line is placed in the active high state whenever a JZR to col<sub>15</sub> is selected as the address control function. Customarily, the start of a macroinstruction fetch sequence is situated at rowo and col<sub>15</sub> so that the INTEL 3214 Priority Interrupt Control Unit may be enabled at the beginning of the fetch/execute cycle. The priority interrupt control unit may respond to the interrupt by pulling the enable row address (ERA) input line down to override the selected next row address from the MCU. Then by gating an alternative next row address on to the row address lines of the microprogram memory, the microprogram may be forced to enter an interrupt handling routine. The alternative row address placed on the microprogram memory address lines does not alt the contents of the microprogram address register. Therefore, subsequent jump functions will utilize the row address in the register, and not the alternative row address, to determine the next microprogram address.

Note, the load function always overrides the address control function on ACo-AC6. It does not, however, override the latch enable or load sub-functions of the JCE or JPX instruction, respectively. In addition, it does not inhibit the interrupt strobe enable or any of the flag control functions.

JPX

## D.C. AND OPERATING CHARACTERISTICS

### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias 0°C to 70°C |

|------------------------------------|

| Storage Temperature                |

| All Output and Supply Voltages     |

| All Input Voltages1.0V to +5.5V    |

| Output Currents                    |

<sup>\*</sup>COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

$T_A = 0^{\circ}C$  to  $70^{\circ}C$

| SYMBOL          | PARAMETER                                                                                                                                      | MIN | TYP <sup>(1)</sup>        | MAX                     | UNIT           | CONDITIONS                                                                                         |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|---------------------------|-------------------------|----------------|----------------------------------------------------------------------------------------------------|

| V <sub>C</sub>  | Input Clamp Voltage (All<br>Input Pins)                                                                                                        |     | -0.8                      | -1.0                    | V              | V <sub>CC</sub> = 4.75V, I <sub>C</sub> = -5 mA                                                    |

| l <sup>E</sup>  | Input Load Current:<br>CLK Input<br>EN Input<br>All Other Inputs                                                                               |     | -0.075<br>-0.05<br>-0.025 | -0.75<br>-0.50<br>-0.25 | mA<br>mA<br>mA | $V_{CC} = 5.25V$ , $V_F = 0.45V$                                                                   |

| I <sub>R</sub>  | Input Leakage Current:<br>CLK<br>EN Input<br>All Other Inputs                                                                                  |     |                           | 120<br>80<br>40         | μΑ<br>μΑ<br>μΑ | V <sub>CC</sub> = 5.25V, V <sub>R</sub> = 5.25V                                                    |

| $V_{iL}$        | Input Low Voltage                                                                                                                              |     |                           | 8.0                     | V              | V <sub>CC</sub> = 5.0V                                                                             |

| ViH             | Input High Voltage                                                                                                                             | 2.0 |                           |                         | V              |                                                                                                    |

| Icc             | Power Supply Current                                                                                                                           |     | 170                       | 240                     | mA             | V <sub>CC</sub> = 5.25V <sup>(2)</sup>                                                             |

| VOL             | Output Low Voltage<br>(All Output Pins)                                                                                                        |     | 0.35                      | 0.45                    | V              | $V_{CC} = 4.75V$ , $I_{OL} = 10 \text{ mA}$                                                        |

| V <sub>OH</sub> | Output High Voltage<br>(MA <sub>0</sub> -MA <sub>8</sub> , ISE, FO)                                                                            | 2.4 | 3.0                       |                         | V              | $V_{CC} = 4.75V$ , $I_{OH} = -1 \text{ mA}$                                                        |

| Ios             | Output Short Circuit Current (MA <sub>0</sub> -MA <sub>8</sub> , ISE, FO)                                                                      | -15 | -28                       | -60                     | mA             | V <sub>CC</sub> = 5.0V                                                                             |

| IO (off)        | Off-State Output Current:<br>PR <sub>0</sub> -PR <sub>2</sub> , MA <sub>0</sub> -MA <sub>2</sub> , FO<br>MA <sub>0</sub> -MA <sub>8</sub> , FO |     |                           | -100<br>100             | μΑ<br>μΑ       | V <sub>CC</sub> = 5.25V, V <sub>O</sub> = 0.45V<br>V <sub>CC</sub> = 5.25V, V <sub>O</sub> = 5.25V |

<sup>(1)</sup> Typical values are for  $T_A=25^{\circ}C$  and nominal supply voltage. (2) EN input grounded, all other inputs and outputs open.

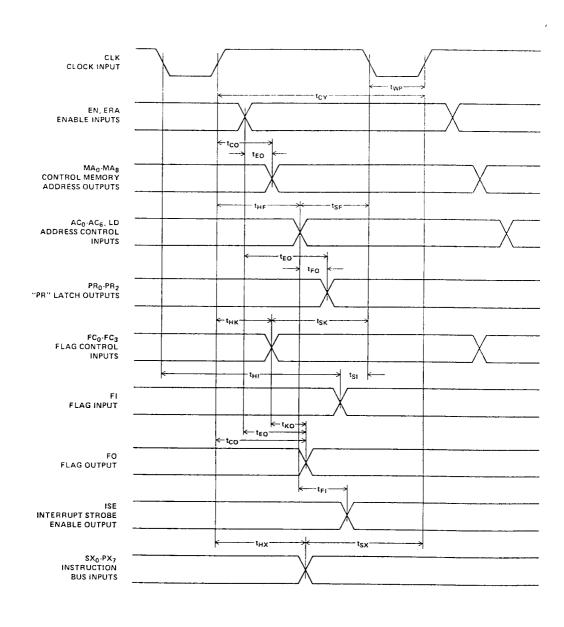

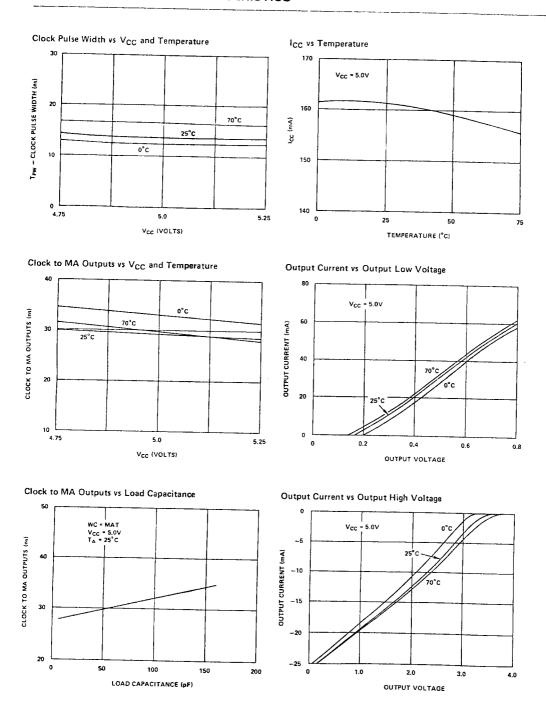

A.C. CHARACTERISTICS AND WAVEFORMS  $T_A$  = 0°C to 70°C,  $V_{CC}$  = 5.0V ±5%

| SYMBOL          | PARAMETER                                                                                                         | MIN      | TYP <sup>(1)</sup> | MAX | UNIT |

|-----------------|-------------------------------------------------------------------------------------------------------------------|----------|--------------------|-----|------|

| $t_{CY}$        | Cycle Time                                                                                                        | 85       | 60                 |     |      |

| t <sub>WP</sub> | Clock Pulse Width                                                                                                 | 30       | 20                 |     | ns   |

|                 | Control and Data Input Set-Up Times:                                                                              |          | 20                 |     | ns   |

| tsr             | LD, AC <sub>0</sub> -AC <sub>6</sub>                                                                              | 10       |                    |     |      |

| tsk             | FC <sub>0</sub> , FC <sub>1</sub>                                                                                 | 0        | 0                  |     | ns   |

| $t_{SX}$        | SX <sub>0</sub> -SX <sub>3</sub> , PX <sub>4</sub> -PX <sub>7</sub>                                               | _        | 0.5                |     | ns   |

| tsı             | FI                                                                                                                | 35<br>15 | 25                 |     | ns   |

|                 | Comments to the second                                                                                            | 15       | 5                  |     | ns   |

| •               | Control and Data Input Hold Times:                                                                                |          |                    |     |      |

| t <sub>HF</sub> | LD, AC <sub>0</sub> -AC <sub>6</sub>                                                                              | 5        | 0                  |     | ns   |

| thk.            | FC <sub>0</sub> , FC <sub>1</sub>                                                                                 | 0        |                    |     | ns   |

| t <sub>HX</sub> | \$X <sub>0</sub> -\$X <sub>3</sub> , PX <sub>4</sub> -PX <sub>7</sub>                                             | 20       | 5                  |     | пѕ   |

| t <sub>HI</sub> | FI                                                                                                                | 20       | 8                  |     | ns   |

| tco             | Propagation Delay from Clock Input (CLK) to Outputs (MA $_0$ -MA $_8$ , FO)                                       |          | 30                 | 45  | ns   |

| t <sub>KO</sub> | Propagation Delay from Control Inputs $FC_2$ and $FC_3$ to Flag Out (FO)                                          |          | 16                 | 30  | ns   |

| t <sub>FO</sub> | Propagation Delay from Control Inputs $AC_0$ - $AC_6$ to Latch Outputs ( $PR_0$ - $PR_2$ )                        |          | 26                 | 40  | ns   |

| t <sub>EO</sub> | Propagation Delay from Enable Inputs EN and ERA to Outputs $(MA_0-MA_8, FO, PR_0-PR_2)$                           |          | 21                 | 32  | ns   |

| t <sub>F1</sub> | Propagation Delay from Control Inputs AC <sub>0</sub> -AC <sub>6</sub> to Interrupt<br>Strobe Enable Output (ISE) |          | 24                 | 40  | ns   |

#### NOTE:

## **TEST CONDITIONS:**

Input pulse amplitude of 2.5 volts.

Input rise and fall times of 5 ns between 1 volt and 2 volts.

Output load of 10 mA and 50 pF.

Speed measurements are taken at the 1.5 volt level.

## TEST LOAD CIRCUIT:

# CAPACITANCE(2) TA = 25°C

| SYMBOL          | PARAMETER                                         | MIN | TYP     | MAX      | UNIT     |

|-----------------|---------------------------------------------------|-----|---------|----------|----------|

| C <sub>IN</sub> | Input Capacitance:<br>CLK, EN<br>All Other Inputs |     | 11<br>5 | 16<br>10 | pF       |

| COUT            | Output Capacitance                                |     | 6       | 12       | pF<br>pF |

#### NOTE:

<sup>(1)</sup> Typical values are for TA = 25°C and nominal supply voltage.

<sup>(2)</sup> This parameter is periodically sampled and is not 100% tested. Condition of measurement is f = 1 MHz,  $V_{BIAS} = 2.5V$ ,  $V_{CC} = 5V$  and  $T_A = 25^{\circ}C$ .

# APPENDIX A ADDRESS CONTROL FUNCTION SUMMARY

| MNEMONIC |                         | FUNCTION        |   |                |                |                |                |                | XT B            | NEXT COL       |                |                |                |                 |                |                |                |

|----------|-------------------------|-----------------|---|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|----------------|

|          | DESCRIPTION             | AC <sub>6</sub> | 5 | 4              | 3              | 2              | 1              | 0              | MA <sub>8</sub> | 7              | 6              | 5              | 4              | MA <sub>3</sub> | 2              | 1              | 0              |

| JCC      | Jump in current column  | 0               | 0 | d <sub>4</sub> | d <sub>3</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | d <sub>4</sub>  | d <sub>3</sub> | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub> | $m_3$           | m <sub>2</sub> | m <sub>1</sub> | mu             |

| JZR      | Jump to zero row        | 0               | 1 | 0              | $d_3$          | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | 0               | 0              | 0              | 0              | 0              | $d_3$           | $d_2$          | d <sub>1</sub> | d <sub>0</sub> |

| JCR      | Jump in current row     | 0               | 1 | 1              | d <sub>3</sub> | d <sub>2</sub> | $d_1$          | d <sub>0</sub> | m <sub>8</sub>  | m <sub>7</sub> | m <sub>6</sub> | m <sub>5</sub> | m <sub>4</sub> | $d_3$           | $d_2$          | d <sub>1</sub> | do             |

| JCE      | Jump in column/enable   | 1               | 1 | 1              | 0              | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub> | mg              | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | $m_3$           | $m_2$          | m <sub>1</sub> | mo             |

| JFL      | Jump/test F-latch       | 1               | 0 | 0              | d <sub>3</sub> | d <sub>2</sub> | d <sub>1</sub> | d <sub>0</sub> | m <sub>8</sub>  | d <sub>3</sub> | $d_2$          | d <sub>1</sub> | ď              | m <sub>3</sub>  | 0              | 1              | ť              |

| JCF      | Jump/test C-flag        | 1               | 0 | 1              | 0              | d <sub>2</sub> | $d_1$          | $d_0$          | m <sub>8</sub>  | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | $d_0$          | $m_3$           | 0              | 1              | С              |

| JZF      | Jump/test Z-flag        | 1               | 0 | 1              | 1              | d <sub>2</sub> | d <sub>1</sub> | ďO             | mg              | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | $d_0$          | $m_3$           | 0              | 1              | z              |

| JPR      | Jump/test PR-latches    | 1               | 1 | 0              | 0              | d <sub>2</sub> | d <sub>1</sub> | do             | m <sub>8</sub>  | m <sub>7</sub> | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | <b>P</b> 3      | p <sub>2</sub> | P1             | P <sub>0</sub> |

| JLL      | Jump/test left PR bits  | 1               | 1 | 0              | 1              | $d_2$          | d <sub>1</sub> | d <sub>0</sub> | m <sub>8</sub>  | m7             | $d_2$          | d <sub>1</sub> | do             | 0               | 1              | Р3             | p <sub>2</sub> |

| JRL      | Jump/test right PR bits | 1               | 1 | 1              | 1              | 1              | d1             | ďo             | m <sub>8</sub>  | m <sub>7</sub> | 1              | d <sub>1</sub> | d <sub>0</sub> | 1               | 1              | Ρį             | P <sub>0</sub> |

| JPX      | Jump/test PX-bus        | 1               | 3 | 1              | 1              | 0              | d <sub>1</sub> | do             | m8              | m7             | m <sub>6</sub> | d <sub>1</sub> | d <sub>0</sub> | ×7              | ×6             | ×5             | Х4             |

| SYMBOL         | MEANING                                              |  |  |  |  |  |  |  |  |

|----------------|------------------------------------------------------|--|--|--|--|--|--|--|--|

| d <sub>n</sub> | Data on address control line n                       |  |  |  |  |  |  |  |  |

| mn             | Data in microprogram address register bit n          |  |  |  |  |  |  |  |  |

| P <sub>n</sub> | Data in PR-latch bit n                               |  |  |  |  |  |  |  |  |

| ×n             | Data on PX-bus line n (active LOW)                   |  |  |  |  |  |  |  |  |

| f, c, z        | Contents of F-latch, C-flag, or Z-flag, respectively |  |  |  |  |  |  |  |  |

# APPENDIX B FLAG CONTROL FUNCTION SUMMARY

| TYPE          | MNEMONIC | DESCRIPTION                | FC <sub>1</sub> | 0 |  |

|---------------|----------|----------------------------|-----------------|---|--|

|               | SCZ      | Set C-flag and Z-flag to f | 0               | 0 |  |

| Flag<br>Input | STZ      | Set Z-flag to f            | 0               | 1 |  |

|               | STC      | Set C-flag to f            | 1               | 0 |  |

|               | HCZ      | Hold C-flag and Z-flag     | 1               | 1 |  |

| TYPE          | MNEMONIC | DESCRIPTION                | FC <sub>3</sub> | 2 |  |

|               | FF0      | Force FO to 0              | 0               | 0 |  |

| Flag          | FFC      | Force FO to C-flag         | 0               | 1 |  |

| Output        | FFZ      | Force FO to Z-flag         | 1               | 0 |  |

|               | FF1      | Force FO to 1              | 1               | 1 |  |

| LOAD<br>FUNCTION |                 | NEX | TRO | w              |                | NEXT COL        |                |    |            |  |  |

|------------------|-----------------|-----|-----|----------------|----------------|-----------------|----------------|----|------------|--|--|

| LD               | MA <sub>8</sub> | 7   | 6   | 5              | 4              | MA <sub>3</sub> | 2              | 1  | 0          |  |  |

| 0                | see Appendix A  |     |     |                |                | see Ap          | pendix         | A  |            |  |  |

| 1                | 0               | x3  | ×2  | x <sub>1</sub> | x <sub>0</sub> | ×7              | × <sub>6</sub> | ×5 | <b>X</b> 4 |  |  |

| SYMBOL | MEANING                                   |

|--------|-------------------------------------------|

| f      | Contents of the F-latch                   |

| ×n     | Data on PX- or SX-bus line n (active LOW) |

|        |                                           |

The following ten diagrams illustrate the jump set for each of the eleven jump and jump/test functions of the MCU. Location 341, indicated by the black square, represents one current row (row<sub>21</sub>) and current column (col<sub>3</sub>) address. The blue boxes indicate the microprogram locations that may be selected by the particular function as the next address.

JCC

Jump in Current Column

JZR

Jump to Zero Row

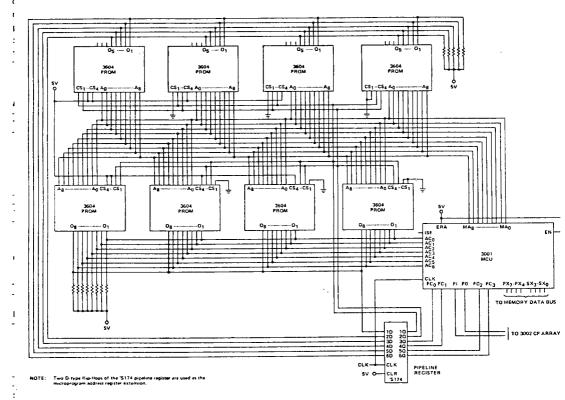

Non-Pipelined Configuration with 512 Microinstruction Addressability

Pipelined Configuration with 2048 Microinstruction Addressability