# IBM PowerPC<sup>®</sup>970FX RISC Microprocessor

# Data Sheet

Preliminary Electrical Information

SA14-2760-07

Version 2.3

# Preliminary

June 4, 2006

© Copyright International Business Machines Corporation 2005, 2006

All Rights Reserved Printed in the United States of America June 2006

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

| 01 00(11.   |                      |

|-------------|----------------------|

| IBM         | IBM Logo             |

| PowerPC     | PowerPC Logo         |

| PowerPC 970 | PowerPC Architecture |

Other company, product and service names may be trademarks or service marks of others.

**Note**: All information contained in this document is subject to change without notice. Verify with your IBM field application enginner that you have the latest version of this document before finalizing a design.

The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties, or give rise to any express or implied warranty. Information contained in this document was obtained in specific environments, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

THE INFORMATION CONTAINED IN THIS DOCUMENT IS PROVIDED ON AN "AS IS" BASIS. In no event will IBM be liable for damages arising directly or indirectly from any use of the information contained in this document.

IBM Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351 The IBM home page can be found at <u>http://www.ibm.com</u>

The IBM Systems and Technology Group's Microelectronics home page can be found at <a href="http://www.ibm.com/chips">http://www.ibm.com/chips</a>

June 4, 2006

| About This Datasheet                                                      | 9    |

|---------------------------------------------------------------------------|------|

| 1. General Information                                                    | 11   |

| 1.1 Description                                                           | . 11 |

| 1.2 Features                                                              | . 11 |

| 1.3 PowerPC 970FX Block Diagram                                           | . 13 |

| 1.4 Ordering and Processor Version Register                               |      |

| 1.4.1 Leaded Package Version                                              |      |

| 1.4.2 Reduced-Lead Package Version                                        |      |

| 2. General Parameters                                                     | 17   |

| 3. Electrical and Thermal Characteristics                                 | 17   |

| 3.1 DC Electrical Characteristics                                         | . 17 |

| 3.1.1 Absolute Maximum Ratings                                            |      |

| 3.1.2 Recommended Operating Conditions                                    |      |

| 3.1.3 Package Thermal Characteristics                                     |      |

| 3.1.4 DC Electrical Specifications                                        |      |

| 3.1.5 Power Consumption                                                   |      |

| 3.2 AC Electrical Characteristics                                         |      |

| 3.3 Clock AC Specifications                                               |      |

| 3.4 Processor-Clock Timing Relationship Between PSYNC and SYSCLK          |      |

| 3.5 Processor Interconnect Specifications                                 |      |

| 3.5.1 Electrical and Physical Specifications                              |      |

| 3.5.1.1 Source Synchronous Bus (SSB)                                      |      |

| 3.5.1.2 Drive Side Characteristics                                        |      |

| 3.5.1.3 Module-to-Module Interconnect Characteristics                     |      |

| 3.5.1.4 Receive Side Characteristics                                      |      |

| 3.6 Input AC Specifications                                               |      |

| 3.6.1 TBEN Input Pin                                                      |      |

| •                                                                         |      |

| 3.7 Asynchronous Output Specifications                                    |      |

| 3.8 Mode Select Input Timing Specifications                               |      |

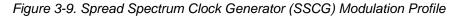

| 3.9 Spread Spectrum Clock Generator (SSCG)                                |      |

| 3.9.1 Design Considerations                                               |      |

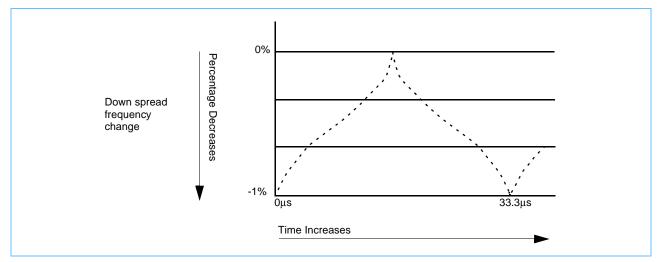

| 3.10 I <sup>2</sup> C and JTAG                                            |      |

| 3.10.1 I <sup>2</sup> C Bus Timing Information                            |      |

| 3.10.2 IEEE 1149.1 AC Timing Specifications                               |      |

| 3.10.3 I2C and JTAG Considerations                                        |      |

| 3.10.4 Boundary Scan Considerations                                       | . 39 |

| 4. PowerPC 970FX Microprocessor Dimension and Physical Signal Assignments |      |

| 4.1 ESD Considerations                                                    |      |

| 4.2 Mechanical Packaging                                                  |      |

| 4.2.1 Leaded Package Version                                              | . 40 |

| 4.2.2 Reduced-Lead Package Version                                        |      |

| 4.2.2.1 Mechanical Specifications                                         |      |

| 4.2.2.2 Assembly Considerations                                           | . 44 |

| Data Sheet  |    |

|-------------|----|

| PowerPC 970 | FΧ |

| 4.3 PowerPC 970FX Microprocessor Pinout Listings          | . 50 |

|-----------------------------------------------------------|------|

| 5. System Design Information                              |      |

| 5.1 External Resistors                                    |      |

| 5.2 PLL Configuration                                     | . 57 |

| 5.2.1 Determining PLLMULT and BUS_CFG Settings            | . 57 |

| 5.2.2 PLL_RANGE Configuration                             | . 58 |

| 5.3 PLL Power Supply Filtering                            | . 60 |

| 5.4 Decoupling Recommendations                            |      |

| 5.4.1 Using the KVPRBVDD and KVPRBGND Pins                | . 61 |

| 5.5 Decoupling Layout Guide                               |      |

| 5.6 Input-Output Usage                                    | . 65 |

| 5.6.1 Chip Signal I/O and Test Pins                       |      |

| 5.7 Thermal Management Information                        | . 69 |

| 5.7.1 Thermal Management pins                             | . 69 |

| 5.7.2 Reading Thermal Diode Calibration data via JTAG     | . 69 |

| 5.7.3 Heatsink Attachment and Mounting Forces             | . 71 |

| 5.8 Operational and Design Considerations                 | . 72 |

| 5.8.1 Power-On Reset Considerations                       |      |

| 5.8.2 Debugging PowerPC 970FX Power-On and Reset Sequence | . 72 |

| 5.8.3 I <sup>2</sup> C Addressing of PowerPC 970FX        |      |

| Revision Log                                              | 73   |

| Figure 1-1. PPC 970FX Block Diagram                                                                 | 13             |

|-----------------------------------------------------------------------------------------------------|----------------|

| Figure 1-2. Part Number Legend                                                                      |                |

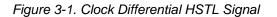

| Figure 3-1. Clock Differential HSTL Signal                                                          |                |

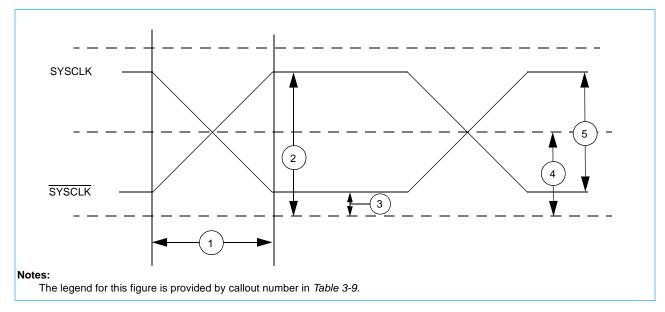

| Figure 3-2. Processor-Clock Timing Relationship Between PSYNC and SYSCLK                            |                |

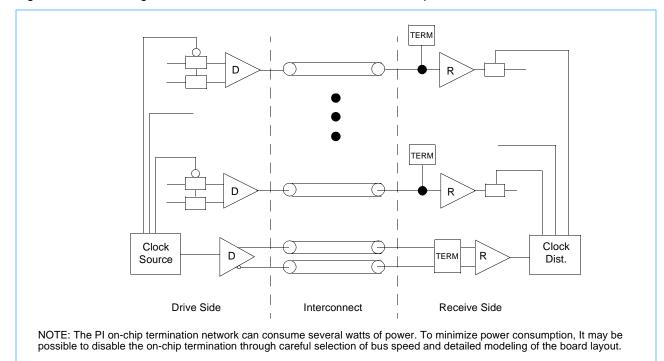

| Figure 3-3. Block Diagram of an SSB for a Processor Interconnect Implementation                     |                |

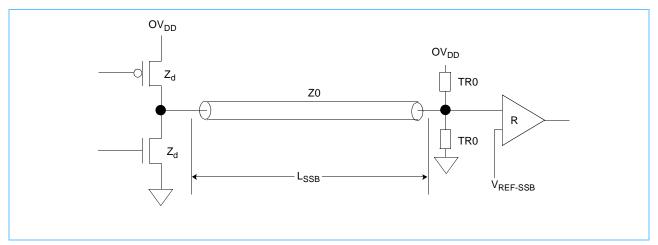

| Figure 3-4. Typical Implementation for a Single-ended Line                                          |                |

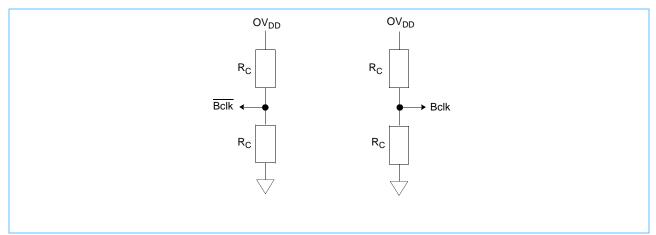

| Figure 3-5. Differential Clock Termination Circuitry                                                |                |

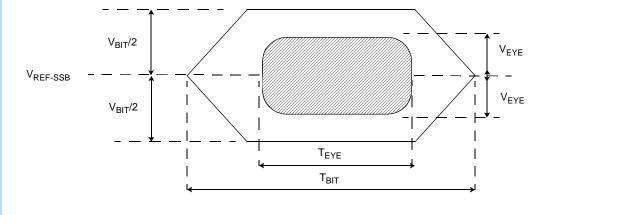

| Figure 3-6. Post-IAP Eye Opening                                                                    |                |

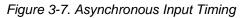

| Figure 3-7. Asynchronous Input Timing                                                               |                |

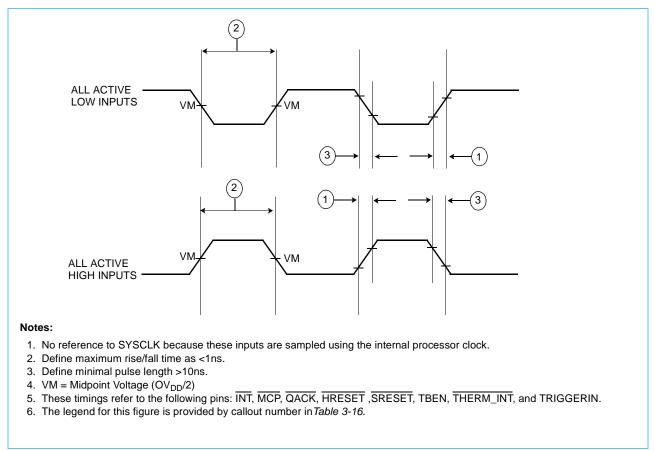

| Figure 3-8. HRESET and BYPASS Timing Diagram                                                        |                |

| Figure 3-9. Spread Spectrum Clock Generator (SSCG) Modulation Profile                               |                |

| Figure 3-10. JTAG Clock Input Timing Diagram                                                        |                |

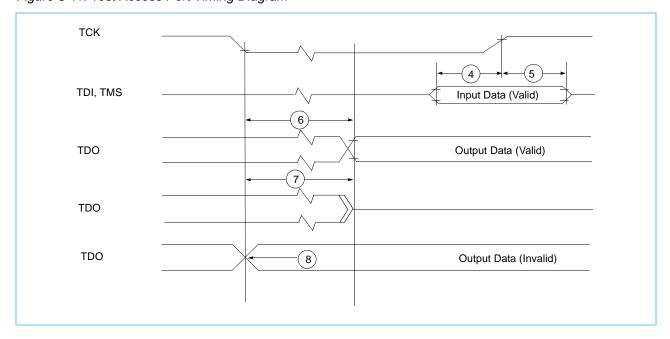

| Figure 3-11. Test Access Port Timing Diagram                                                        |                |

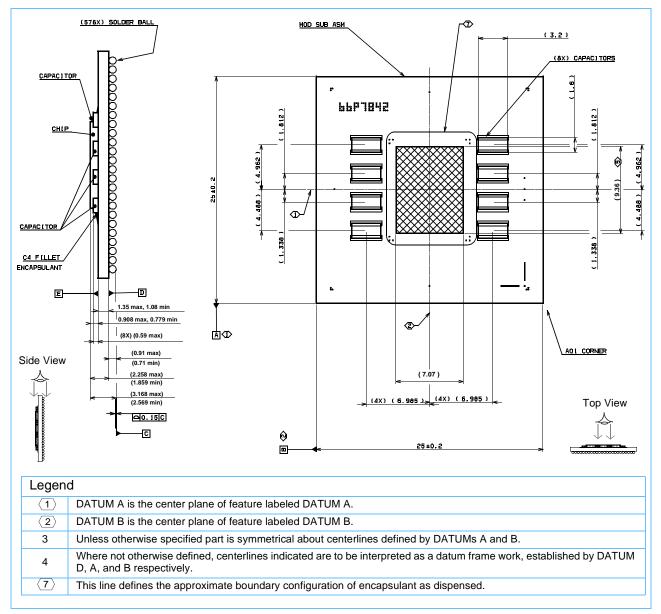

| Figure 4-1. PPC 970FX Microprocessor for Mechanical Package, Leaded, for DD3.0x Parts (to 41        | op and side)   |

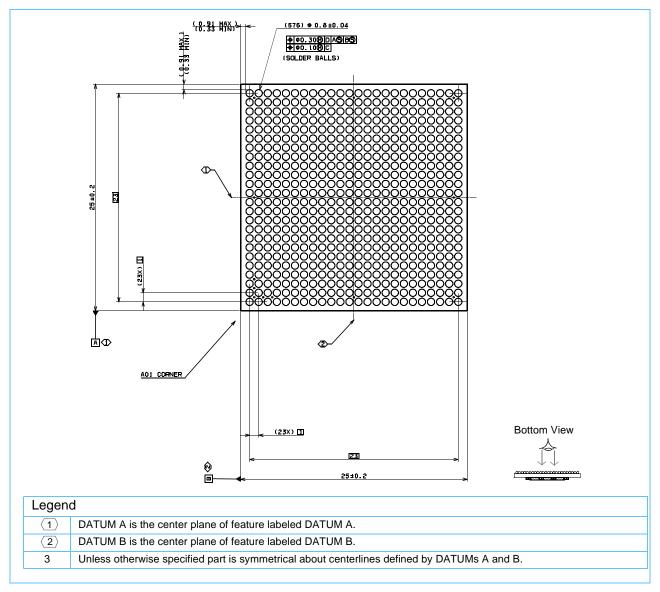

| Figure 4-2. PPC 970FX Microprocessor Mechanical Package, Leaded, for DD3.1x Parts (top a            | and side) 42   |

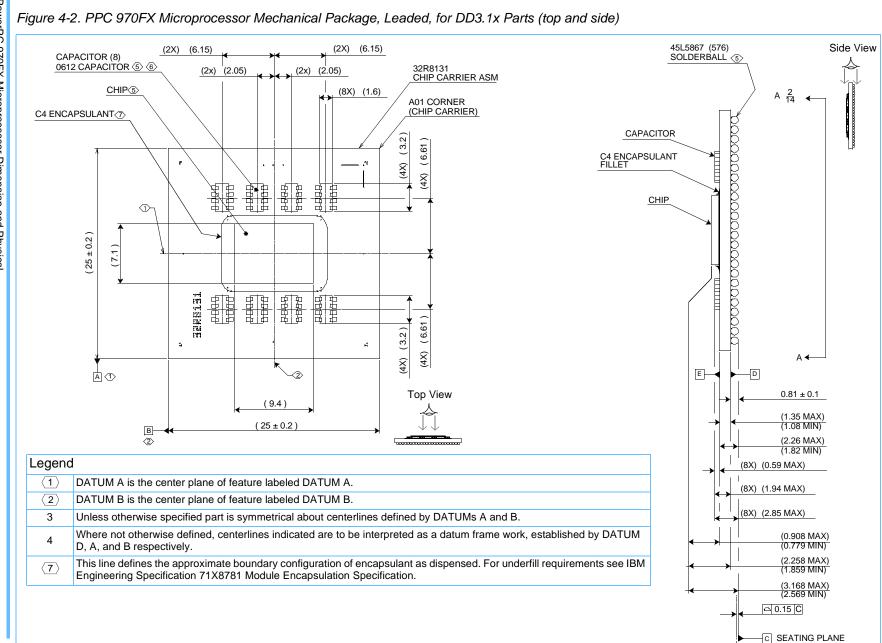

| Figure 4-3. PPC 970FX Microprocessor Bottom Surface Nomenclature of Mechanical Package CBGA Package |                |

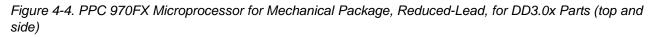

| Figure 4-4. PPC 970FX Microprocessor for Mechanical Package, Reduced-Lead, for DD3.0x F side)       |                |

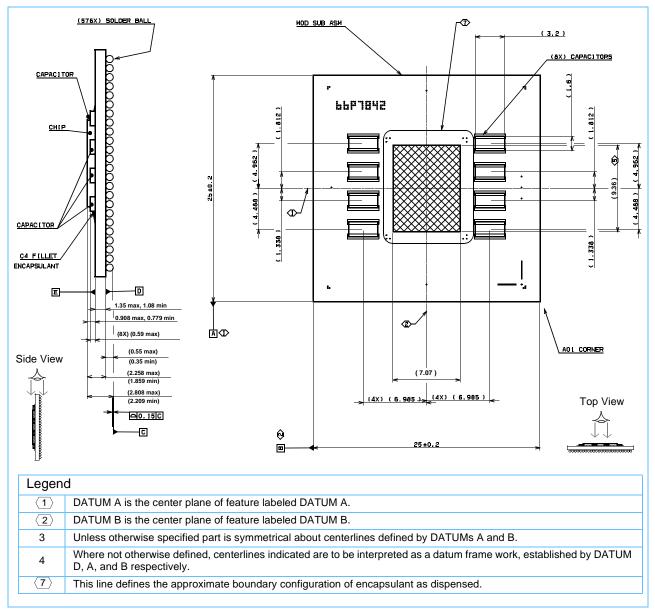

| Figure 4-5. PPC 970FX Microprocessor Mechanical Package, Reduced-Lead, for DD3.1 Parts 46           | (top and side) |

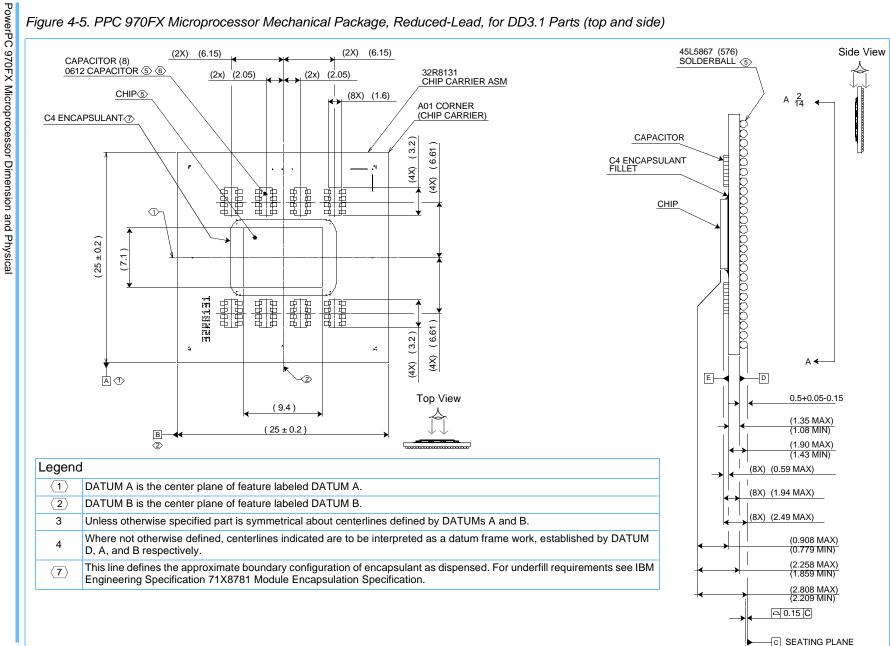

| Figure 4-6. PPC 970FX Microprocessor Bottom Surface Nomenclature of Reduced-Lead CBG                | A Package 47   |

| Figure 4-7. PPC 970FX Ball Placement (Top View)                                                     |                |

| Figure 4-8. PPC 970FX Ball Placement (Bottom View)                                                  |                |

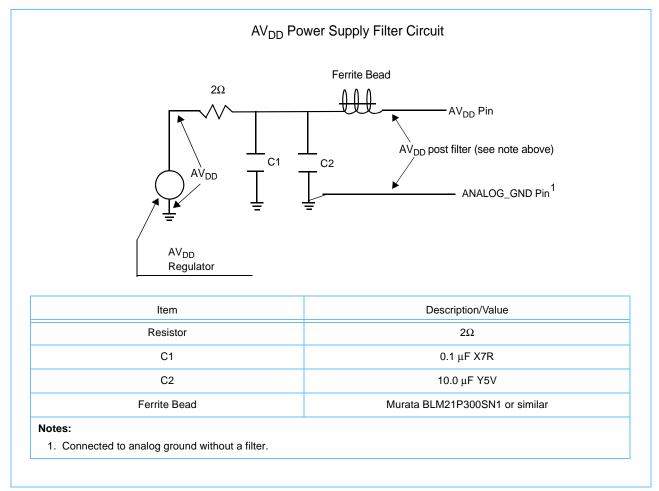

| Figure 5-1. PLL Power Supply Filter Circuit                                                         |                |

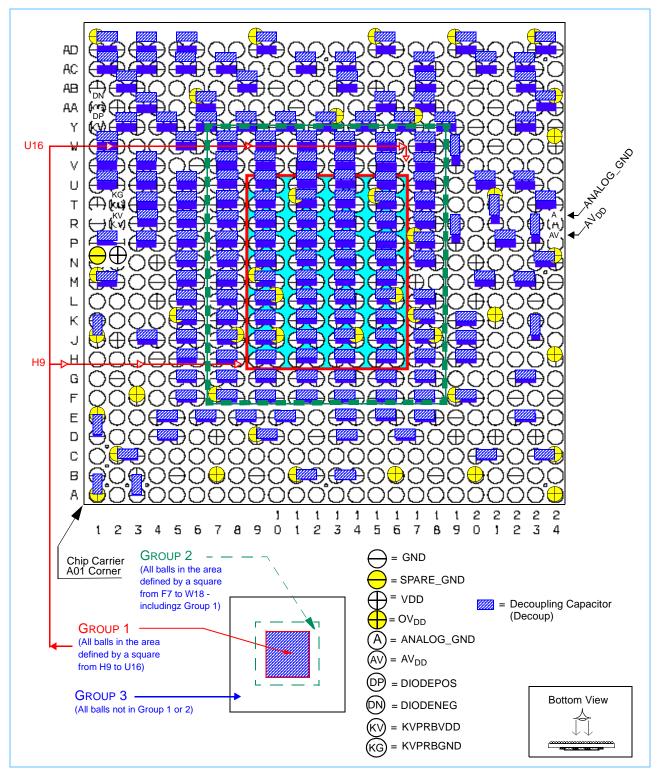

| Figure 5-2. Decoupling Capacitor (Decap) Locations                                                  |                |

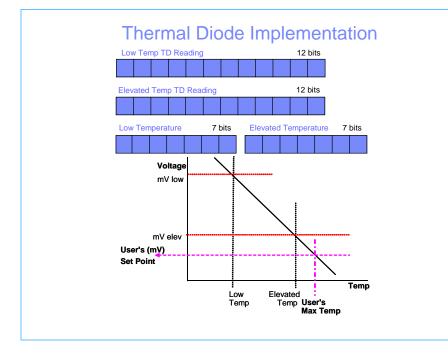

| Figure 5-3. PowerPC 970FX Thermal Diode Implementation                                              |                |

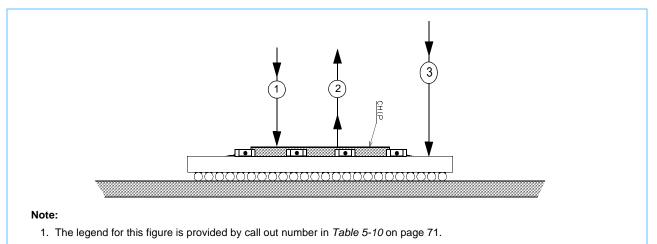

| Figure 5-4. Force Diagram for the PowerPC 970FX Package                                             | 71             |

| Table 1-1. PPC 970FX Ordering and Processor Version Register (PVR) for the Leaded PackageVersion | 14   |

|--------------------------------------------------------------------------------------------------|------|

| Table 1-2. PPC 970FX Ordering and Processor Version Register (PVR) for the Reduced-Lead Package  | Ver- |

| sion                                                                                             |      |

| Table 2-1. General Parameters of the PowerPC 970FX                                               |      |

| Table 3-1. Absolute Maximum Ratings                                                              | . 17 |

| Table 3-2. Recommended Operating Conditions                                                      | . 18 |

| Table 3-3. Package Thermal Characteristics                                                       | . 18 |

| Table 3-4. DC Electrical Specifications                                                          | . 19 |

| Table 3-5. Power Consumption for Power-Optimized Parts                                           | . 20 |

| Table 3-6. Power Consumption for Power-Optimized Parts                                           | . 21 |

| Table 3-7. Power Consumption for Standard Parts                                                  | . 21 |

| Table 3-8. Power Consumption for Standard Parts                                                  | . 22 |

| Table 3-9. Clock AC Timing Specifications                                                        | . 23 |

| Table 3-10. Processor-Clock Timing Relationship Between PSYNC and SYSCLK                         | . 24 |

| Table 3-11. Processor Interconnect SSB Driver Specifications                                     | . 27 |

| Table 3-12. Processor Interconnect SSB PCB Trace Specifications                                  | . 27 |

| Table 3-13. Processor Interconnect SSB Receiver Specifications                                   | . 28 |

| Table 3-14. Processor Interconnect SSB Timing Parameters for the Deskew and Clock Alignment      | . 28 |

| Table 3-15. Eye-Size Requirements                                                                | . 29 |

| Table 3-16. Input AC Timing Specifications                                                       | . 30 |

| Table 3-17. Input AC Timing Specifications for TBEN                                              | . 30 |

| Table 3-18. Input AC Timing Specifications for HRESET                                            | . 30 |

| Table 3-19. Asynchronous Type Output Signals                                                     | . 32 |

| Table 3-20. Asynchronous Open Drain Output Signals                                               | . 32 |

| Table 3-21. Asynchronous Open Drain Bidirectional (BiDi) Signals                                 | . 32 |

| Table 3-22. Input AC Timing Specifications                                                       | . 33 |

| Table 3-23. Mode Select Type Input Signals                                                       | . 35 |

| Table 3-24. Debug Pins                                                                           | . 35 |

| Table 3-25. JTAG AC Timing Specifications (Dependent on SYSCLK)                                  | . 37 |

| Table 4-1. Leaded and Reduced-Lead Package, Layout, and Assembly Differences                     | . 44 |

| Table 4-2. Pinout Listing for the CBGA Package                                                   | . 50 |

| Table 4-3. Voltage and Ground Assignments                                                        | . 55 |

| Table 5-1. PowerPC 970FX Bus Configuration                                                       | . 57 |

| Table 5-2. PowerPC 970FX PLL Configuration                                                       | . 58 |

| Table 5-3. System Configuration - Typical Examples of Pin Settings                               | . 59 |

| Table 5-4. Recommended Decoupling Capacitor Specifications                                       |      |

| Table 5-5. Recommended Minimum Number of Decoupling Capacitors                                   |      |

| Table 5-6. PowerPC 970FX Debug/Bringup Pin Settings and Information                              |      |

| Table 5-7. PowerPC 970FX Pins for Manufacturing Test Only                                        | . 64 |

| Table 5-8. Input/Output Signal Descriptions               | .65 |

|-----------------------------------------------------------|-----|

| Table 5-9. Thermal Diode Data Encoding                    | .70 |

| Table 5-10. Allowable Forces on the PowerPC 970FX Package | .71 |

# About This Datasheet

This datasheet describes the IBM PPC 970FX RISC Microprocessor. This microprocessor, also called the PPC 970FX, is a 64-bit implementation of the IBM PowerPC<sup>®</sup> family of reduced instruction set computer (RISC) microprocessors that are based on the PowerPC Architecture<sup>™</sup>.

# Who Should Read This Datasheet

This datasheet is intended for designers who plan to develop products using the PPC 970FX.

# **Related Publications**

Related IBM publications include the following:

- PowerPC 970FX RISC Microprocessor Users Manual

- PowerPC 970FX Power On Reset Application Note

- PowerPC 970FX DD3.x Errata List

Other related publications include the following:

• *I2C Bus Specification.* (This document is produced by Philips Semiconductors and can be downloaded from http://www.semiconductors.philips.com.)

# **Conventions and Notations Used in This Datasheet**

The use of overbars, for example DDEL\_OUT, designates signals that are active low or the compliment of differential signals.

The following software documentation conventions are used in this manual:

- 1. Function names are written in **bold** type. For example, **np\_npms\_proc\_register ()**.

- 2. Variables are written in italic type. For example, *enable\_mode*.

- 3. Keywords and data types are shown by being written all in capitals with underlines between words. For example, OFF\_DISABLED.

# 1. General Information

# **1.1 Description**

The IBM PowerPC 970FX RISC Microprocessor, is a 64-bit implementation of the IBM PowerPC<sup>®</sup> family of reduced instruction set computer (RISC) microprocessors that are based on the PowerPC Architecture. This microprocessor, also called the PPC 970FX, includes a Vector/SIMD facility which supports high-bandwidth data processing and algorithmic-intensive computations. This microprocessor is also designed to support multiple system organizations, including desktop and low-end server applications, and uniprocessor up through four-way SMP configurations.

Note: The terms microprocessor and processor are used interchangeably in this document.

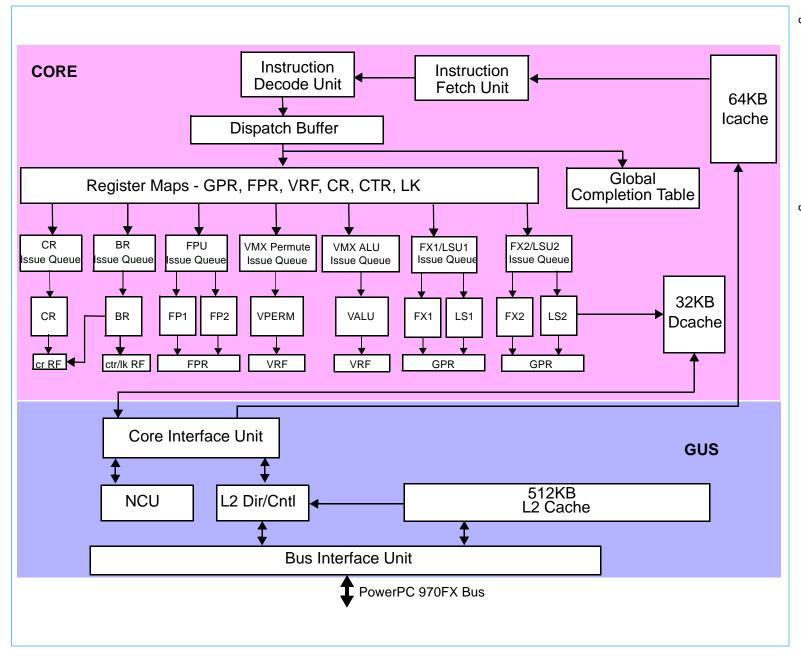

*Figure 1-1* on page 13 is a block diagram of the PPC 970FX.

The PPC 970FX consists of three main components:

- PPC 970FX Core which includes VMX execution units

- PPC 970FX Storage subsystem which includes core interface logic, non-cacheable unit, L2 cache and controls, and the Bus Interface Unit

- PPC 970FX Pervasive Functions

This document also provides pertinent physical characteristics of the PPC 970FX single chip modules (SCM).

### 1.2 Features

- 64-bit implementation of the PowerPC Architecture (Version 2.01)

- Binary compatibility for all PowerPC application level code (problem state)

- Binary compatibility for all PowerPC application level code (problem state)

- Support for 32-bit O/S bridge facility

- Vector/SIMD Multimedia eXtension

- Layered implementation strategy for very high frequency operation

- Deeply pipelined design

- 16 stages for most fixed-point register-register operations

- 18 stages for most load and store operations (assuming L1 Dcache hit)

- 21 stages for most floating point operations

- 19, 22, and 25 stages for fixed-point, complex-fixed, and floating point operations, respectively in the VALU.

- 19 stages for VMX permute operations

- Dynamic instruction cracking for some instructions allows for simpler inner core dataflow

- Dedicated dataflow for cracking one instruction into two internal operations

- Microcoded templates for longer emulation sequences

- Speculative superscalar inner core organization

- Aggressive branch prediction

- Prediction for up to two branches per cycle

- Support for up to 16 predicted branches in flight

- Prediction support for branch direction and branch addresses

- · Out of order issue of up to ten operations into 10 execution pipelines

- Two load or store operations

- Two fixed-point register-register operations

- Two floating-point operations

- One branch operation

- One condition register operation

- One VMX permute operation

- One VMX ALU operation

- In order dispatch of up to five operations into distributed issue queue structure

- Register renaming on GPRs, FPRs, VRFs, CR Fields, XER (parts), FPSCR, VSCR, VRSAVE, Link and Count

- Large number of instructions in flight (theoretical maximum of 215 instructions)

- Up to 16 instructions in instruction fetch unit (fetch buffer and overflow buffer)

- Up to 32 instructions in instruction fetch buffer in instruction decode unit

- Up to 35 instructions in 3 decode pipe stages and 4 dispatch buffers

- Up to 100 instructions in the inner-core (after dispatch)

- Up to 32 stores queued in the STQ (available for forwarding)

- · Fast, selective flush of incorrect speculative instructions and results

- · Specific focus on storage latency management

- Out-of-order and speculative issue of load operations

- Support for up to 8 outstanding L1 cache line misses

- Hardware initiated instruction prefetching from L2 cache

- · Software initiated data stream prefetching

- Support for up to 8 active streams

- Critical word forwarding / critical sector first

- New branch processing / prediction hints added to branch instructions

- Power management

- Static power management

- Software initiated doze and nap

- Dynamic power management

- Parts of the design stop their (hardware initiated) clocks when not in use

- PowerTune

- Software initiated slow down of the processor; selectable to half of the nominal operating frequency

# 1.3 PowerPC 970FX Block Diagram

Preliminary

Figure 1-1. PPC 970FX Block Diagram

# **1.4 Ordering and Processor Version Register**

#### 1.4.1 Leaded Package Version

The PowerPC 970FX has the following part numbers and Processor Version Register (PVR) values for the respective design revision levels.

Table 1-1. PPC 970FX Ordering and Processor Version Register (PVR) for the Leaded PackageVersion

| Order Part Number     | Frequency<br>GHz | Revision Level | PVR        | Note |

|-----------------------|------------------|----------------|------------|------|

| IBM25PPC970FX6TB055RT | 1.0              | DD3.0x         | 0x003C0300 | 1    |

| IBM25PPC970FX6TB075RT | 1.2              | DD3.0x         | 0x003C0300 | 1    |

| IBM25PPC970FX6TB186ET | 1.6              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TB267ET | 1.8              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TB348ET | 2.0              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TB348RT | 2.0              | DD3.0x         | 0x003C0300 | 1    |

Note 2: Refer to Table 3-7 and Table 3-8 for power and voltage rating.

| Order Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Frequency<br>GHz | Revision Level | PVR        | Note |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------|------|

| IBM25PPC970FX6UB055RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.0              | DD3.1          | 0x003C0301 | 1    |

| IBM25PPC970FX6UB075RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.2              | DD3.1          | 0x003C0301 | 1    |

| IBM25PPC970FX6UB105RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.4              | DD3.1          | 0x003C0301 | 1    |

| IBM25PPC970FX6UB185RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.6              | DD3.1          | 0x003C0301 | 1    |

| IBM25PPC970FX6UB186ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.6              | DD3.1          | 0x003C0301 | 2    |

| IBM25PPC970FX6UB267ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1.8              | DD3.1          | 0x003C0301 | 2    |

| IBM25PPC970FX6UB348ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0              | DD3.1          | 0x003C0301 | 2    |

| IBM25PPC970FX6UB348RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.0              | DD3.1          | 0x003C0301 | 1    |

| IBM25PPC970FX6UB428ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2              | DD3.1          | 0x003C0301 | 2    |

| IBM25PPC970FX6UB429RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2.2              | DD3.1          | 0x003C0301 | 1    |

| Note 1: Refer to <i>Table 3-5</i> and and <i>Table 3-5</i> and and <i>Table 3-5</i> and and <i>Table 3-5</i> and a |                  | -              |            |      |

**Note 1:** Refer to *Table 3-5* and *Table 3-6* for power and voltage rating. **Note 2:** Refer to *Table 3-7* and *Table 3-8* for power and voltage rating.

#### 1.4.2 Reduced-Lead Package Version

The PowerPC 970FX has the following part numbers and Processor Version Register (PVR) values for the respective design revision levels.

| Table 1-2. PPC 970FX Ordering and Processor Version Register (PVR) for the Reduced-Lead Package |

|-------------------------------------------------------------------------------------------------|

| Version                                                                                         |

| Order Part Number                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Frequency<br>GHz | Revision Level | PVR        | Note |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------|------|

| IBM25PPC970FX6TR055RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.0              | DD3.0x         | 0x003C0300 | 1    |

| IBM25PPC970FX6TR075RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.2              | DD3.0x         | 0x003C0300 | 1    |

| IBM25PPC970FX6TR186ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.6              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TR267ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1.8              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TR348ET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0              | DD3.0x         | 0x003C0300 | 2    |

| IBM25PPC970FX6TR348RT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2.0              | DD3.0x         | 0x003C0300 | 1    |

| Note 1: Refer to <i>Table 3-5</i> and <i>Table 3-5</i> and <i>Table 3-7</i> a | •                | 0 0            |            | ·    |

| Order Part Number     | Frequency<br>GHz | Revision Level | PVR        | Note |

|-----------------------|------------------|----------------|------------|------|

| IBM25PPC970FX6UR055RT | 1.0              | DD3.1          | 0x003C0301 | 1    |