IBM PowerPC<sup>®</sup> 750CL Microprocessor Revision Level DD2.X

Datasheet

Preliminary

Version 2.1

September 30, 2006

© Copyright International Business Machines Corporation 2005, 2006

All Rights Reserved Printed in the United States of America 2006.

The following are trademarks of International Business Machines Corporation in the United States, or other countries, or both.

| IBM         | IBM Logo             |

|-------------|----------------------|

| PowerPC     | PowerPC Logo         |

| PowerPC 750 | PowerPC Architecture |

IEEE is a registered trademark in the United States, owned by the Institute of Electrical and Electronics Engineers.

Other company, product and service names may be trademarks or service marks of others.

All information contained in this document is subject to change without notice. The products described in this document are NOT intended for use in applications such as implantation, life support, or other hazardous uses where malfunction could result in death, bodily injury, or catastrophic property damage. The information contained in this document does not affect or change IBM product specifications or warranties. Nothing in this document shall operate as an express or implied license or indemnity under the intellectual property rights of IBM or third parties. All information contained in this documents, and is presented as an illustration. The results obtained in other operating environments may vary.

While the information contained herein is believed to be accurate, such information is preliminary, and should not be relied upon for accuracy or completeness, and no representations or warranties of accuracy or completeness are made.

**Note:** This document contains information on products in the sampling and/or initial production phases of development. This information is subject to change without notice. Verify with your IBM field applications engineer that you have the latest version of this document before finalizing a design.

Some of the information provided herein pertains to third party vendors and their products and services. You are directed to contact such vendors with all questions pertaining to their respective products or services, as well as any requests for product or service updates. You are solely responsible for the selection of any vendors, including their products and services. The vendors identified herein are not agents or representatives of IBM and are not authorized to make commitments, warranties or representations on behalf of IBM. IBM makes no commitments, warranties or representations with regard to the vendors, their respective product or services, or the compatibility of such products or services with any of IBM's product or services.

The information contained in this document is provided on an "AS IS" basis and no warranties of any kind, including but not limited to the implied warranties of merchantability and fitness for a particular purpose, are provided. In no event will IBM be liable to you or to any third parties for any damages arising directly or indirectly from any use of the information contained in this document.

IBM Microelectronics Systems and Technology Group 2070 Route 52, Bldg. 330 Hopewell Junction, NY 12533-6351

The IBM home page can be found at ibm.com

The IBM Microelectronics home page can be found at ibm.com/chips

750cl\_ds\_title.fm. September 30, 2006

# **Table of Contents**

| 1. | General Information                                                                                  | . 9 |

|----|------------------------------------------------------------------------------------------------------|-----|

|    | 1.1 Features                                                                                         | 9   |

|    | 1.2 Processor Version Register                                                                       | 12  |

|    | 1.3 Part Number Information                                                                          | 12  |

| 2. | Overview                                                                                             | 13  |

|    | 2.1 Block Diagram                                                                                    | 13  |

|    | 2.2 General Parameters                                                                               |     |

| 3. | Electrical and Thermal Characteristics                                                               | 15  |

|    | 3.1 DC Electrical Characteristics                                                                    | 15  |

|    | 3.2 AC Electrical Characteristics                                                                    | 17  |

|    | 3.3 Clock Specifications                                                                             | 18  |

|    | 3.4 Spread Spectrum Clock Generator                                                                  | 19  |

|    | 3.4.1 Design Considerations                                                                          | 19  |

|    | 3.5 60x Bus Input AC Specifications                                                                  |     |

|    | 3.5.1 Input Setup Timing                                                                             |     |

|    | 3.6 60x Bus Output AC Specifications                                                                 |     |

|    | 3.6.1 IEEE 1149.1 AC Timing Specifications                                                           | 26  |

| 4. | Dimensions and Signal Assignments                                                                    | 29  |

|    | 4.1 Package                                                                                          | 29  |

|    | 4.1.1 Överview                                                                                       |     |

|    | 4.1.2 Features                                                                                       | 29  |

|    | 4.2 Mechanical Specifications                                                                        |     |

|    | 4.3 Microprocessor Ball Placement                                                                    |     |

|    | 4.4 Pinout Listings                                                                                  | 33  |

| 5. | System Design Information                                                                            | 36  |

|    | 5.1 Reference Clock Selection                                                                        | 36  |

|    | 5.2 PLL Configuration                                                                                | 36  |

|    | 5.3 PLL Power Supply Filtering                                                                       | 38  |

|    | 5.4 Decoupling Recommendations                                                                       | 38  |

|    | 5.5 Connection Recommendations                                                                       | 41  |

|    | 5.6 Die Temperature Monitor                                                                          | 41  |

|    | 5.7 Output Buffer DC Impedance                                                                       |     |

|    | 5.7.1 Input/Output Usage                                                                             |     |

|    | 5.8 Thermal Management Information                                                                   |     |

|    | 5.8.1 Minimum Heat Sink Requirements                                                                 |     |

|    | 5.8.2 Internal Package Conduction Resistance<br>5.8.3 Adhesives and Thermal Interface Materials      |     |

|    |                                                                                                      |     |

|    | <ul><li>5.9 Heat-Sink Selection Example</li><li>5.10 Operational and Design Considerations</li></ul> |     |

|    | 5.10 Operational and Design Considerations                                                           |     |

|    |                                                                                                      | 01  |

| 5.10.2 Configuring the Processor During Reset                                    | 57 |

|----------------------------------------------------------------------------------|----|

| 5.10.3 64-Bit or 32-Bit Data Bus Mode                                            | 58 |

| 5.10.3.1 Precharge Duration Selection and Application                            | 58 |

| 5.11 JTAG Test Access Port (TAP) Operation                                       | 58 |

| 5.11.1 Interface Pins                                                            | 59 |

| 5.11.2 Supported IEEE 1149 JTAG Instructions and Data Registers                  | 59 |

| 5.11.2.1 Instructions                                                            | 59 |

| 5.11.2.2 Data Registers                                                          | 59 |

| 5.11.3 Recommendations to Support System Debug                                   | 60 |

| 5.11.3.1 Processor Debug System Enablement when Implementing Precharge Selection | 60 |

# List of Figures

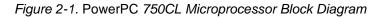

| Figure 2-1.  | PowerPC 750CL Microprocessor Block Diagram                                                                    | . 13 |

|--------------|---------------------------------------------------------------------------------------------------------------|------|

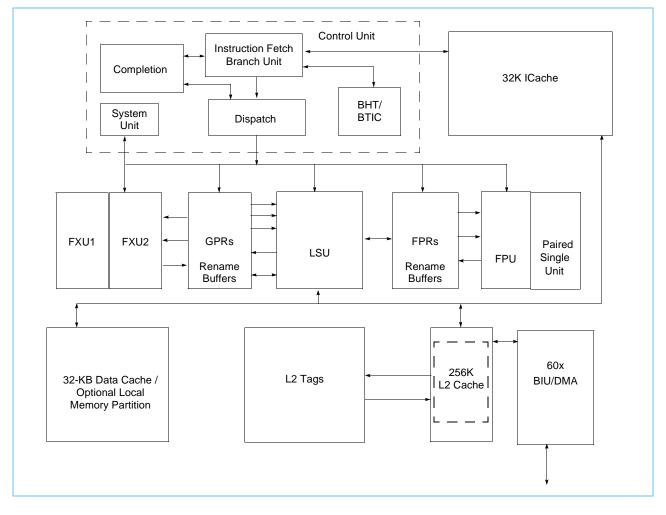

| Figure 3-1.  | SYSCLK Input Timing Diagram                                                                                   | . 18 |

| Figure 3-2.  | Linear Sweep Modulation Profile                                                                               | . 19 |

| Figure 3-3.  | Input Timing Definition                                                                                       | .21  |

| Figure 3-4.  | Input Timing Diagram                                                                                          | .21  |

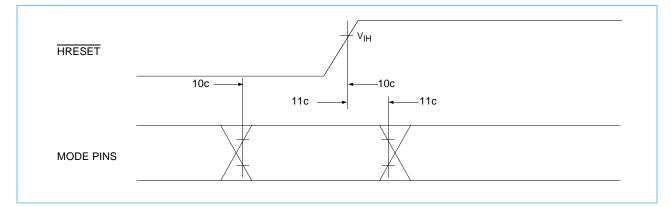

| Figure 3-5.  | Mode Select Input Timing Diagram                                                                              | . 22 |

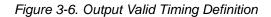

| Figure 3-6.  | Output Valid Timing Definition                                                                                | . 24 |

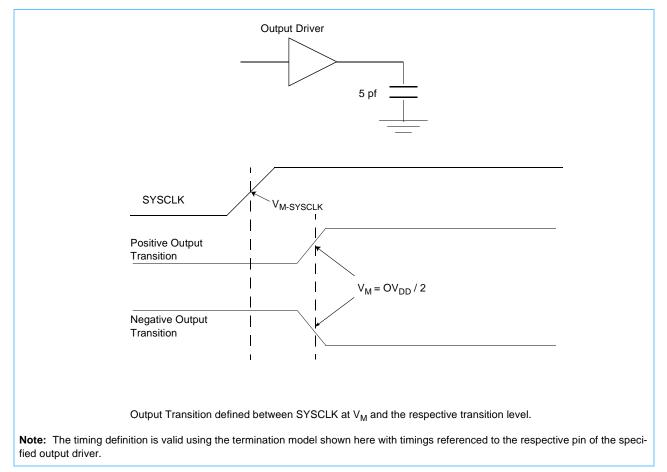

| Figure 3-7.  | Output Timing Diagram for 750CL                                                                               | . 25 |

| Figure 3-8.  | JTAG Clock Input Timing Diagram                                                                               | . 27 |

| Figure 3-9.  | TRST Timing Diagram                                                                                           | . 27 |

| Figure 3-10. | Boundary-Scan Timing Diagram                                                                                  | . 27 |

| Figure 3-11. | Test Access Port Timing Diagram                                                                               | . 28 |

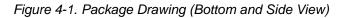

| Figure 4-1.  | Package Drawing (Bottom and Side View)                                                                        | . 30 |

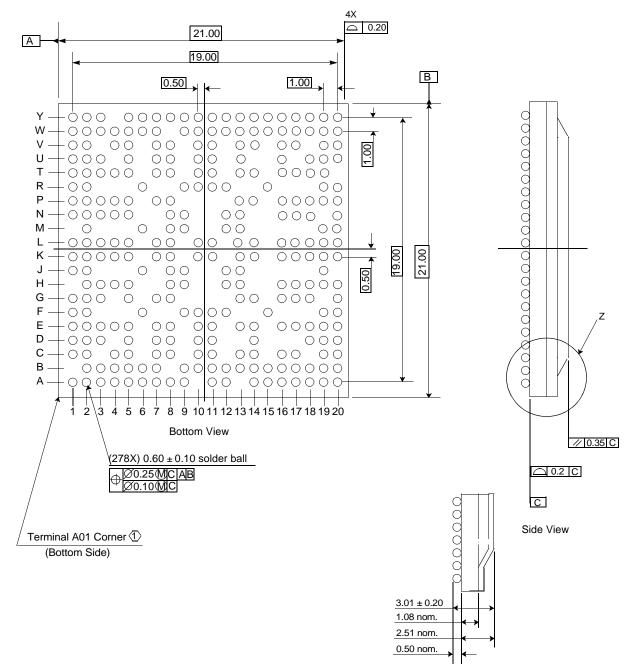

| Figure 4-2.  | Package Drawing (Top View)                                                                                    | . 31 |

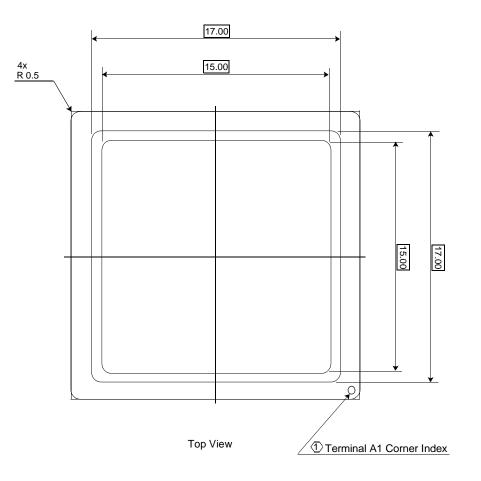

| Figure 4-3.  | PowerPC 750CL Microprocessor Ball Placement                                                                   | . 32 |

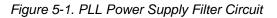

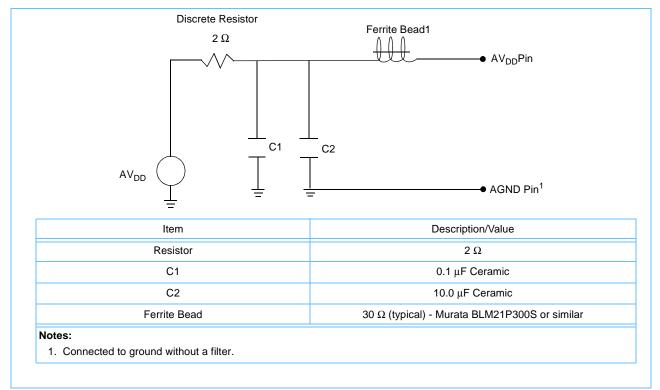

| Figure 5-1.  | PLL Power Supply Filter Circuit                                                                               | . 38 |

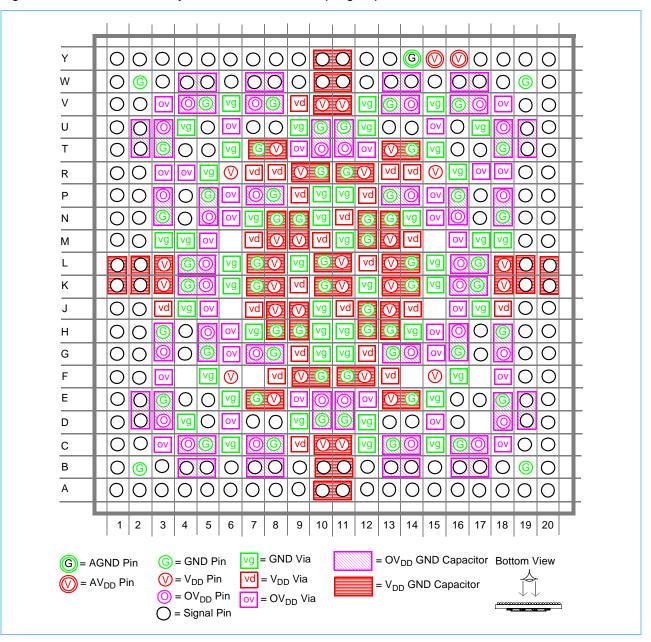

| Figure 5-2.  | Orientation and Layout of the 750CL Decoupling Capacitors                                                     | . 40 |

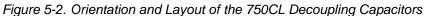

| Figure 5-3.  | Thermal Diode Schematic                                                                                       | . 41 |

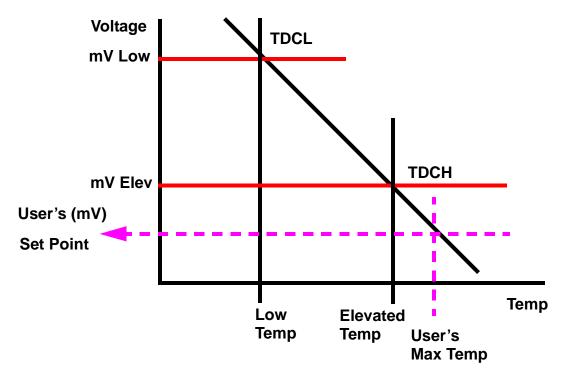

| Figure 5-4.  | Interpolating Chip Junction Temperature Using Thermal Calibration Registers and User Vo<br>age Measurement 42 | olt- |

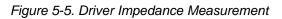

| Figure 5-5.  | Driver Impedance Measurement                                                                                  | . 43 |

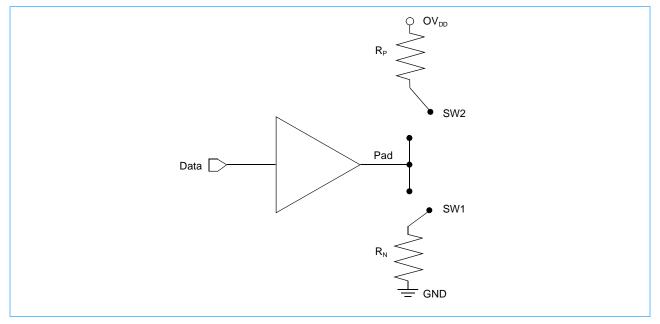

| Figure 5-6.  | IBM RISCWatch JTAG to HRESET, TRST, and SRESET Signal Connector                                               | . 49 |

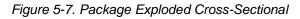

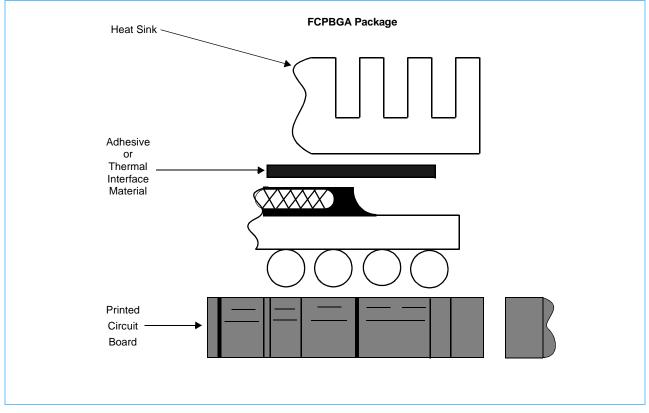

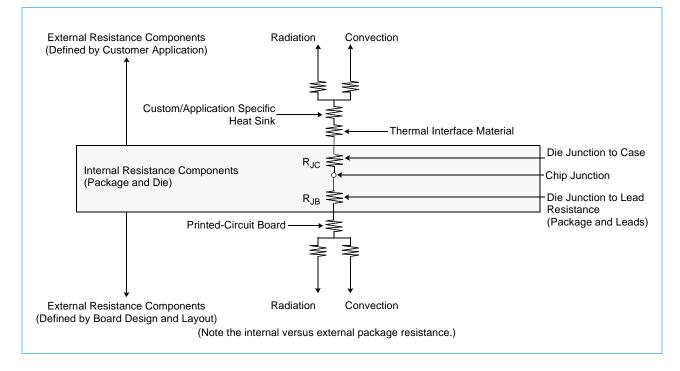

| Figure 5-7.  | Package Exploded Cross-Sectional                                                                              | . 50 |

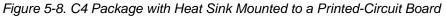

| Figure 5-8.  | C4 Package with Heat Sink Mounted to a Printed-Circuit Board                                                  | . 52 |

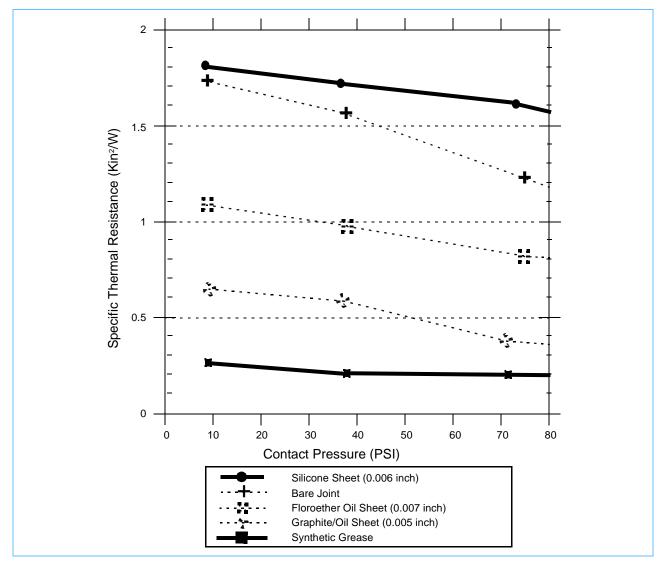

| Figure 5-9.  | Thermal Performance of Select Thermal Interface Material                                                      | . 54 |

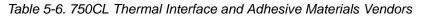

| Figure 5-10. | Example of a Pin-Fin Heat-Sink-to-Ambient Thermal Resistance versus Airflow Velocity                          | . 56 |

# **List of Tables**

| Table 1-1.  | 750CL Processor Version Register (PVR)                 |    |

|-------------|--------------------------------------------------------|----|

| Table 2-1.  | 750CL General Parameters                               | 14 |

| Table 3-1.  | Absolute Maximum Ratings                               | 15 |

| Table 3-2.  | Recommended Operating Conditions                       |    |

| Table 3-3.  | Package Thermal Characteristics                        | 16 |

| Table 3-4.  | DC Electrical Specifications                           | 16 |

| Table 3-5.  | Power Consumption                                      | 17 |

| Table 3-6.  | Clock AC Timing Specifications                         |    |

| Table 3-7.  | 60x Bus Input AC Timing Specifications                 | 20 |

| Table 3-8.  | 60x Bus Output AC Timing Specifications                | 23 |

| Table 3-9.  | JTAG AC Timing Specifications (Independent of SYSCLK)  | 26 |

| Table 4-1.  | Pinout Listing for the FC-PBGA Package                 |    |

| Table 5-1.  | 750CL Microprocessor PLL Configuration                 |    |

| Table 5-2.  | Recommended Decoupling Capacitor Specifications        |    |

| Table 5-3.  | Driver Impedance Characteristics                       |    |

| Table 5-4.  | Input/Output Usage                                     | 45 |

| Table 5-5.  | 750CL Heat-Sink Vendors                                | 51 |

| Table 5-6.  | 750CL Thermal Interface and Adhesive Materials Vendors | 55 |

| Table 5-7.  | Summary of Mode Select                                 | 57 |

| Table 5-8.  | TAP Pins                                               | 59 |

| Table 5-9.  | Instruction Encodings                                  | 59 |

| Table 5-10. | JTAG Instructions                                      | 60 |

## **1. General Information**

The IBM PowerPC 750CL RISC Microprocessor is a 32-bit implementation of the IBM PowerPC family. This document contains pertinent physical and electrical characteristics of the IBM PowerPC 750CL RISC Microprocessor Revision DD2.X Single Chip Module (SCM). The PowerPC 750CL Microprocessor is also referred to as the 750CL throughout this document.

## 1.1 Features

This section summarizes the features of the 750CL implementation of the PowerPC Architecture<sup>™</sup>. Major features of the 750CL include the following:

- Branch processing unit

- Fetches four instructions per clock

- Processes one branch per cycle and can resolve two speculations

- · Executes single speculative stream during fetch of another speculative stream

- Has 512-entry Branch History Table (BHT) for dynamic prediction

- Dispatch unit

- · Has full hardware detection of dependencies which are resolved in the execution units

- Dispatches two instructions to six independent units (system, branch, load/store, fixed-point unit 1, fixed-point unit 2, or floating-point)

- Has serialization control (predispatch, postdispatch, execution, serialization)

- Decode

- Register file access

- Forwarding control

- Partial instruction decode

- Load/store unit

- Has single-cycle load or store cache access (byte, half-word, word, double-word)

- Has effective address generation

- Allows hits under misses (one outstanding miss)

- · Has single-cycle misaligned access within double word boundary

- Has alignment, zero padding, sign extend for integer register file

- Converts floating-point internal format (using alignment, normalization, and quantization)

- Sequences for load/store multiples and string operations

- Has store gathering

- Has cache and TLB instructions

- · Supports big and little-endian byte addressing

- Supports misaligned little-endian in hardware

- Fixed-point units

- Fixed-Point Unit 1 (FXU1); multiply, divide, shift, rotate, arithmetic, logical

- Fixed-Point Unit 2 (FXU2); shift, rotate, arithmetic, logical

- Single-cycle arithmetic, shift, rotate, logical

- Multiply and divide support (multi-cycle)

- Early out multiply

- Floating-point unit

- Support for IEEE-754 standard single- and double-precision floating-point arithmetic

- 3-cycle latency, 1-cycle throughput, single-precision multiply-add

- 3-cycle latency, 1-cycle throughput, double-precision add

- 4-cycle latency, 2-cycle throughput, double-precision multiply-add

- Hardware support for divide

- Hardware support for denormalized numbers

- Time deterministic non-IEEE mode

- Support for paired single floating point arithmetic

- Data quantization support

- System unit

- Executes CR logical instructions and miscellaneous system instructions

- Has special register transfer instructions

- Level 1 (L1) cache structure

- 32K, 32-byte line, 8-way set associative instruction cache

- 32K, 32-byte line, 8-way set associative data cache

- Optional local memory partition

- Single-cycle cache access

- Pseudo-LRU replacement

- Copy-back or write-through data cache (on a page per page basis)

- Supports PowerPC memory coherency modes

- Non-blocking instruction and data cache (supports hits under one outstanding miss)

- No snooping of instruction cache

- Memory management unit

- 128 entry, 2-way set associative instruction TLB

- 128 entry, 2-way set associative data TLB

- Hardware reload for TLBs

- 8 instruction BAT's and 8 data BATs

- Virtual memory support for up to 4 exabytes (252) virtual memory

- Real memory support for up to 4 gigabytes (232) of physical memory

- Level 2 (L2) cache

- 256KB, 64-byte line, 2-way set associative on-chip cache memory

- Internal L2 cache controller with 2K-entry tag array

- Copy-back or write-through data cache (on a page basis, or for all L2)

- 64-byte cache line organized as two 32-byte sectors

- L2 frequency at core speed

- Selectable 32B, 64B, or 128B L2 cache loads

- Error Correction Code (ECC) protection on cache array

- Bus interface

- Is compatible with 60X processor interface

- Has a 32-bit address bus

- Has a 64-bit data bus (also supports 32-bit data bus mode)

- Supports bus-to-core frequency multipliers of 2x, 2.5x, 3x, 3.5x, 4x, 4.5x, 5x, 5.5x, 6x, 6.5x, 7x, 7.5x, 8x, 8.5x, 9x, 9.5x, and 10x

- Has DMA support for local memory load/store

- Bus transaction pipeline depth of 2, 3, or 4 transactions (selectable)

- Write Gather Pipe

- 128 byte circular queue

- 32 byte transfers

- Independent read and write ports

- Testability

- LSSD scan design

- JTAG interface.

## **1.2 Processor Version Register**

The 750CL has the following Processor Version Register (PVR) values for the respective design revision levels.

| 750CL Design Revision Level                                                                                             | PVR        |  |  |

|-------------------------------------------------------------------------------------------------------------------------|------------|--|--|

| DD2.0                                                                                                                   | 0x000872r0 |  |  |

| <b>Note:</b> r = reserved nibble; reserved bits can be either '0' or '1', and should be masked in application software. |            |  |  |

## **1.3 Part Number Information**

| Power  | PC 750 Family Member   |                                                                                                                                             |                                |

|--------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Proces | s Technology           |                                                                                                                                             | Reliability Grade              |

| Design | Revision Level         |                                                                                                                                             | Application Conditions         |

| Packag | де Туре                |                                                                                                                                             | Nominal Core Frequen           |

|        | Process Technology     | G = 10KE                                                                                                                                    |                                |

|        | Design Revision Level  | E = dd2.0                                                                                                                                   |                                |

|        | Package Type           | Q = Lead-Reduced FCPBGA (flip of                                                                                                            | chip plastic ball grid array)  |

|        | Nominal core frequency | Minimum core frequency in MHz at<br>ditions<br>90 = 900 MHz<br>80 = 800 MHz<br>73 = 733 MHz<br>60 = 600 MHz<br>50 = 500 MHz<br>40 = 400 MHz | the specified Application Con- |

|        | Application Conditions | 2: Vdd=1.15V +/-50mV, OVdd =1.1<br>= 0 to 105C<br>3:                                                                                        | 5V +/-50mV or 1.8V +/- 5%. Tj  |

|        | Reliability Grade      | 4 = Commercial Grade                                                                                                                        |                                |

# 2. Overview

The IBM PowerPC 750CL RISC Microprocessor, also called the 750CL, is targeted for high-performance, low-power systems using a 60X bus. The 750CL also includes an internal 256kB L2 cache with on-board Error Correction Circuitry (ECC).

## 2.1 Block Diagram

## **2.2 General Parameters**

## Table 2-1. 750CL General Parameters

| Item              | Description                                                                                                 | Notes |

|-------------------|-------------------------------------------------------------------------------------------------------------|-------|

| Technology        | 90nm copper Silicon-On-Insulator (SOI) technology<br>Low-K dielectric<br>8 layer metal wirings<br>CMOS 10ke |       |

| Die Size          | 15.92 sq. mm (3.99x3.99mm)                                                                                  |       |

| Logic design      | Fully static                                                                                                |       |

| Package           | 278-pin Plastic Ball Grid Array (FC-PBGA)<br>21 × 21 mm (1.0-mm pitch)<br>0.6-mm ball size                  |       |

| Core power supply | 1.15 V Nominal                                                                                              |       |

| I/O power supply  | 1.15 V Nominal or 1.8 V Nominal                                                                             |       |

# 3. Electrical and Thermal Characteristics

This section provides AC and DC electrical specifications and thermal characteristics for the 750CL.

## 3.1 DC Electrical Characteristics

The tables in this section describe the DC electrical characteristics for the 750CL

#### Table 3-1. Absolute Maximum Ratings

| Characteristic            | Symbol           | 1.15V           | 1.8V        | Units | Notes |

|---------------------------|------------------|-----------------|-------------|-------|-------|

| Core supply voltage       | V <sub>DD</sub>  | -0.3 to 1.4     | -0.3 to 1.4 | V     | 3,4   |

| PLL supply voltage        | AV <sub>DD</sub> | -0.3 to 1.4     | -0.3 to 1.4 | V     | 3,4,5 |

| 60x bus supply voltage    | OV <sub>DD</sub> | -0.3 to 1.4     | -0.3 to 2.0 | V     | 3,4   |

| Input voltage             | V <sub>IN</sub>  | -0.3 to 1.4     | -0.3 to 2.0 | V     | 2     |

| Storage temperature range | T <sub>STG</sub> | JEDEC J-STD-033 |             | С     |       |

Notes:

1. Functional and tested operating conditions are given in *Table 3-2* Recommended Operating Conditions. Absolute maximum ratings are stress ratings only, and functional operation and the maximums is not guaranteed. Stresses beyond those listed above may affect device reliability or cause permanent damage to the device.

2. Caution: Transient V<sub>IN</sub> overshoots of up to  $OV_{DD}$  + 0.8 V, with a maximum of 2.6 V for 1.8 V operation, and undershoots down to GND – 0.8 V, are allowed for up to 5 ns.

3. Caution: OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub> by more than 1.8 V continuously. OV<sub>DD</sub> may exceed V<sub>DD</sub>/AV<sub>DD</sub> by up to 2.0 V for up to 20 ms during power-on or power-off. OV<sub>DD</sub> must not exceed V<sub>DD</sub>/AV<sub>DD</sub> by more than 2.0 V for any amount of time.

4. Caution: V<sub>DD</sub>/AV<sub>DD</sub> must not exceed OV<sub>DD</sub> by more than 1.0 V continuously. V<sub>DD</sub>/AV<sub>DD</sub> may exceed OV<sub>DD</sub> by up to 1.4 V for up to 20 ms during power-on or power-off. V<sub>DD</sub>/AV<sub>DD</sub> must not exceed OV<sub>DD</sub> by more than 1.4 V for any amount of time.

5. Caution: AV<sub>DD</sub> must not exceed V<sub>DD</sub> by more than 0.5 V at any time.

#### Table 3-2. Recommended Operating Conditions

| Characteristic                      | Symbol           | Value                   | Unit | Notes |

|-------------------------------------|------------------|-------------------------|------|-------|

| Core supply voltage                 | V <sub>DD</sub>  | 1.15 ± .05              | V    |       |

| 60X bus I/O supply voltage (1.15 V) | OV <sub>DD</sub> | 1.15 ± .05              | V    |       |

| 60X bus I/O supply voltage (1.8 V)  | OV <sub>DD</sub> | 1.8 ± 5%                | V    |       |

| PLL supply voltage <sup>2</sup>     | AV <sub>DD</sub> | 1.15 ± .05              | V    |       |

| Input voltage                       | V <sub>IN</sub>  | GND to OV <sub>DD</sub> | V    |       |

| Die-junction temperature            | ТJ               | 0 to 105                | °C   |       |

Notes:

1. ESD Specifications: Human body model +/- 500V Machine model +/- 200V

2. Please consult section 5.3 for AVdd noise filtering requirements.

#### Table 3-3. Package Thermal Characteristics

| Characteristic                                                                    | Symbol          | Value | Unit |

|-----------------------------------------------------------------------------------|-----------------|-------|------|

| FC-PBGA package thermal resistance, junction-to-case thermal resistance (typical) | θ <sup>JC</sup> | 2     | °C/W |

| FC-PBGA package thermal resistance, junction-to-lead thermal resistance (typical) | $\theta_{JB}$   | 13    | °C/W |

**Note:**  $\theta_{JC}$  is the internal resistance from the junction to the back of the die. A heat sink customized to the end user application and ambient operating environment is required to ensure the die junction temperature is maintained within the limits defined in Table 3-2 on page 15.

Note: Thermal resistance values are based on modeling only.

## Table 3-4. DC Electrical Specifications

See Table 3-2 on page 15 for recommended operating conditions.

| Characteristic                                                               | Symbol                   |      |      | Unit | Notes  |  |

|------------------------------------------------------------------------------|--------------------------|------|------|------|--------|--|

| Characteristic                                                               | Cymbol                   | Min. | Max. | Onit | 110100 |  |

| Input high veltage                                                           | V <sub>IH (1.15 V)</sub> | 0.75 | —    | V    |        |  |

| Input high voltage                                                           | V <sub>IH (1.8 V)</sub>  | 1.20 | —    | V    |        |  |

| Input low voltage                                                            | V <sub>IL (1.15 V)</sub> | —    | 0.40 | V    |        |  |

| input iow voltage                                                            | V <sub>IL (1.8 V)</sub>  | —    | 0.60 | V    |        |  |

| Input leakage current, $V_{IN}$ = applies to all $OV_{DD}$ levels            | I <sub>IN</sub>          | —    | 10   | μΑ   |        |  |

| Hi-Z (off state) leakage current, $V_{IN}$ = applies to all $OV_{DD}$ levels | I <sub>TSI</sub>         | —    | 10   | μA   |        |  |

| Output high voltage, I <sub>OH</sub> = -4 mA                                 | V <sub>OH (1.15 V)</sub> | 0.90 | —    | V    |        |  |

| Output high voltage, I <sub>OH</sub> = -4 mA                                 | V <sub>OH (1.8 V)</sub>  | 1.30 | —    | V    |        |  |

| Output low voltage, I <sub>OL</sub> = 4 mA                                   | V <sub>OL (1.15 V)</sub> | —    | 0.30 | V    |        |  |

| Output low voltage, I <sub>OL</sub> = 4 mA                                   | V <sub>OL (1.8 V)</sub>  | —    | 0.40 | V    |        |  |

| Capacitance, V <sub>IN</sub> = 0 V, f = 1 MHz                                | C <sub>IN</sub>          | —    | 5    | pF   | 1      |  |

|                                                                              | V <sub>IH (1.15 V)</sub> | 0.8  | —    | V    |        |  |

| SYSCLK Input High Voltage                                                    | V <sub>IH (1.8 V)</sub>  | 1.20 | —    | V    |        |  |

|                                                                              | V <sub>IL (1.15 V)</sub> | —    | 0.30 | V    |        |  |

| SYSCLK Input Low Voltage                                                     | V <sub>IL (1.8 V)</sub>  | _    | 0.30 | V    |        |  |

#### Table 3-5. Power Consumption

See Table 3-2 on page 15 for recommended operating conditions.

| Mode                    | T <sub>i</sub> | T <sub>c</sub> | Processor<br>Frequency |      |       |

|-------------------------|----------------|----------------|------------------------|------|-------|

|                         | ,              | j C            |                        | Unit | Notes |

| Maximum Power           | 95°C           | 90°C           | 5.5                    | W    | 1     |

| Maximum Power           | 90°C           | TBD            | 5.2                    | W    | 1     |

| Maximum Power           | 85°C           | TBD            | 4.8                    | W    | 1     |

| Nap/Sleep Typical Power | 55°C           | TBD            | 1.6                    | W    | 2     |

Notes:

These values apply for all valid 60x buses. The values do not include I/O supply power (OV<sub>DD</sub>) or PLL supply power (AV<sub>DD</sub>). OV<sub>DD</sub> power is system dependent, but is typically less than 2% of V<sub>DD</sub> power.

Maximum power is measured at the indicated V<sub>DD</sub> and T<sub>J</sub> using parts with worst-case process parameters and running RC5-72. RC5-72 runs hotter than typical production code, but it is possible to design code that runs even hotter than RC5-72. See *PowerPC* 750CL *Power Dissipation* Application Note for more information.

Typical power is an estimate of the average value modeled in a system executing typical applications with V<sub>DD</sub> and typical process parameters. Note that typical power cannot be used in the design of the power supply or cooling system.

## **3.2 AC Electrical Characteristics**

This section provides the AC electrical characteristics for the 750CL. After fabrication, parts are sorted by maximum processor core frequency as shown in *Section 3.3, Clock Specifications,* on page 18, and tested for conformance to the AC specifications for that frequency. The processor core frequency is determined by the bus (SYSCLK) frequency and the settings of the PLL configuration (PLL\_CFG[0:4]) signals.

## **3.3 Clock Specifications**

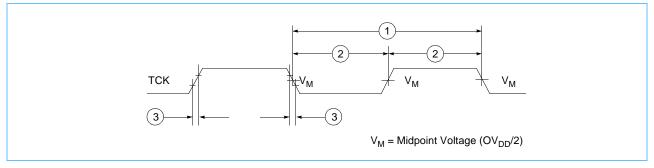

Table 3-6 provides the clock AC timing specifications as defined in Figure 3-1.

#### Table 3-6. Clock AC Timing Specifications

See Table 3-2 on page 15 for recommended operating conditions.<sup>1, 3, 5</sup>

| Figure 3-1          | Characteristic                       |      | lue  | Unit | Notes |

|---------------------|--------------------------------------|------|------|------|-------|

| Timing<br>Reference | Characteristic                       | Min. | Max. | Unit | Notes |

|                     | Processor frequency                  | 400  | 900  | MHz  |       |

|                     | SYSCLK frequency                     | 50   | 240  | MHz  |       |

| 2, 3                | SYSCLK slew rate                     | 2.50 | 10.0 | V/ns | 2     |

| 4                   | SYSCLK duty cycle measured at 0.60 V | 25   | 75   | %    |       |

|                     | SYSCLK cycle-to-cycle jitter         | —    | 150  | ps   | 4     |

|                     | Internal PLL relock time             | —    | 100  | μs   | 4     |

|                     | Internal PLL reset time              | 10   | —    | μs   | 5     |

Notes:

- Caution: The SYSCLK frequency and the PLL\_CFG[0:4] settings must be chosen such that the resulting SYSCLK (bus) frequency, CPU (core) frequency, and PLL frequency do not exceed their respective maximum or minimum operating frequencies. Refer to the PLL\_CFG[0:4] signal description in *Table 5-1, 750CL Microprocessor PLL Configuration,* on page 36 for valid PLL\_CFG[0:4] settings.

- 2. Slew rate for the SYSCLK inputs is measured from 0.4 to 0.75 V.

- 3. Timing is guaranteed by design and characterization, and is not tested.

- 4. Relock timing is guaranteed by design and characterization, and is not tested. PLL-relock time is the maximum amount of time required for PLL lock after a stable V<sub>DD</sub> and SYSCLK are reached during the power-on reset sequence. This specification also applies when the PLL has been disabled and subsequently re-enabled during sleep mode. Also note that hard reset (HRESET) must be held asserted for a minimum of 255 bus clocks after the PLL-relock time during the power-on reset sequence.

- 5. During power-up or if the frequency of SYSCLK is changed during hardware reset (HRESET), then the PLL must be reset to lock onto the new frequency.

## 3.4 Spread Spectrum Clock Generator

## 3.4.1 Design Considerations

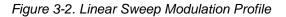

When designing with the Spread Spectrum Clock Generator (SSCG), there are a number of design issues that must be taken into account.

SSCG creates a controlled amount of long-term jitter. In order for a receiving PLL in the 750CL to operate in this environment, it must be able to accurately track the SSCG clock jitter.

The accuracy to which the 750CL PLL can track the SSCG clock is referred to as tracking skew. When performing system timing analysis, the tracking skew must be added or subtracted to the I/O timing specifications because the tracking skew appears as a static phase error between the internal PLL and the SSCG clock.

To minimize the impact on I/O timings, the following SSCG configuration is recommended:

- Down spread mode, less than or equal to 1% of the maximum frequency.

- A modulation frequency of 32 kHz or less.

- Linear sweep modulation or "Hershey's Kiss" (as in a Lexmark<sup>1</sup> profile) modulation profile as shown in *Figure 3-2*.

In this configuration, the tracking skew is less than 100 ps.

<sup>1.</sup> See patent 5,631,920.

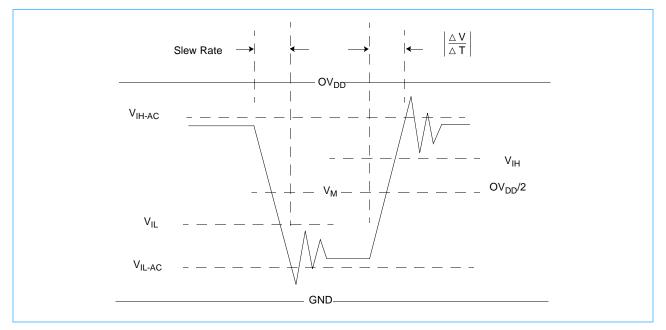

## 3.5 60x Bus Input AC Specifications

Table 3-7 provides the 60x bus AC timing specifications defined in Figure 3-4 and Figure 3-5 on page 22.

| Table 3-7. 60x Bus Input AC Timing Specifications                            |  |

|------------------------------------------------------------------------------|--|

| See <i>Table 3-2</i> on page 15 for operating conditions. <sup>1, 4, 5</sup> |  |

| Figure 3-4 and             |                                                                   | 1.15 V   | Mode | 1.8 V | Mode |                  |       |  |

|----------------------------|-------------------------------------------------------------------|----------|------|-------|------|------------------|-------|--|

| 3-5<br>Timing<br>Reference | Characteristic                                                    | Min.     | Max. | Min.  | Max. | Unit             | Notes |  |

| 10a                        | Input setup: SYSCLK to all inputs valid                           | 1.15     | _    | 1.1   | —    | ns               | 8     |  |

| 10c                        | Mode select input setup to HRESET, TLBI-<br>SYNC, QACK, and DRTRY | 8        | _    | 8     | _    | SYSCLK<br>cycles | 2     |  |

| 11a                        | Input hold: SYSCLK to inputs invalid                              | —        | 350  | —     | 400  | ps               |       |  |

| 11c                        | HRESET to mode select input hold TLBI-<br>SYNC., QACK, and DRTRY  | 0        | _    | 0     | —    | SYSCLK<br>cycles | 3     |  |

| V <sub>M</sub>             | Measurement reference voltage for inputs                          |          |      |       |      | —                |       |  |

| V <sub>IL-AC</sub>         | AC timing reference levels                                        | —        | 0.2  | —     | TBD  | V                | 6     |  |

| V <sub>IH-AC</sub>         |                                                                   | OVdd-0.2 | —    | TBD   | —    | v                | 0     |  |

| Slew Rate                  | Reference input slew rate                                         | 0.8      | _    | TBD   | —    | V/ns             | 7     |  |

Notes:

1. Input specifications are measured from the midpoint voltage (V<sub>M</sub>) of the signal in question to the V<sub>M</sub> of the rising edge of the input SYSCLK. Timings are measured at the pin (see *Figure 3-4* on page 21).

2. t<sub>SYSCLK</sub> is the period of the external clock (SYSCLK) in nanoseconds (ns). The numbers given in the table multiplied by the period of SYSCLK to compute the actual time duration (in ns) of the parameter in question.

- 3. This specification is for configuration mode select only. Also note that the HRESET must be held asserted for a *minimum of 255 bus clocks* after the PLL relock time during the power-on reset sequence.

- 4. All values are guaranteed by design, and are not tested.

- 5. Refer to Section 3.5.1 on page 20 and Figure 3-3 on page 21 for input setup timing definitions.

- 6. Input reference signal levels used to establish the timings defined in this table.

- 7. Input slew rate refers to the slew rate between Vih-AC and Vil-AC timing reference levels.

- 8. INT#, SMI#, MCP#, and CHKSTP\_IN# must remain asserted until recognised by the processor.

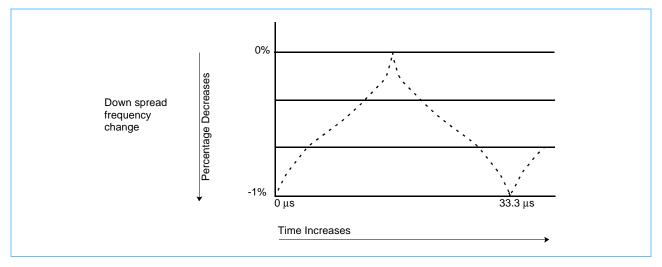

## 3.5.1 Input Setup Timing

The information in this subsection is provided to clarify the criteria used to establish the timings in *Table 3-7*. The DC Electrical Specifications shown in *Table 3-6* on page 18 are not altered by this clarification. The valid input signal levels remain  $V_{IH}$  and  $V_{IL}$ .

The input setup times shown as 10a in *Table 3-7* specify the required time from the input signal crossing  $V_M$  to the rising edge of SYSCLK crossing  $V_M$ .

For the timings in *Table 3-7* to be valid, the falling edge of the input signal shown in *Table 3-7* is assumed to transition through  $V_M$  and cross  $V_{IL-AC}$  at the slew rate specified in *Table 3-7*. Input signals that do not reach the  $V_{IL-AC}$  boundary, or slew from  $V_M$  to  $V_{IL-AC}$  more slowly than specified, will result in longer input setup times.

In the same way, on the rising edge, the input signal must continue past  $V_M$  and cross the  $V_{IH-AC}$  boundary within the specified minimum slew rate. Input signals that do not reach the  $V_{IH-AC}$  boundary within the slew rate specified will result in longer input setup times.

Figure 3-4 provides the input timing diagram for the 750CL.

## Figure 3-3. Input Timing Definition

## Figure 3-4. Input Timing Diagram

Figure 3-5 provides the mode select input timing diagram for the 750CL.

## Figure 3-5. Mode Select Input Timing Diagram

## 3.6 60x Bus Output AC Specifications

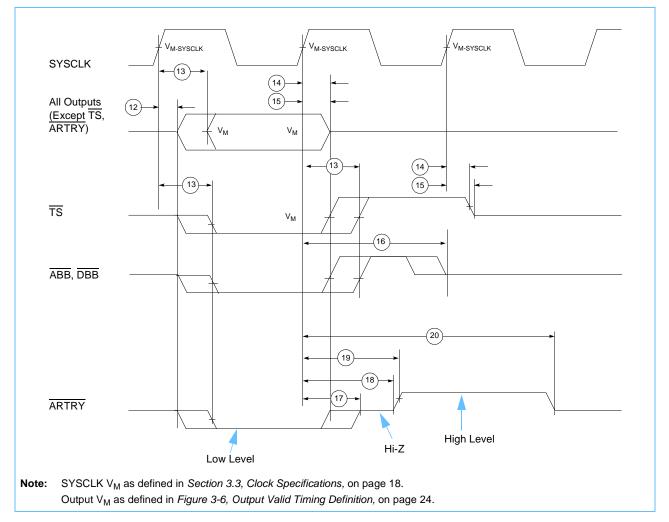

*Table 3-8* provides the 60× bus output AC timing specifications for the 750CL as defined in *Figure 3-7* on page 25.

#### *Table 3-8. 60x Bus Output AC Timing Specifications* See *Table 3-2* on page 15 for operating conditions.<sup>1, 4, 6</sup>

| Figure 3-7          | Characteristic                                                                                                                                     | 1.15 V N                   | lode | 1.8 V M | ode  | Unit                | Notoo |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|---------|------|---------------------|-------|

| Timing<br>Reference | Characteristic                                                                                                                                     | Min.                       | Max. | Min.    | Max. | Unit                | Notes |

| 12                  | SYSCLK to Output Driven<br>(Output Enable Time)                                                                                                    | 200                        | —    | TBD     | —    | ps                  |       |

| 13                  | SYSCLK to Output Valid                                                                                                                             | —                          | 2.6  | —       | 2.6  | ns                  | 5     |

| 14                  | SYSCLK to Output Invalid (Output Hold)                                                                                                             | 500                        | -    | 400     | -    | ps                  |       |

| 15                  | SYSCLK to Output High Impedance<br>(all signals <u>exc</u> ept address retry [AR <u>TRY</u> ], address<br>bus busy [ABB], and data bus busy [DBB]) | _                          | 2.8  | _       | TBD  | ns                  |       |

| 16                  | SYSCLK to $\overline{\text{ABB}}$ and $\overline{\text{DBB}}$ high impedance after precharge                                                       | _                          | 1.0  | —       | 1.0  | t <sub>SYSCLK</sub> | 2     |

| 17                  | SYSCLK to ARTRY high impedance before precharge                                                                                                    | _                          | 2.7  | —       | TBD  | ps                  |       |

| 18                  | SYSCLK to ARTRY precharge enable                                                                                                                   | (0.2 x tsy-<br>sclk) + 0.2 | _    | TBD     |      | ps                  | 3     |

| 19                  | Maximum delay to ARTRY precharge                                                                                                                   | _                          | 1.0  |         | 1.0  | t <sub>SYSCLK</sub> | 2, 3  |

| 20                  | SYSCLK to ARTRY high impedance after precharge                                                                                                     | —                          | 2.0  |         | 2.0  | t <sub>SYSCLK</sub> | 2, 3  |

Notes:

- All output specifications are measured from the V<sub>M</sub> of the rising edge of SYSCLK to the midpoint of the output signal in question using a test load as shown in *Figure 3-6* on page 24. Both input and output timings are measured at the pin. Timings are determined by design.

- 2. t<sub>SYSCLK</sub> is the period of the external bus clock (SYSCLK) in nanoseconds (ns). The numbers given in the table must be multiplied by the period of SYSCLK to <u>compute</u> the actual time duration of the parameter in question.

3. Nominal precharge width for  $\overline{\text{ARTRY}}$  is 1.0 t<sub>SYSCLK</sub>.

- 4. Guaranteed by design and characterization, and not tested.

- 5. Output Valid timing increases as the  $V_{\text{DD}}$  is reduced. These values assume a  $V_{\text{DD}}$  minimum of 1.21 V.

6. See Figure 3-6 on page 24 and Figure 3-7 on page 25 for output loading and timing definitions.

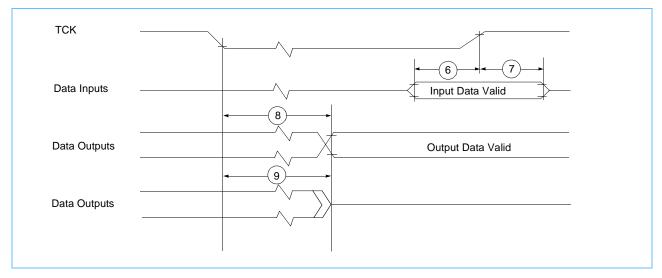

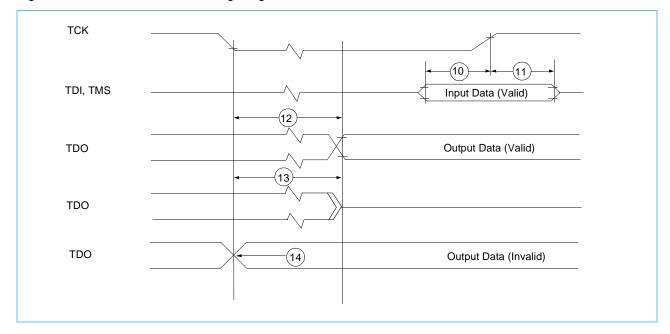

#### 3.6.1 IEEE 1149.1 AC Timing Specifications

*Table 3-9* provides the IEEE 1149.1 (JTAG) AC timing specifications. The five JTAG signals are: test data input (TDI), test data output (TDO), test mode select (TMS), test clock (TCK), and test reset (TRST).

# Table 3-9. JTAG AC Timing Specifications (Independent of SYSCLK)See Table 3-2 on page 15 for operating conditions.

| Num | Characteristic                                | Min. | Max. | Unit | Notes |

|-----|-----------------------------------------------|------|------|------|-------|

|     | TCK frequency of operation                    |      | 25   | MHz  |       |

| 1   | TCK cycle time                                | 40   | —    | ns   |       |

| 2   | TCK clock pulse width measured at +0.55V      | 15   | —    | ns   |       |

| 3   | TCK rise and fall times                       | 0    | 2    | ns   | 4     |

| 4   | Specification obsolete, intentionally omitted | —    | —    | —    |       |

| 5   | TRST assert time                              | 25   | —    | ns   | 1     |

| 6   | Boundary-scan input data setup time           | 0    | —    | ns   | 2     |

| 7   | Boundary-scan input data hold time            | 13   | —    | ns   | 2     |

| 8   | TCK to output data valid                      | —    | 8    | ns   | 3, 5  |

| 9   | TCK to output high impedance                  | 3    | 19   | ns   | 3, 4  |

| 10  | TMS, TDI data setup time                      | 0    | —    | ns   |       |

| 11  | TMS, TDI data hold time                       | 15   | —    | ns   |       |

| 12  | TCK to TDO data valid                         |      | 12   | ns   | 5     |

| 13  | TCK to TDO high impedance                     |      | 9    | ns   | 4     |

| 14  | TCK to output data invalid (output hold)      |      | —    | ns   |       |

Notes:

1. TRST is an asynchronous level sensitive signal. Guaranteed by design.

2. Non-JTAG signal input timing with respect to TCK.

3. Non-JTAG signal output timing with respect to TCK.

4. Guaranteed by characterization and not tested.

5. Minimum specification guaranteed by characterization and not tested.

Figure 3-8 provides the JTAG clock input timing diagram.

## Figure 3-8. JTAG Clock Input Timing Diagram

Figure 3-9 provides the  $\overline{\text{TRST}}$  timing diagram.

## Figure 3-9. TRST Timing Diagram

Figure 3-10 provides the boundary-scan timing diagram.

Figure 3-10. Boundary-Scan Timing Diagram

Figure 3-11 provides the test access port timing diagram.

Figure 3-11. Test Access Port Timing Diagram

# 4. Dimensions and Signal Assignments

IBM offers a plastic ball grid array (FC-PBGA) that supports 292 balls for the 750CL package. This is a signal and power compatible footprint to the PowerPC 750GX RISC Microprocessor module. The 750CL pinout, power dissipation, timing, and signal definitions are not 100% identical to the 750GX. See *PowerPC* 750CL *DD1.2 Differences from 750GX Application Note* for details.

## 4.1 Package

## 4.1.1 Overview

FC-PBGA packages are suited for applications requiring much higher I/O counts and better electrical performance than that offered by EPBGA and HPBGA packages. They are recommended for applications having medium electrical performance and power dissipation requirements.

## 4.1.2 Features

- Low dielectric-constant organic build-up substrate

- Flip chip die attach; BGA second-level interconnect

- Two-layer core

- JEDEC-compliant packages

## 4.2 Mechanical Specifications

Detail "Z": FCPBGA Cross Section

Figure 4-2. Package Drawing (Top View)

#### Notes:

The terminal A1 corner must be identified on the top surface of the package by using a corner chamfer, ink, laser or metallized markings, indentation, or other feature of package body. a distinguishing feature is allowable on the bottom surface of the package to identify the terminal A1 corner. 2 Package conforms to JEDEC Design standard MS-034.

## 4.3 Microprocessor Ball Placement

## Figure 4-3. PowerPC 750CL Microprocessor Ball Placement

| 20 | A6    | A8    | A3   | A2   | A0   | DH31 | DH25 | DH26 | NB     | DH22 | DH19 | DH18       | DH16 | DH15 | DH14 | NB      | DH9          | DH10 | DH4       | DH2       |

|----|-------|-------|------|------|------|------|------|------|--------|------|------|------------|------|------|------|---------|--------------|------|-----------|-----------|

| 19 | A13   | GND   | A5   | A4   | A1   | DH29 | NB   | DH28 | DH23   | DH24 | DH21 | DH20       | NB   | DH17 | DH11 | DH8     | DH6          | DH5  | GND       | DH3       |

| 18 | A11   | A10   |      | OVDD | GND  |      | ovdd | GND  |        | VDD  | VDD  |            | GND  | OVDD |      | GND     | OVDD         |      | DH0       | PLL_CFG0  |

| 17 | A12   | TT1   | OVDD |      | A9   |      | DH30 | DH27 |        | GND  | GND  |            | DH12 | DH13 |      | DH1     |              | OVDD | PLL_CFG1  | PLL_CFG2  |

| 16 | A14   | A15   | GND  | NB   | A7   |      | GND  | OVDD |        | OVDD | OVDD |            | OVDD | GND  |      | DH7     | PLL_CFG3     | GND  | SYSCLK    | EFUSE     |

| 15 | ттз   | TS    |      |      |      | VDD  |      |      |        |      |      |            |      |      | VDD  |         |              |      | SYSCLK    | AVDD      |

| 14 | TSIZ0 | TT2   | OVDD | тто  | GND  |      | ovdd |      |        | GND  | GND  |            |      | OVDD |      | GND     | NB           | OVDD | PLL_CFG4  | AGND      |

| 13 | NB    | TT4   | GND  | NB   | VDD  |      | GND  | GND  | VDD    | VDD  | VDD  | VDD        | GND  | GND  |      | VDD     | LSSD<br>MODE | GND  | L2_TSTCLK | L1_TSTCLK |

| 12 | TA    | TSIZ1 |      |      |      | VDD  |      | GND  | GND    |      |      | GND        | GND  |      | VDD  |         |              |      | MCP       | CKSTP_OUT |

| 11 | TBST  | TSIZ2 | VDD  | GND  | OVDD | GND  |      |      |        | VDD  | VDD  |            |      |      | GND  | OVDD    | GND          | VDD  | TLBISYNC  | HRESET    |

| 10 | NB    | A16   | VDD  | GND  | OVDD | GND  |      |      |        | GND  | GND  |            |      |      | GND  | OVDD    | GND          | VDD  | SMI       | CKSTP_IN  |

| 9  | A18   | A17   |      |      |      | VDD  |      | GND  | VDD    |      |      | VDD        | GND  |      | VDD  |         |              |      | BVSEL     | INT       |

| 8  | AACK  | NB    | GND  | A21  | VDD  |      | GND  | GND  | VDD    | VDD  | VDD  | VDD        | GND  | GND  |      | VDD     | QREQ         | GND  | NB        | QACK      |

| 7  | A20   | A19   | OVDD | A24  | GND  |      | OVDD |      |        | GND  | GND  |            |      | OVDD |      | GND     | DBB          | OVDD | ARTRY     | SRESET    |

| 6  | DBWO  | A23   |      |      |      | VDD  |      |      | THRMD2 |      |      | THRM<br>D1 |      |      | VDD  |         |              |      | TEA       | ABB       |

| 5  | A22   | A26   | GND  | A25  | A31  |      | GND  | OVDD |        | OVDD | OVDD |            | OVDD | GND  |      | CLK_OUT | WT           | GND  | TDO       | DBG       |

| 4  | A28   | A27   | OVDD |      | DL3  |      | NB   | DL13 |        | GND  | GND  |            | DL23 | DL26 |      | CI      |              | ovdd | BG        | NB        |

| 3  | A29   | A30   |      | ovdd | GND  |      | OVDD | GND  |        | VDD  | VDD  |            | GND  | ovdd |      | GND     | OVDD         |      | DRTRY     | BR        |

| 2  | DL0   | GND   | DL2  | DL6  | DL5  | DL11 | DL10 | DL12 | DL16   | DL15 | DL19 | DL20       | DL22 | DL27 | DL28 | тск     | DL30         | TDI  | GND       | KVDD      |

| 1  | DL1   | NB    | DL4  | DL8  | DL7  | DL9  | DL14 | NB   | DL18   | DL17 | DL21 | NB         | DL24 | DL25 | DL29 | DL31    | TRST         | TMS  | GBL       | KGND      |

|    | Α     | в     | С    | D    | Е    | F    | G    | Н    | J      | к    | L    | М          | N    | Р    | R    | Т       | U            | ۷    | w         | Y         |

Note: This view is looking down from above the 750CL placed and soldered on the system board.

NB: There is no ball in this position.

blank: There is no ball in this position.

NC: No connect - do not connect to this ball.

## **4.4 Pinout Listings**

*Table 4-1* contains the pinout listing for the 750CL FCPBGA package.

Table 4-1. Pinout Listing for the FC-PBGA Package

| Signal Name      | Pin Number                                                                                                                                                              | Active | Input/Output | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-------|

| A[0:31]          | E20, E19, D20, C20, D19, C19, A20, E16, B20, E17,<br>B18, A18, A17, A19, A16, B16, B10, B9, A9, B7, A7,<br>D8, A5, B6, D7, D5, B5, B4, A4, A3, B3, E5.                  | High   | Input/Output |       |

| AACK             | A8                                                                                                                                                                      | Low    | Input        |       |

| ABB              | Y6                                                                                                                                                                      | Low    | Input/Output |       |

| AGND             | Y14                                                                                                                                                                     | _      | —            |       |

| ARTRY            | W7                                                                                                                                                                      | Low    | Input/Output |       |

| AV <sub>DD</sub> | Y15                                                                                                                                                                     | _      | —            |       |

| 3G               | W4                                                                                                                                                                      | Low    | Input        |       |

| 3R               | Y3                                                                                                                                                                      | Low    | Output       |       |

| BVSEL            | W9                                                                                                                                                                      | _      | Input        | 3     |

| CKSTP_OUT        | Y12                                                                                                                                                                     | Low    | Output       |       |

|                  | T4                                                                                                                                                                      | Low    | Output       |       |

| CKSTP_IN         | Y10                                                                                                                                                                     | Low    | Input        |       |

| CLK_OUT          | Т5                                                                                                                                                                      |        | Output       |       |

| DBB              | U7                                                                                                                                                                      | Low    | Output       |       |

| DBG              | Y5                                                                                                                                                                      | Low    | Input        |       |

| DBWO             | A6                                                                                                                                                                      | Low    | Input        |       |

| DH[0:31]         | W18, T17, Y20, Y19, W20, V19, U19, T16, T19, U20,<br>V20, R19, N17, P17, R20, P20, N20, P19, M20, L20,<br>M19, L19, K20, J19, K19, G20, H20, H17, H19, F19,<br>G17, F20 | High   | Input/Output |       |

| DL[0:31]         | A2, A1, C2, E4, C1, E2, D2, E1, D1, F1, G2, F2, H2,<br>H4, G1, K2, J2, K1, J1, L2, M2, L1, N2, N4, N1, P1, P4,<br>P2, R2, R1, U2, T1                                    | High   | Input/Output |       |

| DRTRY            | W3                                                                                                                                                                      | Low    | Input        |       |

| FUSE             | Y16                                                                                                                                                                     | N/A    | Input        | 8     |

| BBL              | W1                                                                                                                                                                      | Low    | Input/Output |       |

Notes:

1. These are test signals for factory use only and must be pulled up to OV<sub>DD</sub> for normal machine operation.

2.  $OV_{DD}$  inputs supply power to the input/output drivers and  $V_{DD}$  inputs supply power to the processor core.

3. BVSEL low selects single-ended clock input on SYSCLK. BVSEL high selects differential clock input on SYSCLK and SYSCLK.

4. TCK must be tied high or low for normal machine operation.

5. No connect. Do not connect a net to this ball.

6. SYSCLK# is a differential clock input used with SYSCLK. When using a single-ended clock, ground SYSCLK#.

7. Must be connected to OVdd during normal operation.

8. Must be connected to GND during normal operation.

9. Kelvin V<sub>DD</sub> and GND for voltage regulator sensing.

10. On DD1.x this signal must be pulled up to OVdd for normal operation. On DD2.x, this signal selects the I/O operating voltage such that a pull down to GND selects 1.8V and a pull up to OVdd selects 1.15V.

| Table 11    | Discould interve form |             | D = = 1 - = = = |             |

|-------------|-----------------------|-------------|-----------------|-------------|

| 1 able 4-1. | Pinout Listing for t  | Ine FC-PBGA | Package         | (Continuea) |

| Signal Name      | Pin Number                                                                                                                                                                                                                                                                                        | Active | Input/Output | Notes |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------|-------|

| GND              | B2, B19, C5, C8, C13, C16, D10, D11, E3, E7, E14,<br>E18, F10, F11, G5, G8, G13, G16, H3, H8, H9, H12,<br>H13, H18, J12, K4, K7, K10, K14, K17, L4, L7, L10,<br>L14, L17, M12, N3, N8, N9, N12, N13, N18, P5, P8.<br>P13, P16, R10, R11, T3, T7, T14, T18, U10, U11, V5,<br>V8, V13,V16, W2, W19, | _      | _            |       |

| HRESET           | Y11                                                                                                                                                                                                                                                                                               | Low    | Input        |       |

| INT              | Y9                                                                                                                                                                                                                                                                                                | Low    | Input        |       |

| KGND             | Y1                                                                                                                                                                                                                                                                                                | —      | —            | 9     |

| KV <sub>DD</sub> | Y2                                                                                                                                                                                                                                                                                                | —      | —            | 9     |

| L1_TSTCLK        | Y13                                                                                                                                                                                                                                                                                               | High   | Input        | 8     |

| L2_TSTCLK        | W13                                                                                                                                                                                                                                                                                               | High   | Input        | 10    |

| LSSD_MODE        | U13                                                                                                                                                                                                                                                                                               | Low    | Input        | 1     |

| MCP              | W12                                                                                                                                                                                                                                                                                               | Low    | Input        |       |

| NB               | U14, Y4, D16, D13, A13, B8, T20, N19, J20, G19, B1,<br>G4, H1, M1, A10, W8                                                                                                                                                                                                                        | _      | _            | 5     |

| OV <sub>DD</sub> | C4, C7, C14, C17, D3, D18, E10, E11, G3, G7, G14,<br>G18, H5, H16, K5, K16, L5, L16, N5, N16, P3, P7, P14,<br>P18, T10, T11, U3, U18, V4, V7, V14, V17                                                                                                                                            | _      | _            | 2     |

| PLL_CFG[0:4]     | Y18, W17, Y17, U16, W14                                                                                                                                                                                                                                                                           | High   | Input        |       |

| QACK             | Y8                                                                                                                                                                                                                                                                                                | Low    | Input        |       |

| QREQ             | U8                                                                                                                                                                                                                                                                                                | Low    | Output       |       |

| SMI              | W10                                                                                                                                                                                                                                                                                               | Low    | Input        |       |

| SRESET           | Y7                                                                                                                                                                                                                                                                                                | Low    | Input        |       |

| SYSCLK           | W16                                                                                                                                                                                                                                                                                               | High   | Input        | 6     |

| SYSCLK           | W15                                                                                                                                                                                                                                                                                               | Low    | Input        | 6     |

| TA               | A12                                                                                                                                                                                                                                                                                               | Low    | Input        |       |

| TBST             | A11                                                                                                                                                                                                                                                                                               | Low    | Input/Output |       |

| ТСК              | T2                                                                                                                                                                                                                                                                                                | High   | Input        | 4     |

| TDI              | V2                                                                                                                                                                                                                                                                                                | High   | Input        |       |

| TDO              | W5                                                                                                                                                                                                                                                                                                | High   | Output       |       |

| TEA              | W6                                                                                                                                                                                                                                                                                                | Low    | Input        |       |

Notes:

- 1. These are test signals for factory use only and must be pulled up to  $\text{OV}_{\text{DD}}$  for normal machine operation.

- 2.  $OV_{DD}$  inputs supply power to the input/output drivers and  $V_{DD}$  inputs supply power to the processor core.

- 3. BVSEL low selects single-ended clock input on SYSCLK. BVSEL high selects differential clock input on SYSCLK and SYSCLK.

- 4. TCK must be tied high or low for normal machine operation.

- 5. No connect. Do not connect a net to this ball.

- 6. SYSCLK# is a differential clock input used with SYSCLK. When using a single-ended clock, ground SYSCLK#.

- 7. Must be connected to OVdd during normal operation.

- 8. Must be connected to GND during normal operation.

- 9. Kelvin  $V_{\text{DD}}$  and GND for voltage regulator sensing.

- 10. On DD1.x this signal must be pulled up to OVdd for normal operation. On DD2.x, this signal selects the I/O operating voltage such that a pull down to GND selects 1.8V and a pull up to OVdd selects 1.15V.

#### Table 4-1. Pinout Listing for the FC-PBGA Package (Continued)

| Signal Name     | Pin Number                                                                                                                                             | Active | Input/Output    | Notes |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-----------------|-------|--|

| THRMD1          | M6                                                                                                                                                     |        |                 |       |  |

| THRMD2          | J6                                                                                                                                                     | c      | See Section 5.6 |       |  |

| TLBISYNC        | W11                                                                                                                                                    | Low    | Input           |       |  |

| TMS             | V1                                                                                                                                                     | High   | Input           |       |  |

| TRST            | U1                                                                                                                                                     | Low    | Input           |       |  |

| TS              | B15                                                                                                                                                    | Low    | Input/Output    |       |  |

| TSIZ[0:2]       | A14, B12, B11                                                                                                                                          | High   | Output          |       |  |

| TT[0:4]         | D14, B17, B14, A15, B13                                                                                                                                | High   | Input/Output    |       |  |

| V <sub>DD</sub> | C10, C11, E8, E13, F6, F9, F12, F15, J8, J9, J13, K3,<br>K8, K11, K13, K18, L3, L8, L11, L13, L18, M8, M9,<br>M13, R6, R9, R12, R15, T8, T13, V10, V11 | —      | _               | 2     |  |

| WT              | U5                                                                                                                                                     | Low    | Output          |       |  |

#### Notes:

1. These are test signals for factory use only and must be pulled up to OV<sub>DD</sub> for normal machine operation.

2. OV<sub>DD</sub> inputs supply power to the input/output drivers and V<sub>DD</sub> inputs supply power to the processor core.

3. BVSEL low selects single-ended clock input on SYSCLK. BVSEL high selects differential clock input on SYSCLK and SYSCLK.

4. TCK must be tied high or low for normal machine operation.

5. No connect. Do not connect a net to this ball.

6. SYSCLK# is a differential clock input used with SYSCLK. When using a single-ended clock, ground SYSCLK#.

7. Must be connected to OVdd during normal operation.

8. Must be connected to GND during normal operation.

9. Kelvin V<sub>DD</sub> and GND for voltage regulator sensing.

10. On DD1.x this signal must be pulled up to OVdd for normal operation. On DD2.x, this signal selects the I/O operating voltage such that a pull down to GND selects 1.8V and a pull up to OVdd selects 1.15V.

# 5. System Design Information

This section provides electrical and thermal design recommendations for successful applications on the 750CL.

## 5.1 Reference Clock Selection

PowerPC 750CL Microprocessor supports either a single-ended or differential clock inputs. The reference clock is selected with the pin BVSEL. BVSEL set to GND selects a single-ended reference clock. BVSEL set to OV<sub>DD</sub> selects differential clock inputs.

For single-ended clock operation, the reference clock should be applied to pin SYSCLK. The pin SYSCLK should be tied to GND.

For differential clock operation, the differential reference clocks should be applied to pin SYSCLK and SYSCLK. The recommended board terminations are either:

- 1. 50ohms impedance to GND on pin SYSCLK and 50 ohms impedance to GND on pin SYSCLK. or

- 2. 100 ohms impedance between pins SYSCLK and SYSCLK.

## 5.2 PLL Configuration

Table 5-1 shows the PLL configuration for the 750CL for nominal frequencies.

| PLL_CFG [0:4] |         | Processor to Bus Frequency Ratio |

|---------------|---------|----------------------------------|

| Binary        | Decimal | (PTBFR)                          |

| 00100         | 4       | 2×                               |

| 00101         | 5       | 2.5×                             |

| 00110         | 6       | 3×                               |

| 00111         | 7       | 3.5×                             |

| 01000         | 8       | 4x                               |

| 01001         | 9       | 4.5×                             |

| 01010         | 10      | 5×                               |

| 01011         | 11      | 5.5×                             |

| 01100         | 12      | 6×                               |

| 01101         | 13      | 6.5×                             |

| 01110         | 14      | 7x                               |

| 01111         | 15      | 7.5×                             |

#### Notes:

1. The SYSCLK frequency equals the core frequency divided by the processor-to-bus frequency ratio (PTBFR).

2. In clock-off mode, no clocking occurs inside the 750CL regardless of the SYSCLK input.

3. In PLL-bypass mode, the SYSCLK input signal clocks the internal processor directly, the PLL is disabled, and the bus mode is set for 1:1 mode operation. This mode is intended for factory use only.

The AC timing specifications given in the document do not apply in PLL-bypass mode.

#### Table 5-1. 750CL Microprocessor PLL Configuration (Continued)

| PLL_C  | FG [0:4] | Processor to Bus Frequency Ratio |

|--------|----------|----------------------------------|

| Binary | Decimal  | (PTBFR)                          |

| 10000  | 16       | 8x                               |

| 10001  | 17       | 8.5×                             |

| 10010  | 18       | 9×                               |

| 10011  | 19       | 9.5×                             |

| 10100  | 20       | 10x                              |

Notes:

1. The SYSCLK frequency equals the core frequency divided by the processor-to-bus frequency ratio (PTBFR).

2. In clock-off mode, no clocking occurs inside the 750CL regardless of the SYSCLK input.