# Am186™CC/CH/CU Microcontroller Customer Development Platform

**User's Manual**

Order #22002B

© Copyright 1999 Advanced Micro Devices, Inc. All rights reserved.

The contents of this document are provided in connection with Advanced Micro Devices, Inc. ("AMD") products. AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this publication. Except as set forth in AMD's Standard Terms and Conditions of Sale, AMD assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

AMD's products are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or in any other application in which the failure of AMD's product could create a situation where personal injury, death, or severe property or environmental damage may occur. AMD reserves the right to discontinue or make changes to its products at any time without notice.

AMD, the AMD logo, combinations thereof, Am186, Am188, Comm86, DSLAC, E86, E86MON, PCnet, and SmartDMA are trademarks of Advanced Micro Devices, Inc.

FusionE86 is a service mark of Advanced Micro Devices, Inc.

Microsoft and Windows are registered trademarks of Microsoft Corp.

Other product or brand names are used solely for identification and may be the trademarks or registered trademarks of their respective companies.

#### IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86<sup>TM</sup> family hardware and software development questions.

Frequently accessed numbers are listed below. Additional contact information is listed on the back of this manual. AMD's WWW site lists the latest phone numbers.

#### **Technical Support**

Answers to technical questions are available online, through e-mail, and by telephone.

Go to AMD's home page at www.amd.com and follow the Service link for the latest AMD technical support phone numbers, software, and Frequently Asked Questions.

For technical support questions on all E86 products, send e-mail to epd.support@amd.com (in the US and Canada) or euro.tech@amd.com (in Europe and the UK).

You can also call the AMD Corporate Applications Hotline at:

Toll-free for U.S. and Canada (800) 222-9323 44-(0) 1276-803-299 U.K. and Europe hotline

#### **WWW Support**

For specific information on E86 products, access the AMD home page at www.amd.com and follow the Embedded Processors link. These pages provide information on upcoming product releases. overviews of existing products, information on product support and tools, and a list of technical documentation. Support tools include online benchmarking tools and CodeKit software—tested source code example applications. Many of the technical documents are available online in PDF form.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to webmaster@amd.com.

#### **Documentation and Literature Support**

Data books, user's manuals, data sheets, application notes, and product CDs are free with a simple phone call. Internationally, contact your local AMD sales office for product literature.

To order literature, call:

(800) 222-9323 Toll-free for U.S. and Canada (512) 602-5651 Direct dial worldwide

(512) 602-7639

#### Third-Party Support

AMD FusionE86<sup>SM</sup> partners provide an array of products designed to meet critical time-to-market needs. Products and solutions available include emulators, hardware and software debuggers, board-level products, and software development tools, among others. The WWW site and the E86<sup>TM</sup> Family Products Development Tools CD, order #21058, describe these solutions. In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

### **Contents**

## About the Am186™CC/CH/CU Microcontroller Customer Development Platform

| Main Board Block Diagram         | XV          |

|----------------------------------|-------------|

| Development Module Block Diagram | <b>xv</b> i |

| Theory of Operation              | xvii        |

| Features                         | xvii        |

| Main Board                       | xvii        |

| Development Module               | xviii       |

| Documentation                    | xix         |

| About This Manual                | xix         |

| Suggested Reference Material     | XX          |

| Documentation Conventions        | XX          |

#### Chapter 1

#### **Quick Start**

| Connecting to a PC via a Serial Port                | 1-2 |

|-----------------------------------------------------|-----|

| Installation Requirements                           | 1-2 |

| Main Board Installation                             | 1-2 |

| Connecting to a PC via a USB port                   | 1-5 |

| Connecting the Development Module to the Main Board | 1-5 |

| Connecting a TIP to the Main Board                  | 1-6 |

| Connecting a ROM-ICE to the Main Board              | 1-7 |

| Troubleshooting Installation Problems | 1-8 |

|---------------------------------------|-----|

| For More Information.                 | 1-9 |

#### Chapter 2

### **Main Board Functional Description**

| Main Board Layout                                  | 2-2  |

|----------------------------------------------------|------|

| Main Board Features                                | 2-8  |

| Am186 <sup>TM</sup> CC/CH/CU Microcontroller (J14) | 2-8  |

| Power Supply (A1)                                  | 2-15 |

| Memory Interfaces                                  | 2-20 |

| Communication Interfaces                           | 2-27 |

| Debug and Configuration Circuitry                  | 2-39 |

| Expansion Interfaces                               | 2-49 |

|                                                    |      |

#### Chapter 3

### **Development Module Functional Description**

| Development Module Layout                                 | 3-2  |

|-----------------------------------------------------------|------|

| Customer Development Platform Development Module Features | 3-4  |

| Main Board Interface                                      | 3-4  |

| 10BaseT Ethernet Interface                                | 3-7  |

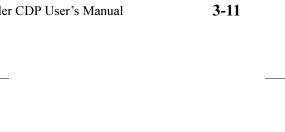

| ISDN Interface                                            | 3-12 |

| POTS Interface                                            | 3-18 |

#### Appendix A

| Default Jumper and Switch Settings |                                   |     |

|------------------------------------|-----------------------------------|-----|

| Default Jumper and Sw              | efault Jumper and Switch Settings |     |

| Appandix P                         |                                   |     |

| Appendix B                         |                                   |     |

| Platform Pin Usage                 |                                   |     |

| Platform Pin Usage                 |                                   | B-1 |

|                                    |                                   |     |

| Appendix C                         |                                   |     |

| Main Board Bill of Mat             | erials                            |     |

| Main Board Bill of Ma              | terials                           |     |

|                                    |                                   |     |

| Appendix D                         |                                   |     |

| <b>Development Module</b>          | Bill of Materials                 |     |

| Development Module I               | Bill of Materials                 | D-1 |

### Appendix E

### **PLD Equations**

| PLD (U13) Equations                 | E-2  |

|-------------------------------------|------|

| PLD (U20) Equations (SBP/PCM Mode)  | E-4  |

| PLD (20) Equations (IOM-2/GCI Mode) | E-13 |

| PLD (U24) Equations                 | E-17 |

### List of Figures

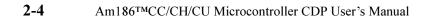

| Figure 0-1.  | Main Board Block Diagram                                      | X      |

|--------------|---------------------------------------------------------------|--------|

| Figure 0-2.  | Router/ISDN Development Module Block Diagram                  | XV     |

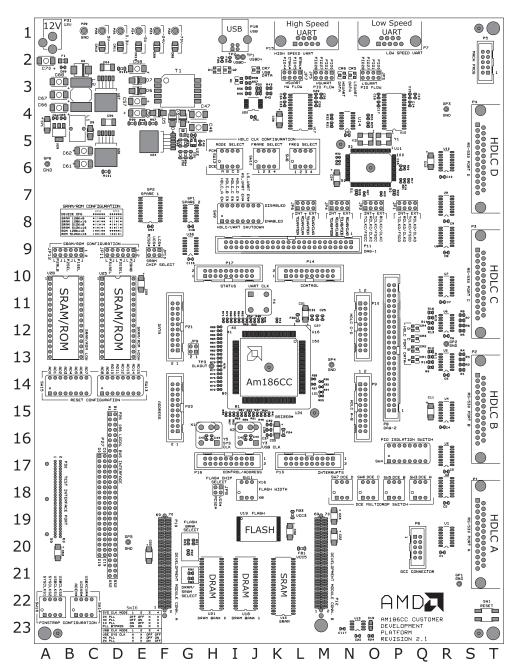

| Figure 2-1.  | Main Board Block Diagram (Same as Figure 0-1)                 | 2-2    |

| Figure 2-2.  | Main Board Layout                                             | 2-3    |

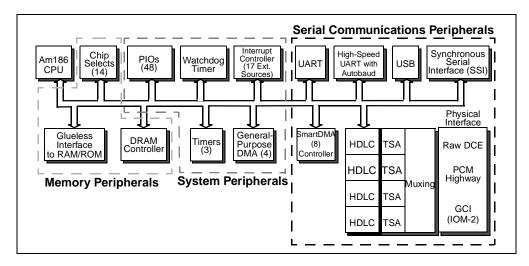

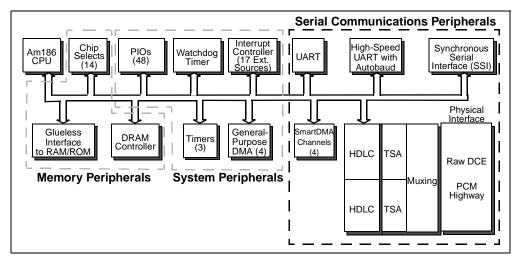

| Figure 2-3.  | Am186CC <sup>TM</sup> Communications Controller Block Diagram | 2-9    |

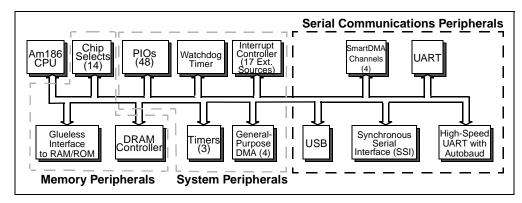

| Figure 2-4.  | Am186CH™ HDLC Microcontroller Block Diagram                   | . 2-10 |

| Figure 2-5.  | Am186CU™ USB Microcontroller Block Diagram                    | .2-10  |

| Figure 2-6.  | Am186 <sup>TM</sup> CC/CH/CU Microcontroller System Clock     | . 2-12 |

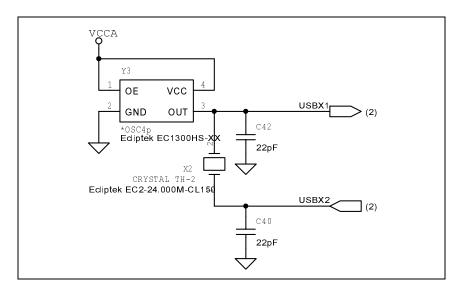

| Figure 2-7.  | Am186CC or Am186CU Microcontroller USB Clock                  | . 2-13 |

| Figure 2-8.  | Main Board Reset Circuitry                                    | . 2-14 |

| Figure 2-9.  | 5-V Power Supply                                              | . 2-1: |

| Figure 2-10. | 3.3-V Power Supply                                            | . 2-10 |

| Figure 2-11. | -5-V Power Supply                                             | . 2-10 |

| Figure 2-12. | –24-V and –70-V Power Supplies                                | .2-1   |

| Figure 2-13. | DRAM or SRAM System Memory and Flash Memory Map               | . 2-20 |

| Figure 2-14. | Main Memory DRAM Circuit                                      | .2-2   |

| Figure 2-15. | Flash Memory Circuit.                                         | . 2-22 |

| Figure 2-16. | DIP SRAM Sockets                                              | . 2-2: |

| Figure 2-17. | RS-232 Serial Port Routing                                    | . 2-29 |

| Figure 2-18. | HDLC Circuit                                                  | . 2-30 |

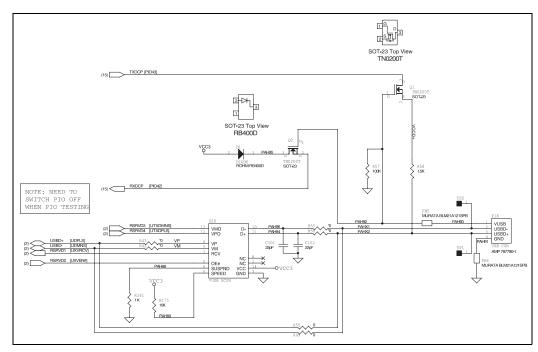

| Figure 2-19. | Universal Serial Bus Circuit                                  | . 2-38 |

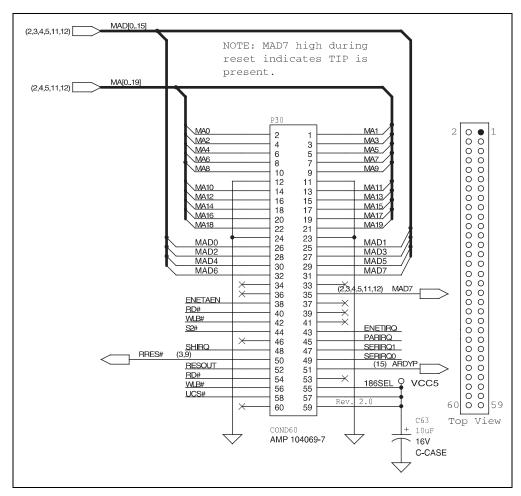

| Figure 2-20. | Test Interface Port Connector                                 | . 2-4  |

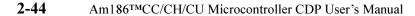

| Figure 2-21. | HP Header Grouping                                            | . 2-43 |

| Figure 2-22. | Debug Header Circuit                                          | . 2-4  |

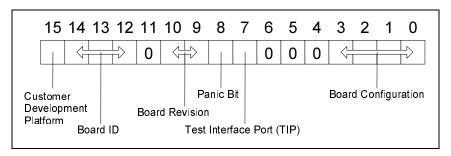

| Figure 2-23. | RESCON Register Bits                                          | . 2-4: |

| Figure 2-24. | Reset Configuration Switches                                  | . 2-40 |

| Figure 2-25. | CPU/PLL Pinstrap Circuit                                      | . 2-4′ |

| Figure 2-26. | Miscellaneous Pinstrap Circuit                                | . 2-49 |

viii

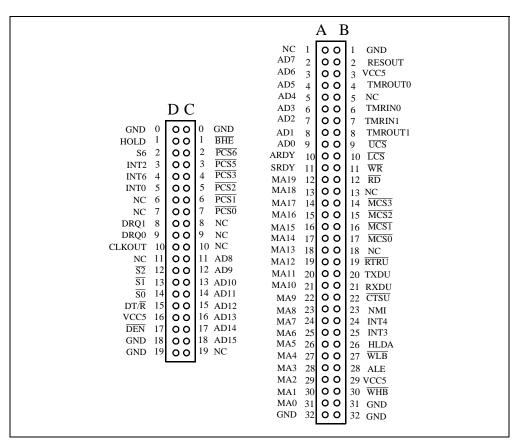

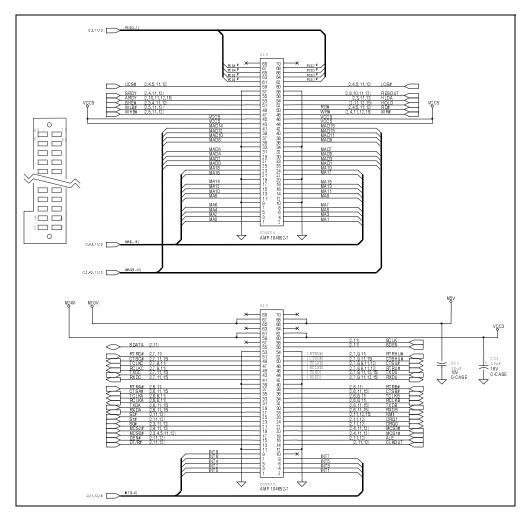

| Figure 2-27. | Am186 <sup>TM</sup> Processor Expansion Interface                 | 2-50 |

|--------------|-------------------------------------------------------------------|------|

| Figure 2-28. | Router/ISDN Development Module Interface                          | 2-52 |

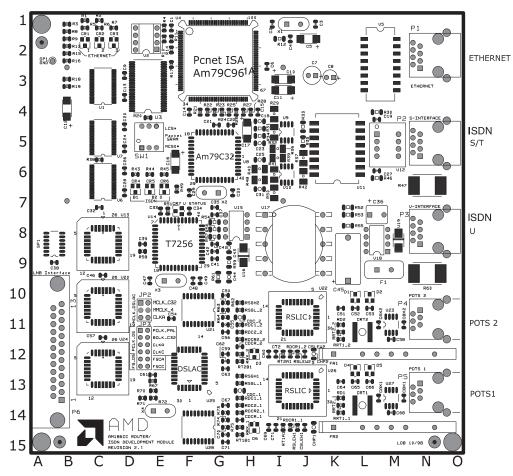

| Figure 3-1.  | Router/ISDN Development Module Block Diagram (same as Figure 0-2) | 3-2  |

| Figure 3-2.  | Router/ISDN Development Module Layout Diagram                     | 3-3  |

| Figure 3-3.  | Main Board and Development Module Connection                      | 3-5  |

| Figure 3-4.  | Router/ISDN Development Module Connector Layout Diagram           | 3-6  |

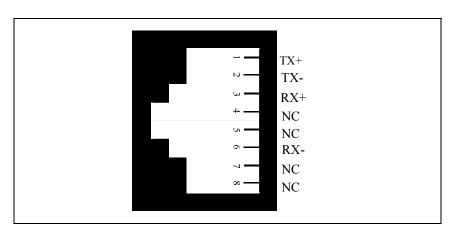

| Figure 3-5.  | Front View of the RJ-45 Connector                                 | 3-8  |

| Figure 3-6.  | 10BaseT Ethernet Interface                                        | 3-10 |

| Figure 3-7.  | Ethernet Controller Schematic                                     | 3-11 |

| Figure 3-8.  | ISDN Reference Point Block Diagram                                | 3-12 |

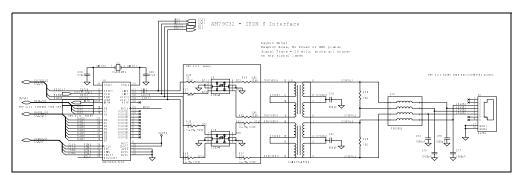

| Figure 3-9.  | ISDN S/T Interface                                                | 3-14 |

| Figure 3-10. | ISDN U Interface                                                  | 3-17 |

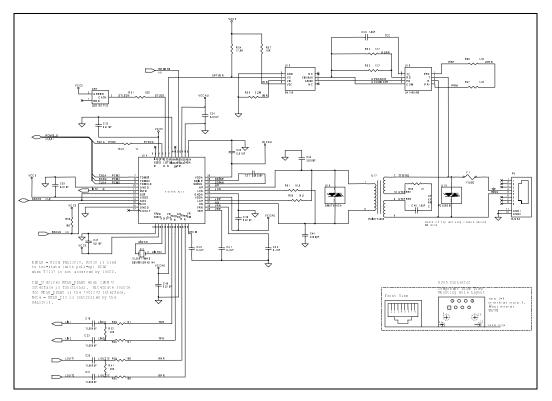

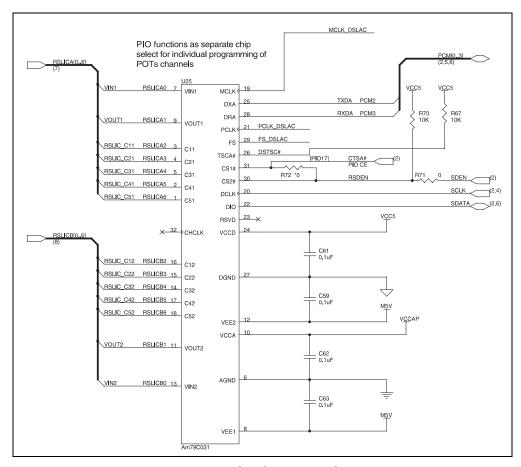

| Figure 3-11. | DSLAC <sup>TM</sup> Device Circuitry                              | 3-19 |

| Figure 3-12. | DSLAC-to-RSLIC Circuit Interface                                  | 3-24 |

| Eigung 2 12  | DTME Intenfore Cinquit                                            | 2 25 |

#### **List of Tables**

| Table 0-1.  | Notational Conventionsxx                                                                                  |

|-------------|-----------------------------------------------------------------------------------------------------------|

| Table 1-1.  | ROM-ICE Configuration                                                                                     |

| Table 1-2.  | Installation Troubleshooting                                                                              |

| Table 2-1.  | Jumpers, Switches, and Adjustments2-4                                                                     |

| Table 2-2.  | CPU and USB Clock Options2-11                                                                             |

| Table 2-3.  | Power Estimates for the CDP Main Board2-18                                                                |

| Table 2-4.  | Power Estimates for the CDP Development Module                                                            |

| Table 2-5.  | Total Power Estimates for the CDP2-19                                                                     |

| Table 2-6.  | DIP x8/x16 SRAM, ROM-ICE Device Selection                                                                 |

| Table 2-7.  | SRAM and ROM Pinouts                                                                                      |

| Table 2-8.  | Switch Options to Enable R-530 DCE Clocking2-32                                                           |

| Table 2-9.  | Switch Options to Set R-530 DCE Clocking Frequency2-32                                                    |

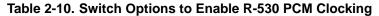

| Table 2-10. | Switch Options to Enable R-530 PCM Clocking2-33                                                           |

| Table 2-11. | Switch Options to Set R-530 PCM Clocking Frequency2-34                                                    |

| Table 2-12. | Switch Options to Set R-530 PCM Frame Sync2-35                                                            |

| Table 2-13. | HDLC DCE/PCM Clock Routing Options2-36                                                                    |

| Table 2-14. | System and USB Clock Modes                                                                                |

| Table 2-15. | CPU and USB Clocking Options                                                                              |

| Table 3-1.  | RJ-45 Connector Pin Functions                                                                             |

| Table 3-2.  | PCnet™-ISA II Ethernet Controller LED Status Information                                                  |

| Table 3-3.  | U Interface Configuration                                                                                 |

| Table 3-4.  | U Interface LED Status                                                                                    |

| Table 3-5.  | Am79C031 DSLAC <sup>TM</sup> Device PCLK/FS/MCLK Configuration3-21                                        |

| Table 3-6.  | Am186 <sup>TM</sup> CC Communications Controller/Am79C031 DSLAC <sup>TM</sup> Communication Configuration |

| Table A-1.  | Main Board Default Jumper and Switch Settings                                                             |

| Table A-2.  | Router/ISDN Development Module Default Jumper and Switch Settings A-5                                     |

| Table R-1   | PIO Usage R-1                                                                                             |

| Table B-2. | Chip Select Usage                                | B-10 |

|------------|--------------------------------------------------|------|

| Table B-3. | Platform Interrupts Pin Usage                    | B-11 |

| Table C-1. | Main Board Bill of Materials                     | C-1  |

| Table D-1. | Router/ISDN Development Module Bill of Materials | D-1  |

хi

### About the Am186™CC/CH/CU Microcontroller Customer Development Platform

The AMD Am186<sup>TM</sup>CC/CH/CU microcontroller customer development platform (CDP) is a system used for customer evaluation and development for the Am186CC/CH/CU microcontrollers. The platform provides access to the major microcontroller interfaces and is an ideal tool for developing customer-specific applications by using the development module interface.

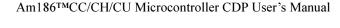

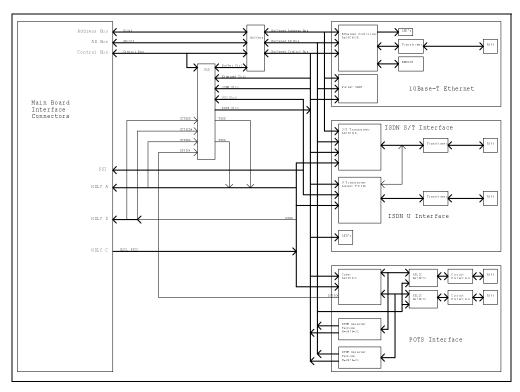

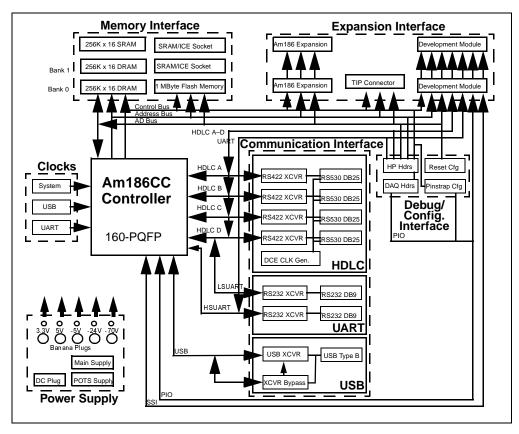

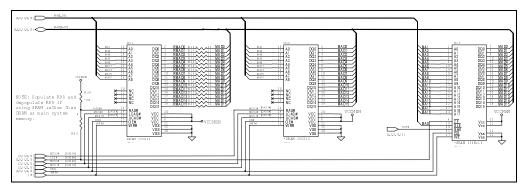

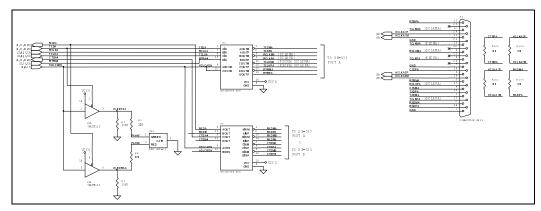

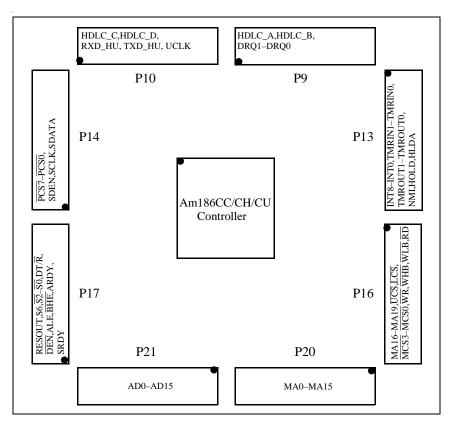

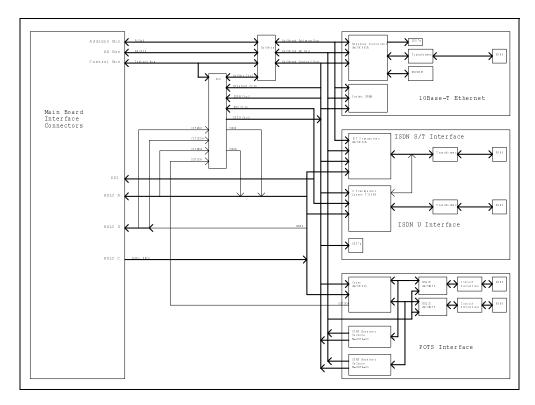

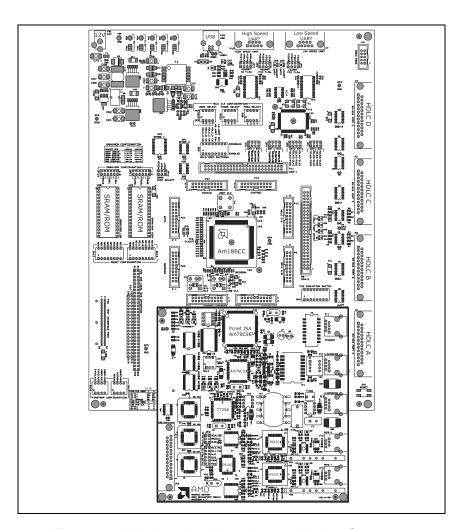

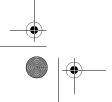

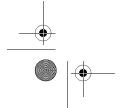

The CDP consists of two boards—a main board that contains the Am186CC communications controller and interfaces (shown in Figure 0-1), and the development module, which can be used for the development of various communications applications such as ISDN TAs and routers (shown in Figure 0-2).

The main board consists of a power supply that provides the necessary voltages for typical system applications of the Am186CC/CH/CU microcontroller. The main board also provides a glueless interface to Flash memory and DRAM or SRAM system main memory, communication interfaces such as a universal asynchronous receiver/transmitter (UART) and High-Speed UART, universal serial bus (USB), and four synchronous serial DCE connections. Other features include the debug interfaces that allow connection to the following:

- · ROM-ICE

- Optional Test Interface Port (TIP) debug board

Am186TMCC/CH/CU Microcontroller CDP User's Manual

- HP logic analyzer headers to provide access to the Am186CC communications controller signals

- Expansion interface through the development module or the 104-pin Am186 processor expansion interface

The development module consists of an Am79C961A PCnet™-ISA II Ethernet Controller for 10BaseT Ethernet, an Am79C32A ISDN digital subscriber controller (DSC) circuit for an ISDN S/T connection, an ISDN U connection, and two POTS connections featuring the Am79C031 DSLACTM device and two Am79R79 Ringing SLICs.

**NOTE:** Although the customer development board provides an Am186CC microcontroller, you can also use the board to develop Am186CH HDLC microcontroller applications and Am186CU USB microcontroller applications. The Am186CH and Am186CU microcontrollers support subsets of the Am186CC microcontroller features. The Am186CH HDLC microcontroller provides two HDLC channels and does not support USB or GCI. The Am186CU USB microcontroller does not support HDLC.

For more information about the Am186CC/CH/CU microcontrollers, refer to

- Am186<sup>TM</sup>CC/CH/CU Microcontroller User's Manual, order #21914

- Am186™CC Communications Controller Data Sheet, order #21915

- Am186<sup>TM</sup>CH HDLC Microcontroller Data Sheet, order #22024

- Am186<sup>TM</sup>CU USB Microcontroller Data Sheet, order #22025

- Am186<sup>TM</sup>CC/CH/CU Microcontroller Register Set Manual, order #21916

For more information about the CDP board features, refer to "Features" on page xvii, and Chapter 2, "Main Board Functional Description".

xiv

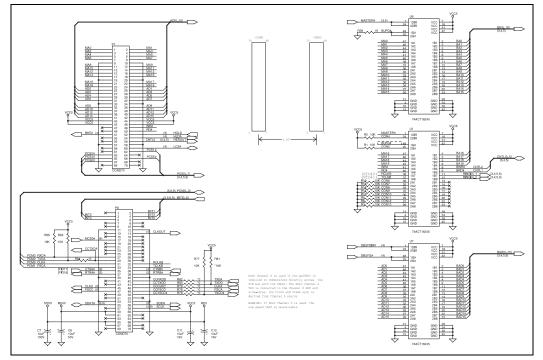

### **Main Board Block Diagram**

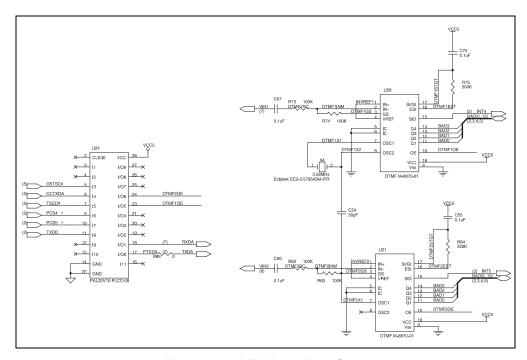

Figure 0-1 shows the block diagram for the main board on the CDP.

Figure 0-1. Main Board Block Diagram

### **Development Module Block Diagram**

Figure 0-2 (or sheet 2 of the development module schematics included in your kit) shows the block diagram for the CDP's development module.

Figure 0-2. Router/ISDN Development Module Block Diagram

xvi

### **Theory of Operation**

The Am186CC/CH/CU microcontroller CDP provides a comprehensive evaluation system to support Am186CC/CH/CU microcontroller-based designs. The combined features of the Am186CC/CH/CU microcontroller CDP offer designers a complete tool for hardware and software development with the Am186CC/CH/CU microcontrollers.

**NOTE:** If you are evaluating the Am186CH or Am186CU microcontroller, all of the features on the CDP are not available. The Am186CH and Am186CU microcontrollers support subsets of the Am186CC microcontroller features. The Am186CH HDLC microcontroller provides two HDLC channels and *does not* support USB or GCI. The Am186CU USB microcontroller *does not* support HDLC.

#### **Features**

The Am186CC/CH/CU microcontroller CDP provides the features described in the following sections.

#### **Main Board**

- Am186CC 3.3-V, 50-MHz Microcontroller

- Power Supply (generates 3.3 V, 5.0 V, -5.0 V, -24 V, and -70 V from a 12-V DC source)

- · Memory Interfaces

- Main system memory

4-Mbit, 256K x 16, 40-ns EDO DRAM

Two 1-Mbit 128K x 8, 35-ns SRAMs configured as 128K x 16

- 8-Mbit configurable 512K x 16, or 1M x 8, 55-ns Flash memory

Am186TMCC/CH/CU Microcontroller CDP User's Manual

- Communication Interfaces

- HDLC synchronous communications Four RS-422, DB-25 DCE/PCM connections clocked by the main board clock generator (Am186CH HDLC microcontroller supports only two connections) Dedicated 2 x 5 header for GCI (supported on Am186CC microcontroller only)

- Peripheral USB port (supported on Am186CC and Am186CU microcontrollers only)

- UARTs One 460-Kbaud, RS-232, DB-9 DCE connection One 120-Kbaud, RS-232, DB-9 DCE connection

- · Debug and Configuration

- 60-pin connector interface to the optional test interface port (TIP) debug board

- Two 32-pin DIP sockets for use with a x16 ROM-ICE

- Eight 2 x 10 shrouded headers to directly connect Am186CC/CH/CU microcontroller signals to HP analyzers

- Two 4-segment switches to allow pinstrap configuration

- Two 8-segment switches to allow system-specific configuration

#### **Development Module**

- 10BaseT Ethernet port

- ISDN interface

- S/T interface

- U interface

- Two POTS Interfaces

#### **Documentation**

The Am186<sup>TM</sup>CC/CH/CU Microcontroller Customer Development Platform User's Manual provides information on the design and function of the Am186CC/ CH/CU microcontroller CDP.

#### About This Manual

Chapter 1, "Quick Start" helps you quickly set up and start using the Am186CC/ CH/CU microcontroller CDP.

Chapter 2, "Main Board Functional Description" describes the basic sections of the platform: layout, jumper and switch settings, microcontroller, power supply, memory interfaces, communication interfaces, debug and configuration, and development module.

Chapter 3, "Development Module Functional Description" describes the features and components on the development module, including a 10BaseT Ethernet port, ISDN interface, and POTS interfaces.

Appendix A, "Default Jumper and Switch Settings" provides a table with the default jumper and switch settings.

Appendix B, "Platform Pin Usage" provides tables describing the CDP's PIO, chip select, and interrupt pin usage.

Appendix C, "Main Board Bill of Materials" contains the bill of materials for the Am186CC/CH/CU microcontroller CDP main board.

Appendix D, "Development Module Bill of Materials" contains the bill of materials for the Am186CC/CH/CU microcontroller CDP module.

Appendix E, "PLD Equations" contains PLD code for the PLDs at locations U13, U20, and U24.

A standard index is also included.

#### **Suggested Reference Material**

- Am186<sup>TM</sup>CC/CH/CU Microcontroller User's Manual Advanced Micro Devices, order #21914

- Am186<sup>TM</sup>CC Communications Controller Data Sheet Advanced Micro Devices, order #21915

- Am186<sup>TM</sup>CH HDLC Microcontroller Data Sheet Advanced Micro Devices, order #22024

- Am186<sup>TM</sup>CU USB Microcontroller Data Sheet Advanced Micro Devices, order #22025

- Am186<sup>TM</sup>CC/CH/CU Microcontroller Register Set Manual Advanced Micro Devices, order #21916

- Am186<sup>TM</sup> and Am188<sup>TM</sup> Family Instruction Set Manual Advanced Micro Devices, order #21076

- E86MON<sup>TM</sup> Software User's Manual Advanced Micro Devices, order #21891

- E86<sup>TM</sup> Family Products and Development Tools CD Advanced Micro Devices, order #21508

#### **Documentation Conventions**

Table 0-1. Notational Conventions

| Symbol          | Usage                                                                                                                           |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------|

| Boldface        | Indicates that characters must be entered exactly as shown, except that the alphabetic case is only significant when indicated. |

| Typewriter face | Indicates computer text input or output in an example or listing.                                                               |

### Chapter 1

### **Quick Start**

This chapter provides information that will help you quickly set up and start using the Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP.

The CDP is supported by the E86MON<sup>TM</sup> board-resident debugger. The E86MON boot monitor software enables you to load, run, and debug programs on the CDP. For detailed information on using the E86MON software, refer to the E86MON<sup>TM</sup> Software User's Manual included in your kit.

#### For information on how to:

- Connect the CDP to a PC via a serial port, see page 1-2

- Connect the CDP to a PC via a USB port, see page 1-5

- Connect the development module to the main board, see page 1-5

- Connect the TIP to the main board, see page 1-6

- Connect the ROM-ICE to the main board, see page 1-7

- Invoke the E86MON software, see step 5 on page 1-4

- Troubleshoot installation problems, see page 1-8

- Locate related sources of information, see page 1-9

### Connecting to a PC via a Serial Port

Follow the steps below to connect the Am186CC/CH/CU microcontroller customer development platform to your PC via your PC's serial port.

#### **Installation Requirements**

The items listed below are necessary to install and run the CDP:

- PC with an available COM port

- Terminal emulation software (such as Microsoft® Windows®Terminal or ProComm Plus) that supports ASCII file transfers, software flow control (Xon/Xoff), and send break capability.

- Power source for universal power supply

#### **Main Board Installation**

CAUTION: As with all computer equipment, the Am186CC/CH/CU microcontroller CDP's main board may be damaged by electrostatic discharge (ESD). Please take proper precautions when handling any board.

1. Remove the board from the shipping carton. Visually inspect the board to verify that it was not damaged during shipment.

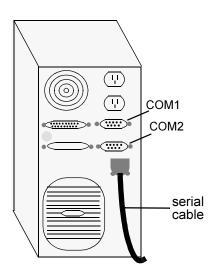

2. Connect either of the CDP main board's DB-9 serial ports to an available COM port. Use the serial cable included in the Am186CC/CH/CU microcontroller CDP kit and note that a DB-9 to DB-25 serial connector adapter is provided if your host system requires it.

3. Connect the power supply to the barrel connector (see P31 at location A-1 in Figure 2-2 on page 2-3) on the CDP's main board.

4. Apply power to the board by connecting the power supply to an electrical outlet. When the board is powered up, the LEDs (see CR12–CR8 at locations C-2–F-2 in Figure 2-2 on page 2-3) should be illuminated.

If all of the LEDs are not illuminated, remove the power supply immediately and contact AMD technical support. See "If You Have Questions, We're Here to Help You." on page iii.

CAUTION: If using your own power supply, ensure that it is a 12-V supply and is capable of providing at least 2 A.

- 5. Invoke the terminal emulation program at 19200 baud, no parity, 8 data bits, and 1 stop bit; enable the software flow control (Xon/Xoff), if supported.

- 6. Reset the board by depressing and releasing the RESET switch (see SW1 at location T-23 in Figure 2-2 on page 2-3).

Type an **a** in the terminal window within three seconds of reset to ensure that the E86MON software uses the correct baud rate. When the E86MON software receives an **a**, it adjusts its baud rate (if necessary) and displays the welcome message and prompt.

**NOTE:** If you type a character other than an **a**, or type no character at all, the E86MON software still displays the welcome message and prompt, but may be using an incorrect baud rate. Depressing and releasing the RESET switch (SW1 at location T-23) gives you another opportunity to type an **a**.

7. To display the version of the monitor and the commands available, type ? and press Enter.

For detailed information about using the E86MON software, refer to the  $E86MON^{\text{TM}}$  Software User's Manual included in your kit.

### Connecting to a PC via a USB port

**NOTE:** USB is *not supported* on the Am186CH HDLC microcontroller.

Follow the steps below to connect the Am186CC/CH/CU microcontroller customer development platform to your PC via your PC's USB port.

- 1. Insert the flat end of your USB cable into the USB port that is connected to your PC.

- 2. Connect the other end of the USB cable into the CDP's main board USB connector (see P18 at location I-1 in Figure 2-2 on page 2-3) that is located on the edge of the board near the power supply (see P31 at location A-1).

To drive the USB, download the USB driver CodeKit software from the AMD website. The CodeKit software package includes installation instructions for the USB host driver and the USB driver on the CDP.

Go to **www.amd.com**, then click on Embedded Processors to get to the Codekit software packages.

# **Connecting the Development Module to the Main Board**

Follow the steps below to connect the router/ISDN development module to the Am186CC/CH/CU microcontroller CDP main board (see Figure 3-3 on page 3-5).

- 1. Orient the main board such that the AMD logo is in the lower right-hand corner, facing you. Orient the development module such that the AMD logo is in the lower leviathan corner, facing you.

- 2. Position the development module above the development module connectors (see P12 and P19 at locations M-22 and F-22, respectively, in Figure 2-2 on page 2-3) on the main board.

- Carefully press the development module down onto the connectors on the main board.

# Connecting a TIP to the Main Board

Follow the steps below to connect the test interface port (TIP) debug board to the Am186CC/CH/CU microcontroller CDP main board:

- 1. Orient the main board such that the AMD logo is in the lower righthand corner, facing you.

- 2. Place the TIP board to the left of the main board with the LCD display toward you.

- 3. Plug the TIP connector into the TIP board with the tab facing toward the left.

- 4. Plug the other end of the connector into the CDP's main board TIP (see P30 at location A-19 in Figure 2-2 on page 2-3) with the tab facing up.

### Connecting a ROM-ICE to the Main Board

Follow the steps below to connect a ROM-ICE to the Am186CC/CH/CU microcontroller customer development platform main board:

- 1. Orient the main board such that the AMD logo is in the lower righthand corner, facing you.

- 2. Set the jumpers according to the configuration shown in Table 1-1 on page 1-7, and jumper your chip select on JP10 (see location F-9 in Figure 2-2 on page 2-3).

- 3. Position the ROM-ICE to the left of the main board.

- 4. Connect the ROM-ICE Low into the left DIP socket (see U28 at location B-12), which is labeled SRAM/ROM LOW.

- 5. Connect the ROM-ICE High into the right DIP socket (see U25 at location D-12), which is labeled SRAM/ROM HIGH.

Table 1-1. ROM-ICE Configuration

| Device           | JP12  |       |       | JP11   |        |       | Vigual Datail                                                                                                 |  |

|------------------|-------|-------|-------|--------|--------|-------|---------------------------------------------------------------------------------------------------------------|--|

|                  | P29LB | P2SEL | P1SEL | P31SEL | P30SEL | Р29НВ | Visual Detail                                                                                                 |  |

| ROM<br>128K x 16 | 11-12 | 5-6   | NC    | NC     | NC     | 1-2   | 00 - 20 SEE                                                                                                   |  |

| ROM<br>512K x 16 | 11-12 | 5-6   | NC    | 11-12  | 5-6    | 1-2   | 0   P29HB<br>0   P39SEL<br>0   P31SEL<br>1   P11<br>1   P12<br>1   P12<br>0   P1SEL<br>0   P1SEL<br>0   P1SEL |  |

### **Troubleshooting Installation Problems**

Table 1-2. Installation Troubleshooting

| Problem                                                                                      | Solution                                                                                                                                                                                                                                                                                                               |  |  |

|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Nothing happens when pushing the RESET button.                                               | Sometimes it is difficult to make a good connection when pushing the small RESET button. If all else fails, remove the power supply from the AC electrical outlet and disconnect and reconnect the power supply. The LEDs will light up when the reset is successful.                                                  |  |  |

| The computer does not respond with the E86MON software prompt.                               | Reset the board by pressing the RESET switch and typing an a immediately after power up. If this does not work, verify the power, check the cables, etc., and verify that the terminal program is configured correctly.                                                                                                |  |  |

| After typing a during reset, the terminal emulation software displays unreadable characters. | Check the baud rate setting for the terminal emulation software. It should be set to 19200. Also check the word length (8), stop bits (1), and parity (N), and turn off any hardware flow control.                                                                                                                     |  |  |

| The terminal emulation program locks up the software or PC.                                  | Check the COM port connection with the target board. Make sure that the same COM port is selected in the terminal emulation software. In some PCs if the correct COM port is not specified, the software will fail to function—it will lock in a continuous loop waiting for an answer from the incorrect serial port. |  |  |

| The power LED does not turn on with power.                                                   | Immediately disconnect the power supply. Ensure that the polarity of the power connector is correct. This is a very serious failure of the hardware. If the power source is connected incorrectly, the board will be permanently damaged.                                                                              |  |  |

| There is a problem you cannot resolve.                                                       | Contact the AMD Corporate Applications technical support services (see page iii for phone numbers and more information).                                                                                                                                                                                               |  |  |

#### For More Information...

If you need more information about:

- Am186CC/CH/CU microcontroller CDP hardware, see Chapter 2 and Chapter 3.

- E86MON software, see the *E86MON*<sup>TM</sup> *Software User's Manual* included in your kit.

- Problems with the platform or the E86MON software, see the customer support information on page iii.

- The Am186CC/CH/CU microcontroller CDP's main board layout, see Chapter 2.

- The Am186CC/CH/CU microcontroller CDP's module layout, see Chapter 3.

- The Am186CC/CH/CU microcontroller CDP's main board schematics, see the schematics document included in your kit.

- The Am186CC/CH/CU microcontroller CDP's module schematics, see the schematics document included in your kit.

- The Am186CC/CH/CU microcontrollers, see the following documents, which are included in your kit:

- Am186<sup>TM</sup>CC Communications Controller Data Sheet

- Am186<sup>TM</sup>CH HDLC Microcontroller Data Sheet

- Am186<sup>TM</sup>CU USB Microcontroller Data Sheet

- Am186<sup>TM</sup>CC/CH/CU Microcontrollers User's Manual

Am186TMCC/CH/CU Microcontroller CDP User's Manual

- Am186<sup>TM</sup>CC/CH/CU Microcontrollers Register Set Manual

### Chapter 2

### **Main Board Functional Description**

The Am186CC/CH/CU microcontroller customer development platform (CDP) consists of two boards: a main board that contains an Am186CC communications controller and interfaces, and the development module, which you can use to develop ISDN and router applications. This chapter describes the main board. The development module is described in Chapter 3, "Development Module Functional Description".

Read the following sections to learn more about the main board:

- "Main Board Layout" on page 2-2

- "Main Board Features" on page 2-8

### **Main Board Layout**

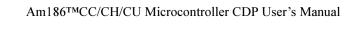

The Am186CC/CH/CU microcontroller customer development platform is easy to configure to fit your design requirements. Figure 2-1 shows the main board block diagram; Figure 2-2 shows the main board layout and component placement; and Table 2-1 lists the jumpers and switches. Note that the schematics referenced are in the separate schematic manual in your board kit.

Figure 2-1. Main Board Block Diagram (Same as Figure 0-1)

Figure 2-2. Main Board Layout

Table 2-1. Jumpers, Switches, and Adjustments

| Part | Function                                           | Description                                                                                                                              | Reference in Figure 2-2 | Schematic<br>Reference<br>Sheet # |

|------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|

| JP1  | HDLC<br>Channel D <sup>1</sup> and<br>clock select | Used to route DCE clocks for HDLC Channel D.                                                                                             | P7                      | Main board<br>Sheet 8             |

| JP2  | HDLC<br>Channel C <sup>1</sup> and<br>clock select | Used to route DCE clocks for HDLC Channel C.                                                                                             | O7                      | Main board<br>Sheet 8             |

| JP3  | UART flow<br>control output<br>select              | Used to provide PIO output for additional RS-232 flow control.                                                                           | O3                      | Main board<br>Sheet 9             |

| JP4  | HDLC<br>Channel B <sup>2</sup> and<br>clock select | Used to route DCE clocks for HDLC Channel B.                                                                                             | N7                      | Main board<br>Sheet 8             |

| JP5  | UART flow<br>control input<br>select               | Used to provide PIO input for additional RS-232 flow control.                                                                            | M3                      | Main board<br>Sheet 9             |

| JP6  | HDLC<br>Channel A <sup>2</sup> and<br>clock select | Used to route DCE clocks for HDLC Channel A.                                                                                             | L7                      | Main board<br>Sheet 8             |

| JP7  | High-Speed<br>UART flow<br>control                 | Provides isolation to High-<br>Speed UART flow control<br>signals or alternate PIOs for flow<br>control.                                 | L3                      | Main board<br>Sheet 9             |

| JP8  | Chip select for Flash memory                       | Used to select $\overline{UCS}$ or $\overline{MCS0}$ for Flash memory.                                                                   | H18                     | Main board<br>Sheet 4             |

| JP9  | Logic analyzer clock select                        | Used as a clock input on the logic analyzer header.                                                                                      | G13                     | Main board<br>Sheet 11            |

| JP10 | SRAM/ROM-<br>ICE device select                     | $\frac{\text{Used to select }\overline{\text{LCS}},\overline{\text{UCSR}},\text{ or }}{\overline{\text{MCS0}}\text{ for SRAM/ROM-ICE}}.$ | F9                      | Main board<br>Sheet 5             |

| JP11 | SRAM/ROM-<br>ICE device select                     | Used to select various SRAM and ROM configurations.                                                                                      | D9                      | Main board<br>Sheet 5             |

Table 2-1. Jumpers, Switches, and Adjustments (Continued)

| Part | Function                                  | Description                                                                                               | Reference in Figure 2-2 | Schematic<br>Reference<br>Sheet # |

|------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|

| JP12 | SRAM/ROM-<br>ICE device select            | Used to select various SRAM and ROM configurations.                                                       | В9                      | Main board<br>Sheet 5             |

| SW1  | Reset switch                              | Used to reset the CDP.                                                                                    | T22                     | Main board<br>Sheet 3             |

| SW3  | HDLC DCE port<br>A multidrop<br>select    | Used to enable multidrop mode for port A. <sup>2</sup>                                                    | Q18                     | Main board<br>Sheet 15            |

| SW4  | PIO isolation select                      | Used to isolate PIOs from other usage on CDP.                                                             | P16                     | Main board<br>Sheet 15            |

| SW5  | HDLC DCE port<br>B multidrop<br>select    | Used to enable multidrop mode for port B. <sup>2</sup>                                                    | P18                     | Main board<br>Sheet 15            |

| SW6  | HDLC DCE port<br>C multidrop<br>select    | Used to enable multidrop mode for port C. <sup>1</sup>                                                    | O18                     | Main board<br>Sheet 15            |

| SW7  | HDLC DCE port<br>D multidrop<br>select    | Used to enable multidrop mode for port D. <sup>1</sup>                                                    | N18                     | Main board<br>Sheet 15            |

| SW8  | HDLC clock<br>configuration<br>select     | Selects HDLC ports A–D frequency options. 1,2                                                             | L6                      | Main board<br>Sheet 8             |

| SW9  | Serial interface<br>transceiver<br>select | Used to disable HDLC port A–D and UART transceivers. (Default: HDLC A–D off and UARTS on.) <sup>1,2</sup> | 18                      | Main board<br>Sheet 3             |

| SW10 | HDLC clock<br>configuration<br>select     | Selects HDLC ports A–D for PCM frame synchronization options. 1,2                                         | J6                      | Main board<br>Sheet 8             |

Table 2-1. Jumpers, Switches, and Adjustments (Continued)

| Part | Function                                       | Description                                                                                  | Reference in Figure 2-2 | Schematic<br>Reference<br>Sheet # |

|------|------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------|-----------------------------------|

| SW11 | Flash memory data bus width select             | Used to determine Flash memory width as 16 or 8 bits. Default: 16 bits.                      | J18                     | Main board<br>Sheet 4             |

| SW12 | HDLC clock<br>configuration<br>select          | Selects HDLC ports A–D for DCE or PCM clocks. <sup>1,2</sup>                                 | 16                      | Main board<br>Sheet 8             |

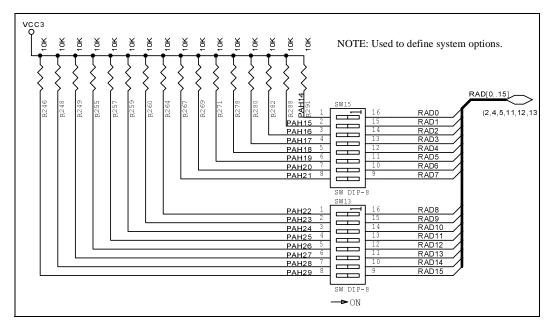

| SW13 | Reset<br>configuration<br>select               | Platform user-specific system configuration.                                                 | D14                     | Main board<br>Sheet 3             |

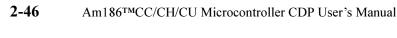

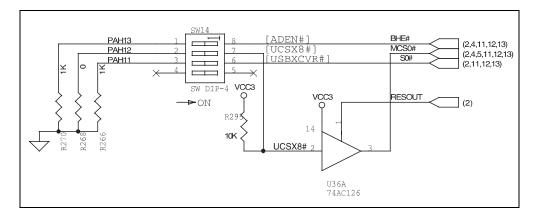

| SW14 | USB clock<br>pinstrap select <sup>3</sup>      | Used to select AD address enable, UCS data width, and external USB <sup>3</sup> transceiver. | C22                     | Main board<br>Sheet 3             |

| SW15 | Reset<br>configuration<br>select               | Platform user-specific system configuration.                                                 | B14                     | Main board<br>Sheet 3             |

| SW16 | CPU and USB <sup>3</sup> clock pinstrap select | Used to select system and USB clock PLL mode pinstrap options.                               | A22                     | Main board<br>Sheet 3             |

| GP1  | Ground                                         | Ground post.                                                                                 | R21                     | Main board<br>Sheet 15            |

| GP2  | Ground                                         | Ground post.                                                                                 | R12                     | Main board<br>Sheet 15            |

| GP3  | Ground                                         | Ground post.                                                                                 | R4                      | Main board<br>Sheet 15            |

| GP4  | Ground                                         | Ground post.                                                                                 | M13                     | Main board<br>Sheet 15            |

| GP5  | Ground                                         | Ground post.                                                                                 | D20                     | Main board<br>Sheet 15            |

| GP6  | Ground                                         | Ground post.                                                                                 | A6                      | Main board<br>Sheet 15            |

Table 2-1. Jumpers, Switches, and Adjustments (Continued)

| Part | Function   | Description                                                 | Reference in Figure 2-2 | Schematic<br>Reference<br>Sheet # |

|------|------------|-------------------------------------------------------------|-------------------------|-----------------------------------|

| TP1  | Test point | Test point for USBD+ from USB connector (P18). <sup>3</sup> | I2                      | Main board<br>Sheet 10            |

| TP2  | Test point | Test point for USBD– from USB connector (P18). <sup>3</sup> | I2                      | Main board<br>Sheet 10            |

| TP3  | Test point | Test point for CLKOUT.                                      | H13                     | Main board<br>Sheet 2             |

- 1. HDLC channels C and D supported on the Am186CC communications controller only.

- 2. HDLC channels A and B supported on the Am186CC and Am186CH microcontrollers only.

- 3. USB is supported on the Am186CC and Am186CU microcontrollers only.

Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

## **Main Board Features**

The main board is a single-sided, 9- x 12-inch, printed circuit board that integrates the Am186CC communications controller, a power supply, memory interfaces, and I/O interfaces onto one board, enabling you to develop specific applications using the development module interface.

The main board contains debug and status features, and enables you to evaluate and develop different configurations of memory and I/O by using on-board configuration switches, jumper blocks, and expansion interfaces.

The following features are described in this section:

- Am186CC/CH/CU microcontroller, page 2-8

- Power supply, page 2-15

- Memory interfaces, page 2-20

- Communications interfaces, page 2-27

- · Debug and configuration circuitry, page 2-39

- Expansion interfaces, page 2-49

## Am186™CC/CH/CU Microcontroller (J14)

The Am186CC/CH/CU microcontroller customer development platform supports a 160-pin PQFP Am186CC communications controller operating at 25, 40, or 50 MHz. The integrated features of the Am186CC communications controller provide a glueless interface to DRAM or SRAM system memory and Flash memory. The microcontroller also integrates UART and High-Speed UART (which require only external transceivers), a high-speed (12 Mbit/s) USB peripheral controller with internal transceiver (Am186CC and Am186CU microcontrollers only), and HDLC channels (Am186CC and Am186CH microcontrollers only) that provide external interfaces to gluelessly connect to communications peripherals.

**NOTE:** Although the CDP supports an Am186CC communications controller, you can also use this platform to evaluate the Am186CH and Am186CU microcontrollers. These microcontrollers support subsets of the Am186CC communications controller's features. Refer to the device data sheets for more information.

Am186TMCC/CH/CU Microcontroller CDP User's Manual

The Am186CC communications controller is designed as a cost-effective, highperformance microcontroller solution for communication applications. The Am186CC communications controller offers the advantages of the x86 development environment's widely available native development tools, applications, and system software. For detailed information about the specific features of the Am186CC/CH/CU microcontroller, refer to the corresponding data sheet and user's manual included in your kit. Figure 2-3 shows the Am186CC communications controller block diagram; Figure 2-4 on page 2-10 shows the Am186CH HDLC microcontroller block diagram; and Figure 2-5 on page 2-10 shows the Am186CU USB microcontroller block diagram.

Figure 2-3. Am186CC™ Communications Controller Block Diagram

Figure 2-4. Am186CH™ HDLC Microcontroller Block Diagram

Figure 2-5. Am186CU™ USB Microcontroller Block Diagram

## **Am186CC™** Communications Controller Power Supply

The CDP main board provides a 3.3-V power supply for the Am186CC communications controller. The power supply is sourced from a 3.3-V low drop out (LDO) regulator (U29) from a 5-V switching power supply. The digital and analog power pins are isolated by filtering to prevent noise on the digital circuitry from affecting the internal analog block.

2-10 Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

## Am186™CC/CH/CU Microcontroller Clocking

Four types of input clocks are used on the main board: the system clock, USB clock (Am186CC and Am186CU microcontrollers only), UART clock, and HDLC clocks (Am186CC and Am186CH microcontrollers only).

The system and USB clocks, shown in Figure 2-6 and Figure 2-7, respectively, use internal oscillators and PLLs that enable the use of slower, less costly, fundamental mode crystals for providing system clock frequencies from 16 to 50 MHz, and a USB frequency of 48 MHz. The UART clock can be derived from the system clock frequency, or from the UCLK input by using an external oscillator. The on-board MACH device can be used for the DCE or PCM HDLC clocks at various frequencies and frame syncs (PCM mode only); or if you are using the development module interface, you can drive the HDLC clocks from a specific DCE, PCM, or GCI peripheral. For the available clock options, see Table 2-2.

Table 2-2. CPU and USB Clock Options

| G                             |           | PLL Mode |            | D. J. D.   |                       |  |

|-------------------------------|-----------|----------|------------|------------|-----------------------|--|

| Clock                         | 1x        | 2x       | 4x         | PLL Bypass | Oscillator            |  |

| System clock                  | 16–40 MHz | 8–25 MHz | 8–12.5 MHz | 0–24 MHz   | 0–40 MHz              |  |

| USB clock <sup>1</sup>        | _         | 24 Mhz   | 12 MHz     | _          | 12, 24 MHz            |  |

| Shared<br>system/USB<br>clock | _         | 24 Mhz   | 12 MHz     | _          | 12, 24 MHz            |  |

| UART clock                    | _         | _        | _          | _          | 0–40 MHz <sup>2</sup> |  |

- 1. The USB clock is supported on the Am186CC and Am186CU microcontrollers only.

- 2. UCLK is limited to the maximum frequency of the system clock.

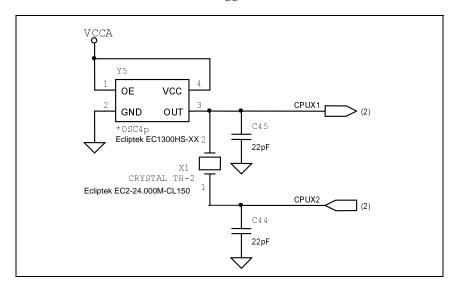

#### System Clock

The system clock, shown in Figure 2-6 on page 2-12 (or sheet 3 of the main board schematics included in your kit), can be derived from a fundamental mode crystal by doing one of the following:

- Driving X1 and X2 at location X1 into the integrated oscillator and using the internal PLL (see locations H16 and J16 in Figure 2-2 on page 2-3)

- Driving X1 and X2 at location X1 into the integrated oscillator and bypassing the internal PLL

The system clock can also be derived from an external oscillator by doing one of the following:

- Driving an external oscillator from Y5 into X1 and using the internal PLL (see location H16 in Figure 2-2 on page 2-3)

- Driving an external oscillator from Y5 into X1 and bypassing the internal PLL

The PLL can be configured in 1x, 2x (default), or 4x PLL mode or PLL bypass mode by appropriately setting the pinstraps on SW16. See "Debug and Configuration Circuitry" on page 2-39 for more information.

The maximum crystal input and oscillator frequencies are 40 MHz. The CDP provides pin sockets, allowing the designer to easily attain multiple clock configurations.

**NOTE:** When using an external oscillator or clock source to drive the system, USB, or UART clock, you must drive the clock with a source that does not exceed the Am186CC/CH/CU microcontroller's  $V_{CC}$ .

Figure 2-6. Am186™CC/CH/CU Microcontroller System Clock

2-12

Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

#### **USB Clock**

- The USB clock (shown in Figure 2-7or sheet 3 of the main board schematics included in your kit), which must be 48 MHz, may be derived from one of the following:

- · System clock

- Driving USBX1 and USBX2 at location X2 into the integrated oscillator and using the internal PLL (see location J16 in Figure 2-2 on page 2-3)

- Driving an external oscillator into USBX1 from Y3 and using the internal PLL

The PLL can be configured in 2x or 4x PLL mode by appropriately setting the pinstraps on SW16. See "Debug and Configuration Circuitry" on page 2-39 for more information.

The Am186CC and Am186CU microcontrollers' USB block requires a 48-MHz clock input. The USB clocking options are 12 MHz in 4x PLL mode, 24 MHz in 2x PLL mode, or a system clock of 48 MHz.

**NOTE:** When using the system clock for USB clocking, USBX1 must be terminated to ground to prevent unwanted oscillation in the unused integrated USB oscillator. To accomplish this, populate C42 with a  $0-\Omega$  resistor.

Figure 2-7. Am186CC or Am186CU Microcontroller USB Clock

Am186™CC/CH/CU Microcontroller CDP User's Manual

The UCLK input at location Y4 (see location J11 in Figure 2-2 on page 2-3) is used to drive the UART or High-Speed UART with a unique clock source that is not derived from the system clock. The CDP provides oscillator pin sockets, enabling the use of standard 3.3-V half-can oscillators.

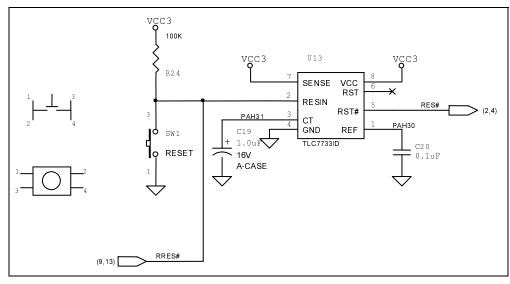

## **Am186CC™** Communications Controller Reset

The Am186CC communications controller requires the  $\overline{RES}$  input to be asserted for at least 1 ms to allow the internal circuitry to stabilize. The CDP main board uses an external device that monitors the 3.3-V  $V_{CC}$  to provide a reset output with an internal 21-ms RC delay to drive the 3.3-V  $\overline{RES}$  input to the Am186CC communications controller. Depressing the reset switch (SW1) causes a system reset without cycling power. Figure 2-8 (or sheet 3 of the main board schematics included in your kit) shows the reset circuitry.

Figure 2-8. Main Board Reset Circuitry

## **Power Supply (A1)**

The CDP is powered by a universal power supply that converts  $100-200 \, V_{AC}$  power to 12  $V_{DC},\,2.5$  A. The 12 V enters the CDP main board through a 5.5-mm barrel connector, where the center post is V<sub>CC</sub> and the outer ring is GND. From the 12-V<sub>DC</sub> input, the CDP on-board power supply provides 5 V, 3.3 V, -5 V, -24 V, and -70 V. The CDP provides power indicators for these voltages at CR8-CR12. The CDP also provides test jacks that enable you to monitor the V<sub>CC</sub> voltages at P22-P25, P28-P29. The following sections provide details about the power supply. Table 2-3 through Table 2-5, beginning on page 2-18, contain power estimates for the CDP main board, development module, and CDP totals.

#### 5 V @ 3 A

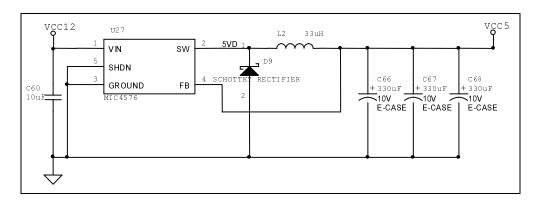

A 5-V buck switching circuit from the 12-V source generates the 5 V, which provides power to a majority of the components on the CDP main board including the DRAM, SRAM, and Flash memory components; the DCE and UART transceivers; the HDLC clock generator; and the 3.3-V LDO regulator. This power supply is also routed to the CDP development module, TIP connector, and Am186 processor expansion interface connectors. For details, see Figure 2-9 or sheet 14 of the main board schematics included in your kit.

Figure 2-9. 5-V Power Supply

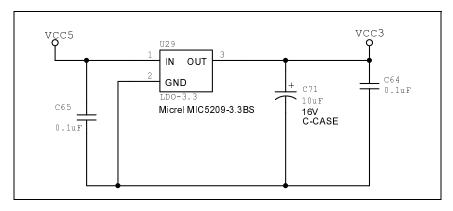

#### 3.3 V @ 500 mA

The 3.3-V LDO regulator at location U29 generates the 3.3 V from the 5-V output. This power supply is used to provide power to the Am186CC communications controller, the USB detect circuitry, and to the optional external USB transceiver. A population option to use the 3.3-V source for the memory components is available. This option is available for the case where no 5-V devices are located on the Am186CC communications controller local bus. For details, see Figure 2-10 or sheet 14 of the main board schematics included in your kit.

Figure 2-10. 3.3-V Power Supply

#### -5 V @ 200 mA

A 5-V buck-boost switching circuit from the 12-V source generates the -5 V. This power supply provides power to the CDP development module and POTS interface. For details, see Figure 2-11 or sheet 14 of the main board schematics included in your kit.

Figure 2-11. -5-V Power Supply

Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

2-16

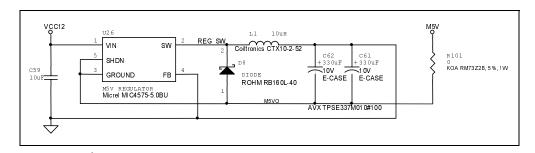

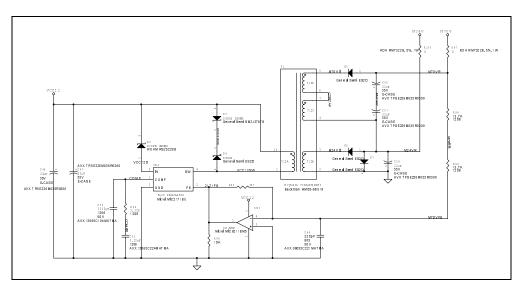

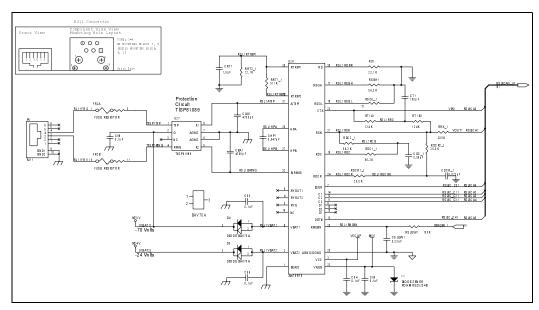

## -24 V @ 50 mA and -70 V @ 60 mA

A switching flyback circuit from the 12-V source generates the -24 V and the -70 V. These outputs are routed to the CDP development module and are used in the POTS interface. For details, see Figure 2-12 or sheet 14 of the main board schematics included in your kit.

Figure 2-12. -24-V and -70-V Power Supplies

Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

Table 2-3. Power Estimates for the CDP Main Board

| Voltage (V) | Device                            | Qty | I <sub>typ</sub> (mA) | I <sub>max</sub> (mA) | P <sub>typ</sub> (mW) | P <sub>max</sub> (mW) |

|-------------|-----------------------------------|-----|-----------------------|-----------------------|-----------------------|-----------------------|

| 3.3         | Am186CC communications controller | 1   | 3001                  | 380                   | 1000                  | 1250                  |

| 3.3         | USB transceiver <sup>2</sup>      | 1   | 10                    | 30                    | 33                    | 99                    |

| 5           | DRAM 256K x 16                    | 2   | 180                   | 180                   | 1800                  | 1800                  |

| 5           | SRAM 128K x 8                     | 2   | 20                    | 35                    | 200                   | 350                   |

| 5           | Flash memory<br>1M x 8/512K x 16  | 1   | 36                    | 60                    | 180                   | 300                   |

| 5           | CLK generator (PLD)               | 1   | 120                   | 200                   | 600                   | 1000                  |

| 5           | UART transceiver                  | 2   | 20                    | 20                    | 200                   | 200                   |

| 5           | DCE driver                        | 2   | 8                     | 20                    | 80                    | 200                   |

| 5           | DCE receiver                      | 4   | 16                    | 23                    | 320                   | 460                   |

| 3.3<br>5    | Main board total                  |     | 310<br>380            | 410<br>572            | 1023<br>1900          | 1353<br>2860          |

- 1. Average operating current at 50 MHz.

- 2. USB is supported on the Am186CC and Am186CU microcontrollers only.

Table 2-4. Power Estimates for the CDP Development Module

| Voltage (V)           | Device                             | Qty | I <sub>typ</sub> (mA)       | I <sub>max</sub> (mA) | P <sub>typ</sub> (mW)        | P <sub>max</sub> (mW)      |

|-----------------------|------------------------------------|-----|-----------------------------|-----------------------|------------------------------|----------------------------|

| 5                     | Ethernet controller                | 1   | 75                          | 75                    | 375                          | 375                        |

| 5                     | ISDN S/T<br>transceiver            | 1   | 31                          | 38                    | 155                          | 190                        |

| 5                     | ISDN U<br>transceiver <sup>1</sup> | 1   | 54                          | 70                    | 270                          | 350                        |

| 5                     | DTMF                               | 2   | 3                           | 7                     | 30                           | 70                         |

| 5<br>-5               | DSLAC                              | 1   | 24<br>10                    | 24<br>10              | 120<br>50                    | 120<br>50                  |

| 5<br>-5<br>-24<br>-70 | RSLIC                              | 2   | 6.5<br>0.70<br>2.70         | 9<br>1.10<br>5        | 65<br>7<br>129.60            | 90<br>11<br>240            |

| 5<br>-5<br>-24<br>-70 | CDP development module total       |     | 203<br>10.7<br>2.70<br>2.70 | 239<br>11.1<br>5<br>5 | 101.5<br>53.5<br>64.8<br>189 | 1195<br>55.5<br>120<br>350 |

$<sup>1. \ \</sup> USB \ is \ supported \ on \ the \ Am186CC \ and \ Am186CU \ microcontrollers \ only.$

Table 2-5. Total Power Estimates for the CDP

| Voltage (V) | I <sub>typ</sub> (ma) | I <sub>max</sub> (ma) | P <sub>typ</sub> (mw) | P <sub>max</sub> (mw) |

|-------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 3.3         | 310                   | 410                   | 1023                  | 1353                  |

| 5           | 583                   | 811                   | 2915                  | 4055                  |

| -5          | 10.7                  | 11.1                  | 53.5                  | 55.5                  |

| -24         | 2.70                  | 5                     | 64.8                  | 120                   |

| -70         | 2.70                  | 5                     | 189                   | 350                   |

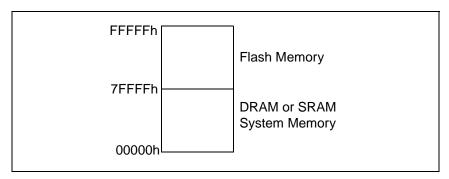

## **Memory Interfaces**

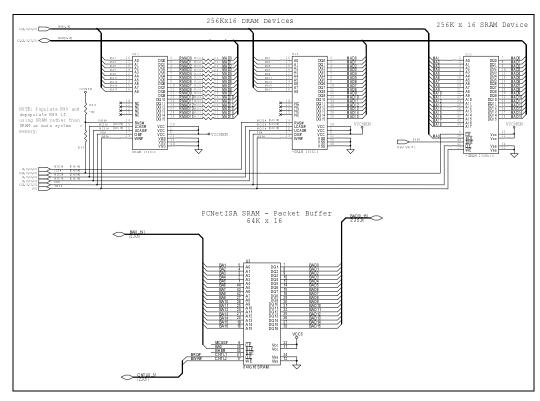

The Am186CC/CH/CU microcontroller customer development platform main board supports DRAM or SRAM system main memory and Flash memory. Figure 2-13 shows the DRAM or SRAM system and Flash memory map, Figure 2-14 on page 2-21 shows the DRAM and SRAM circuitry, and Figure 2-15 on page 2-22 shows the Flash memory circuitry.

Figure 2-13. DRAM or SRAM System Memory and Flash Memory Map

### **Main Memory**

The main board allows the use of two banks of DRAM, or SRAM as the main memory for the system. The default configuration is one bank of 256K x 16 EDO DRAM in an SOJ package, located at U21. See Figure 2-14 on page 2-21 or sheet 4 of the main board schematics included in your kit.

In the default configuration, one bank of 256K x 16 EDO, 40-ns DRAM allows zero wait state operation at up to 50 MHz. The DRAM resides in the lower 512 Kbyte of  $\overline{LCS}$  memory space (0h–7FFFFh). The Am186CC communications controller provides the DRAM memory address on the odd Am186CC communications controller addresses A1–A17 to provide a direct connection to the DRAM device. The DRAM  $\overline{RAS}$  and  $\overline{CAS}$  signaling is provided on the  $\overline{LCSO}/\overline{RASO}$ ,  $\overline{MCS1/CAS1}$ , and  $\overline{MCS2/CASO}$  signals from the Am186CC communications controller when DRAM is selected as the main system memory.

An unpopulated component location, U18, is available for a 256K x 16 device for DRAM bank 1 to be used in the upper 512K of memory space ( $\overline{UCS}$  space). This enables you to boot from Flash memory located in  $\overline{UCS}$  space, and then remap  $\overline{UCS}$  to DRAM bank 1. In this case, the  $\overline{MCS3/RAS1}$  signal becomes the  $\overline{RAS}$  for bank 1 and the  $\overline{CAS}$  signals remain the same.

To use SRAM as main system memory, a 256K x 16 SOJ SRAM can be populated at location U15. R89 must be depopulated, and R90 must be populated with a 10-k $\Omega$  resistor.

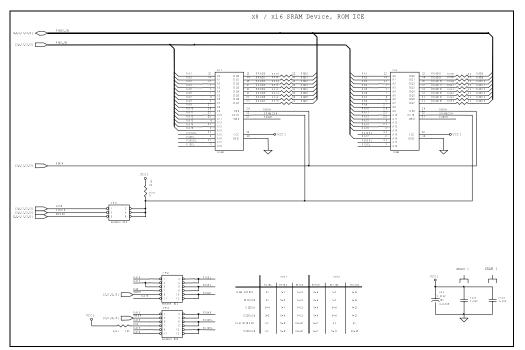

Another option for using SRAM as main system memory is to use two 32-pin DIP sockets at U25 and U28 for SRAM devices. The SRAM is configurable to be used as  $128K \times 8/512K \times 8$ , or  $128K \times 16/512K \times 16$  via configuration jumper blocks JP11 and JP12. A jumper block, JP10, is also used to route either  $\overline{LCS}$ ,  $\overline{UCS}$ , or  $\overline{MCS0}$  to the SRAM sockets.

The CDP main board is populated with 128K x 8, 35-ns DIP SRAM devices as the optional system memory.

**NOTE:** The SRAM sockets are also used for the x16 ROM-ICE interface. Because of this,  $\overline{LCS}$ ,  $\overline{UCS}$ , or  $\overline{MCS0}$  can be used, allowing flexibility of chip selects between the ROM-ICE and on-board Flash memory (see Table 2-6 on page 2-24).

Figure 2-14. Main Memory DRAM Circuit

# •

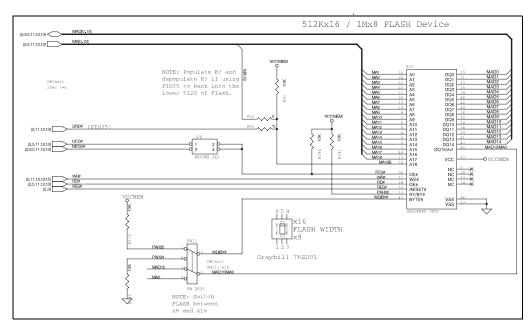

## **Flash Memory**

A single, surface-mount, TSOP Am29F800, 55-ns, 8-Mbit Flash memory device is populated on the CDP main board to allow for zero wait state operation at 50 MHz. See Figure 2-15 or sheet 4 of the main board schematics included in your kit.

You can configure the Flash memory device as 512K x 16 or as a 1-Mbyte x 8 device via configuration switches SW11 and SW14. The default configuration defines the Flash memory as 512 Kbyte (256K x 16) in  $\overline{\text{UCS}}$  space (80000h–FFFFFh). The highest order address bit of the Flash memory can be connected to PIO35 rather than A19 by populating R93 with a 0- $\Omega$  resistor and removing R92. This enables you to bank down to the lower half of the Flash memory to extend available code space to 1 Mbyte. You can also map the Flash memory to  $\overline{\text{MCSO}}$  rather than  $\overline{\text{UCS}}$  via jumper block JP8. For more information about jumper configuration, see page 2-23.

Figure 2-15. Flash Memory Circuit

## **Configuration Overview**

This section describes the options associated with Flash memory and main system memory interfaces.

#### **Flash Memory**

- Flash memory banking select

Populating R92 enables the highest order address bit to the Flash memory to be

routed from A19 (default). Populate R93 to use PIO35 as the Flash memory

banking select. To operate the Flash memory in a banking scheme, PIO35 (which

is normally High) should be configured to be driven Low when accessing the

lower half of the Flash memory.

- JP8: Flash memory chip select

Jumper block JP8 enables you to route UCS (default) or MCS0 as the Flash memory chip select.

- SW11: Flash memory data bus width select

Switch SW11 is used to determine the Flash memory device data width as x8 or x16 (default). When configuring the Flash data width to 8 bits, the pinstrap UCSX8 at SW14 segment 2 must be set to the ON position during reset to configure the Am186CC communications controller to do 8-bit accesses.

#### **SRAM Main Memory**

- JP10: SRAM/ROM-ICE chip select

Jumper block JP10 enables you to route LCS, UCS, or MCS0 to the SRAM

socket's chip select.

- JP11: SRAM/ROM-ICE device select Jumper block JP11 is used along with JP12 to select the different SRAM and ROM configurations.

- JP12: SRAM/ROM-ICE device select

Jumper block JP12 is used along with JP11 to select the different SRAM and

ROM configurations.

Table 2-6 on page 2-24 shows the jumper selections for the various SRAM and ROM options. Figure 2-16 on page 2-25 (or sheet 5 of the main board schematics included in your kit) shows the SRAM sockets. Table 2-7 on page 2-26 lists the SRAM and ROM pinouts.

Table 2-6. DIP x8/x16 SRAM, ROM-ICE Device Selection

| Device          | P29LB | JP12<br>P2SEL | P1SEL | P31SEL | JP11<br>P30SEL | Р29НВ | Visual Detail<br>JP12 JP11              |

|-----------------|-------|---------------|-------|--------|----------------|-------|-----------------------------------------|

| SRAM<br>128Kx8  | 9-10  | 7-8           | NC    | 9-10   | 7-8            | 3-4   |                                         |

| SRAM<br>128Kx16 | 9-10  | 5-6           | NC    | 9-10   | 7-8            | 3-4   | 1<br>0 • 0 • 0 0<br>0 • 0 • 0 0<br>2    |

| SRAM<br>512Kx8  | 9-10  | 7-8           | 3-4   | 9-10   | 5-6            | 3-4   |                                         |

| SRAM<br>512Kx16 | 9-10  | 5-6           | 1-2   | 9-10   | 5-6            | 3-4   |                                         |

| ROM<br>128Kx16  | 11-12 | 5-6           | NC    | NC     | NC             | 1-2   | 000000000000000000000000000000000000000 |

| ROM<br>512Kx16  | 11-12 | 5-6           | NC    | 11-12  | 5-6            | 1-2   |                                         |

Am186<sup>TM</sup>CC/CH/CU Microcontroller CDP User's Manual

2-24

Figure 2-16. DIP SRAM Sockets

2-25

Table 2-7. SRAM and ROM Pinouts

| Pin | SRAM<br>(128K x 8) | SRAM<br>(512K x 8) | ROM<br>(128K x 8) | ROM<br>(256K x 8) | ROM<br>(512K x 8) |

|-----|--------------------|--------------------|-------------------|-------------------|-------------------|

| 1   | NC                 | A18                | VPP               | VPP               | VPP               |

| 2   | A16                | A16                | A16               | A16               | A16               |

| 3   | A14                | A14                | A15               | A15               | A15               |

| 4   | A12                | A12                | A12               | A12               | A12               |

| 5   | A7                 | A7                 | A7                | A7                | A7                |

| 6   | A6                 | A6                 | A6                | A6                | A6                |

| 7   | A5                 | A5                 | A5                | A5                | A5                |

| 8   | A4                 | A4                 | A4                | A4                | A4                |

| 9   | A3                 | A3                 | A3                | A3                | A3                |

| 10  | A2                 | A2                 | A2                | A2                | A2                |

| 11  | A1                 | A1                 | A1                | A1                | A1                |

| 12  | A0                 | A0                 | A0                | A0                | A0                |

| 13  | D0                 | D0                 | D0                | D0                | D0                |

| 14  | D1                 | D1                 | D1                | D1                | D1                |

| 15  | D2                 | D2                 | D2                | D2                | D2                |

| 16  | GND                | GND                | GND               | GND               | GND               |

| 17  | D3                 | D3                 | D3                | D3                | D3                |

| 18  | D4                 | D4                 | D4                | D4                | D4                |

| 19  | D5                 | D5                 | D5                | D5                | D5                |

| 20  | D6                 | D6                 | D6                | D6                | D6                |

| 21  | D7                 | D7                 | D7                | D7                | D7                |

| 22  | CE                 | CE                 | CE                | CE                | CE                |

| 23  | A10                | A10                | A10               | A10               | A10               |

| 24  | OE                 | OE                 | OE                | OE                | OE                |

| 25  | A11                | A11                | A11               | A11               | A11               |

| 26  | A9                 | A9                 | A9                | A9                | A9                |

| 27  | A8                 | A8                 | A8                | A8                | A8                |

| 28  | A13                | A13                | A13               | A13               | A13               |

| 29  | WE                 | WE                 | A14               | A14               | A14               |

| 30  | CS2                | A17                | NC                | A17               | A17               |

| 31  | A15                | A15                | PGM               | PGM               | A18               |

| 32  | VCC                | VCC                | VCC               | VCC               | VCC               |

## **Communication Interfaces**

This section describes the communication interfaces available on the Am186CC/CH/CU microcontroller customer development platform's main board.

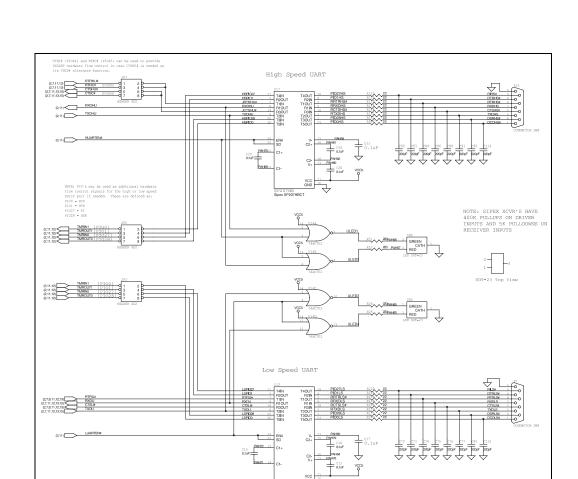

The communication interface I/O ports include two RS-232 DB-9 interfaces for the low- and high-speed serial ports derived from the integrated Am186CC communications controller UARTs, four RS-530 DB-25 DCE/PCM ports derived from the integrated Am186CC or Am186CH microcontroller HDLC interface, and a peripheral USB port derived from the integrated Am186CC or Am186CU microcontroller USB peripheral controller.

**NOTE:** The Am186CH HDLC microcontroller provides only two external HDLC interfaces and does not support USB; the Am186CU USB microcontroller provides a USB interface but does not support HDLC.

#### **RS-232 Serial Ports**

Two RS-232 serial ports (see Figure 2-17 on page 2-29 or sheet 9 of the main board schematics included in your kit) are configured as data communication equipment (DCE) ports to provide direct connection to a typical data terminal equipment (DTE) port on a PC. This enables you to use a straight serial cable (no null-modem) when connecting to a PC. The Am186CC communications controller High-Speed UART is connected to the DB-9 connector at P15 through an RS-232 transceiver and is capable of a data rate of up to 460 Kbit/s. The low-speed UART is connected to the DB-9 connector at P7 through an RS-232 transceiver and is capable of a data rate of up to 120 Kbit/s.