## Am186™CC/CH/CU Microcontrollers

**Register Set Manual**

Order #21916B

| © 1998 Advanced Micro Devices, Inc. All rights reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advanced Micro Devices, Inc. ("AMD") reserves the right to make changes in its products without notice in order to improve design or performance characteristics.                                                                                                                                                                                                                                                                                                                                                                                              |

| The information in this publication is believed to be accurate at the time of publication, but AMD makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication or the information contained herein, and reserves the right to make changes at any time, without notice. AMD disclaims responsibility for any consequences resulting from the use of the information included in this publication.                                                                                                  |

| This publication neither states nor implies any representations or warranties of any kind, including but not limited to, any implied warranty of merchantability or fitness for a particular purpose. AMD products are not authorized for use as critical components in life support devices or systems without AMD's written approval. AMD assumes no liability whatsoever for claims associated with the sale or use (including the use of engineering samples) of AMD products, except as provided in AMD's Terms and Conditions of Sale for such products. |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Trademarks  AMD, the AMD logo, and combinations thereof are trademarks of Advanced Micro Devices, Inc.  Am186, CodeKit, Comm86, E86, and SmartDMA are trademarks of Advanced Micro Devices, Inc.                                                                                                                                                                                                                                                                                                                                                               |

| FusionE86 is a service mark of Advanced Micro Devices, Inc.  Product names used in this publication are for identification purposes and may be trademarks of their respective companies.                                                                                                                                                                                                                                                                                                                                                                       |

## IF YOU HAVE QUESTIONS, WE'RE HERE TO HELP YOU.

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff to answer E86™ and Comm86™ family hardware and software development questions.

Frequently accessed numbers are listed below. Additional contact information is listed on the back of this manual. AMD's WWW site lists the latest phone numbers.

## **Technical Support**

Answers to technical questions are available online, through e-mail, and by telephone.

Go to AMD's home page at **www.amd.com** and follow the **Service** link for the latest AMD technical support phone numbers, software, and Frequently Asked Questions.

For technical support questions on all E86 and Comm86 products, send e-mail to **epd.support@amd.com** (in the US and Canada) or **euro.tech@amd.com** (in Europe and the UK).

You can also call the AMD Corporate Applications Hotline at:

(800) 222-9323 Toll-free for U.S. and Canada

44-(0) 1276-803-299 U.K. and Europe hotline

## **WWW Support**

For specific information on E86 and Comm86 products, access the AMD home page at www.amd.com and follow the Embedded Processors link. These pages provide information on upcoming product releases, overviews of existing products, information on product support and tools, and a list of technical documentation. Support tools include online benchmarking tools and CodeKit™ software—tested source code example applications. Many of the technical documents are available online in PDF form.

Questions, requests, and input concerning AMD's WWW pages can be sent via e-mail to **webmaster@amd.com**.

## **Documentation and Literature Support**

Data books, user's manuals, data sheets, application notes, and product CDs are free with a simple phone call. Internationally, contact your local AMD sales office for product literature.

To order literature, call:

(800) 222-9323 Toll-free for U.S. and Canada

(512) 602-5651 Direct dial worldwide

(512) 602-7639 Fax

## **Third-Party Support**

AMD FusionE86<sup>SM</sup> partners provide an array of products designed to meet critical time-to-market needs. Products and solutions available include emulators, hardware and software debuggers, board-level products, and software development tools, among others. The WWW site and the *E86 Family Products Development Tools CD, order# 21058*, describe these solutions. In addition, mature development tools and applications for the x86 platform are widely available in the general marketplace.

## **TABLE OF CONTENTS**

| CHAPTER 1  | PERIPHERAL CONTROL BLOCK REGISTER OVERVIEW                 | 1-1              |

|------------|------------------------------------------------------------|------------------|

| CHAPTER 2  | HDLC REGISTERS (Am186CC and Am186CH Microcontrollers Only) | 2-               |

| CHAPTER 3  | DMA REGISTERS                                              | 3-               |

| CHAPTER 4  | USB REGISTERS (Am186CC and Am186CU Microcontrollers Only)  | 4-               |

| CHAPTER 5  | ASYNCHRONOUS SERIAL PORT (UART) REGISTERS                  | 5- <sup>-</sup>  |

| CHAPTER 6  | GCI REGISTERS (Am186CC Microcontroller Only)               | 6-               |

| CHAPTER 7  | TSA REGISTERS (Am186CC and Am186CH Microcontrollers Only)  | 7-               |

| CHAPTER 8  | SYNCHRONOUS SERIAL INTERFACE (SSI) REGISTERS               | 8-               |

| CHAPTER 9  | INTERRUPT CONTROLLER REGISTERS                             | 9-               |

| CHAPTER 10 | TIMER REGISTERS                                            | 10-              |

| CHAPTER 11 | CHIP SELECT REGISTERS                                      | 11-              |

| CHAPTER 12 | DRAM CONTROLLER REGISTERS                                  | 12-              |

| CHAPTER 13 | PROGRAMMABLE I/O (PIO) REGISTERS                           | 13-              |

| CHAPTER 14 | RESET CONFIGURATION REGISTER                               | 14-              |

| CHAPTER 15 | WATCHDOG TIMER REGISTER                                    | 15- <sup>-</sup> |

| CHAPTER 16 | MISCELLANEOUS CONFIGURATION REGISTERS                      | 16-              |

| APPENDIX A | REGISTER SUMMARY                                           | <b>A</b> -       |

| INDEX      |                                                            | Index-           |

## **Table of Contents**

## LIST OF FIGURES

| Figure 0-1  | Example Difference Diagram                            |                  |

|-------------|-------------------------------------------------------|------------------|

| Figure 0-2  | Example Difference Diagram for Multichannel Registers |                  |

| Figure 5-1  | Autobaud Enhancement                                  |                  |

| Figure 15-1 | Access to the WDTCON Register                         | 15-2             |

| LIST OF TAE | BLES                                                  |                  |

| Table 0-1   | Documentation Conventions                             | i:               |

| Table 1-1   | Peripheral Control Block Address Map Summary          | 1-2              |

| Table 2-1   | HDLC Register Map                                     |                  |

| Table 3-1   | DMA Register Map                                      |                  |

| Table 4-1   | USB Register Map                                      | 4-'              |

| Table 5-1   | Asynchronous Serial Port Register Map                 | 5-′              |

| Table 5-2   | Baud Rate Table for High-Speed UART                   | 5-19             |

| Table 5-3   | Baud Rate Table for UART (Same as High-Speed UART)    | 5-4              |

| Table 6-1   | GCI Register Map                                      | 6-               |

| Table 7-1   | TSA Register Map                                      | 7-               |

| Table 8-1   | SSI Register Map                                      | 8-′              |

| Table 9-1   | Interrupt Register Map                                | 9-2              |

| Table 9-2   | Interrupt Channel Sources                             | 9-3              |

| Table 9-3   | Interrupt Types                                       | 9-34             |

| Table 9-4   | Interrupt Channel Sources (Same as Table 9-2)         | 9-38             |

| Table 10-1  | Timer Register Map                                    | 10-              |

| Table 11-1  | Chip Select Register Map                              | 11- <sup>-</sup> |

| Table 12-1  | DRAM Controller Register Map                          |                  |

| Table 13-1  | PIO Register Map                                      | 13-              |

| Table 13-2  | PIO Multiplexed Signals                               |                  |

| Table 14-1  | Reset Configuration Register Map                      | 14-              |

| Table 15-1  | Watchdog Timer Register Map                           | 15-              |

| Table 16-1  | Miscellaneous Configuration Register Map              | 16-              |

| Table A-1   | Am186CC/CH/CU Microcontrollers Register Summary       |                  |

## INTRODUCTION

## **Am186™CC MICROCONTROLLER**

The Am186<sup>™</sup>CC communications controller is the first member in the AMD Comm86<sup>™</sup> product family. The Am186CC microcontroller is a cost-effective, high-performance microcontroller solution for communications applications. This highly integrated microcontroller enables customers to save system costs and increase performance over 8-bit microcontrollers and other 16-bit microcontrollers.

The Am186CC microcontroller offers the advantages of the x86 development environment's widely available native development tools, applications, and system software. Additionally, the microcontroller uses the industry-standard 186 instruction set that is part of the AMD E86 family, which continually offers instruction-set-compatible upgrades. Built into the Am186CC microcontroller is a wide range of communications features required in many communications applications, including High-level Data Link Control (HDLC) and the Universal Serial Bus (USB). See Chapter 1, "Peripheral Control Block Register Overview", for a list of included features.

AMD offers complete solutions with the Am186CC microcontroller. A customer development platform board is available. Reference designs that are available or being developed include an Integrated Services Digital Network (ISDN) Terminal Adapter featuring USB, and a low-end router with ISDN, Ethernet, USB, and plain-old telephone service (POTS). AMD and its FusionE86<sup>SM</sup> Partners offer boards, schematics, drivers, protocol stacks, and routing software for these reference designs, enabling fast time to market.

## Am186CH HDLC MICROCONTROLLER

The Am186CH HDLC microcontroller is a cost-reduced derivative of the Am186CC microcontroller that is targeted towards cost-sensitive applications such as linecards and digital phones. The Am186CH HDLC microcontroller is pin-compatible with the Am186CC microcontroller and offers many of the same features, yet the Am186CH HDLC microcontroller provides a cost-effective solution for communications devices that require fewer HDLC channels and do not need GCI or USB.

## **Am186CU USB MICROCONTROLLER**

The Am186CU USB microcontroller is a cost-reduced derivative of the Am186CC microcontroller that is targeted towards cost-sensitive applications such as USB peripherals and digital-subscriber-line (DSL) modems. The Am186CU USB microcontroller is pin-compatible with the Am186CC microcontroller and offers many of the same features, yet the Am186CU USB microcontroller provides a cost-effective solution for USB devices that do not need GCI or HDLC.

#### **PURPOSE OF THIS MANUAL**

This manual includes in reference format the complete set of peripheral control registers required to program the Am186CC/CH/CU microcontrollers. For information about using the internal processor registers, see the *Am186 and Am188 Family Instruction Set Manual*, order #21267.

#### **Intended Audience**

This reference manual is intended primarily for programmers who are developing code for the Am186CC/CH/CU microcontrollers. Computer software and hardware architects and system engineers who are designing or are considering designing systems based on these controllers may also be interested in the information contained in this document. For more information on programming these controllers, see the *Am186CC/CH/CU Microcontrollers User's Manual*, order #21914.

## **Overview of This Manual**

This manual is organized into the following chapters.

- Chapter 1 contains an overview of the microcontroller's **Peripheral Control Block (PCB)** registers.

- Chapter 2 includes descriptions for all of the **High-level Data Link Control (HDLC)** registers (Am186CC and Am186CH microcontrollers only).

- Chapter 3 includes descriptions for the **Direct Memory Access (DMA) registers**.

- Chapter 4 includes descriptions for the **Universal Serial Bus (USB) registers** (Am186CC and Am186CU microcontrollers only).

- Chapter 5 includes descriptions for the **Asynchronous Serial Port (UART) registers**.

- Chapter 6 includes descriptions for the **General Circuit Interface (GCI) registers** (Am186CC microcontroller only).

- Chapter 7 includes descriptions for the **Time Slot Assigner (TSA) registers** (Am186CC and Am186CH microcontrollers only).

- Chapter 8 includes descriptions for the Synchronous Serial Interface (SSI) registers.

- Chapter 9 includes descriptions for the Interrupt Controller registers.

- Chapter 10 includes descriptions for the **Timer registers**.

- Chapter 11 includes descriptions for the **Chip Select registers**.

- Chapter 12 includes descriptions for the **Dynamic Random-Access Memory (DRAM)** registers.

- Chapter 13 includes descriptions for the **Programmable I/O (PIO) registers**.

- Chapter 14 describes the Reset Configuration register.

- Chapter 15 describes the Watchdog Timer register.

- Chapter 16 includes descriptions for the Miscellaneous Configuration registers.

Within each chapter, the registers are listed in ascending hexadecimal order unless descriptions for identical register sets (for example, the HDLC registers) can be combined.

#### RELATED DOCUMENTS

## **AMD Documentation**

The following AMD documents provide additional information about the Am186CC microcontroller.

- The Am186<sup>™</sup>CC Communications Controller Data Sheet, order #21915, the Am186<sup>™</sup>CH HDLC Microcontroller Data Sheet, order #22024, and the Am186<sup>™</sup>CU USB Microcontroller Data Sheet, order #22025, include complete pin lists, pin state tables, timing and thermal characteristics, and package dimensions for the Am186CC/CH/CU microcontrollers.

- The Am186CC/CH/CU Microcontrollers User's Manual, order #21914, provides a functional description of the microcontrollers for both hardware and software designers.

- The Am186 and Am188 Family Instruction Set Manual, order #21267, includes the Am186 microprocessor instruction set used by the Am186CC/CH/CU microcontrollers.

- The E86<sup>™</sup> Family Products and Development Tools CD, order #21058, contains product documentation, utilities, third-party development tools, and evaluation software for AMD microcontrollers and microprocessors.

## **DOCUMENTATION CONVENTIONS**

Table 0-1 lists the documentation conventions used throughout this manual.

## **Table 0-1** Documentation Conventions

| Notation                        | Meaning                                                                                                                                    |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| General                         |                                                                                                                                            |

| bit                             | A single bit in a register.                                                                                                                |

| bit field                       | Two or more consecutive and related bits.                                                                                                  |

| set the EN bit                  | Write a 1 to the EN bit.                                                                                                                   |

| clear the EN bit                | Write a 0 to the EN bit.                                                                                                                   |

| external reset                  | A reset caused by asserting the RES input signal.                                                                                          |

| internal reset                  | A reset initiated by the watchdog timer (see page 15-2).                                                                                   |

| system reset                    | Assertion of the RESOUT signal to reset external peripherals.                                                                              |

| offset 000h                     | A register offset, relative to the base of the current PCB space defined in the Relocation (RELOC) register (see page 16-5).               |

| Register Descriptions           |                                                                                                                                            |

| Software Read/Write             | This row indicates whether software running on the microcontroller can change the value of a field.                                        |

| R in software read/write row    | Software can read this field; for reserved fields, always write the chip reset default value; otherwise, writing this field has no effect. |

| W in software read/write row    | Software can only write this field; when read, the field has no meaning.                                                                   |

| R/W in software read/write row  | Software can read or write this field.                                                                                                     |

| R/W0 in software read/write row | Software can read or clear bits in this field.                                                                                             |

| R/W1 in software read/write row | Software can read or set bits in this field.                                                                                               |

## Table 0-1 Documentation Conventions (Continued)

| Notation                      | Meaning                                                                                                             |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Hardware Set/Clear            | This row indicates whether microcontroller hardware, such as a timer or interrupt, can change the value of a field. |

| — in hardware set/clear row   | Hardware cannot change this field's value after reset.                                                              |

| S in hardware set/clear row   | Hardware can set bits in this field.                                                                                |

| C in hardware set/clear row   | Hardware can clear bits in this field.                                                                              |

| S/C in hardware set/clear row | Hardware can set or clear bits in this field.                                                                       |

| Chip Reset Default            | Value upon an external or internal reset (except in the Watchdog Timer Control (WDTCON) register; see page 15-4).   |

| 0 in default register value   | Cleared on chip reset.                                                                                              |

| 1 in default register value   | Set on chip reset.                                                                                                  |

| x in default register value   | Non-deterministic or floating; no value is guaranteed.                                                              |

| ? in default register value   | Determined by sources external to the microcontroller.                                                              |

| Pin Naming                    |                                                                                                                     |

| {}                            | Pin function during hardware reset (pinstrap).                                                                      |

| []                            | Alternative pin function.                                                                                           |

| MCS3-MCS0                     | All four signals (or registers, or fields).                                                                         |

| MCSx                          | Any of the four signals (or registers, or fields).                                                                  |

| Numbers                       |                                                                                                                     |

| b                             | Binary number.                                                                                                      |

| d                             | Decimal number. Decimal is the default radix.                                                                       |

| h                             | Hexadecimal number.                                                                                                 |

| x in a number                 | Any of several values is legal; for example, 0x01b can be either 0001b or 0101b.                                    |

| [X-Y]                         | The bit field that consists of bits X through Y.                                                                    |

## **Microcontroller-Specific Information**

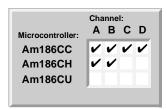

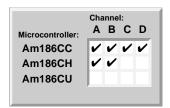

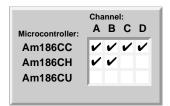

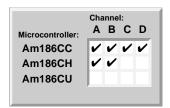

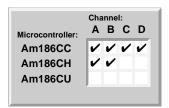

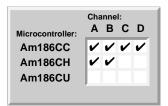

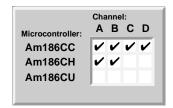

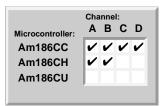

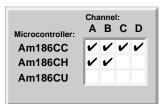

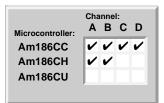

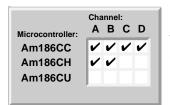

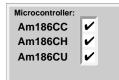

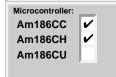

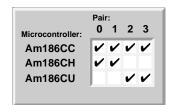

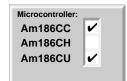

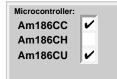

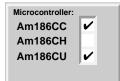

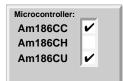

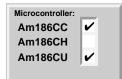

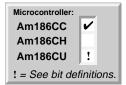

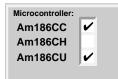

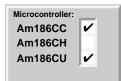

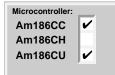

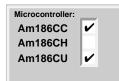

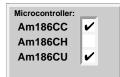

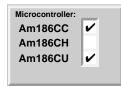

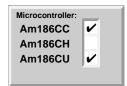

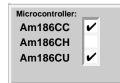

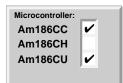

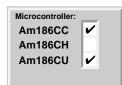

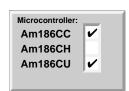

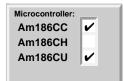

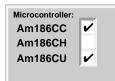

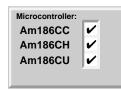

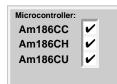

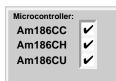

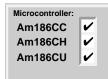

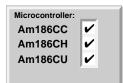

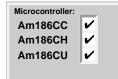

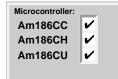

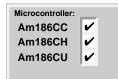

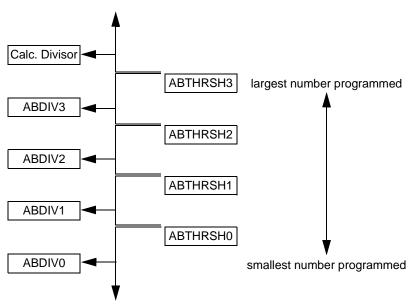

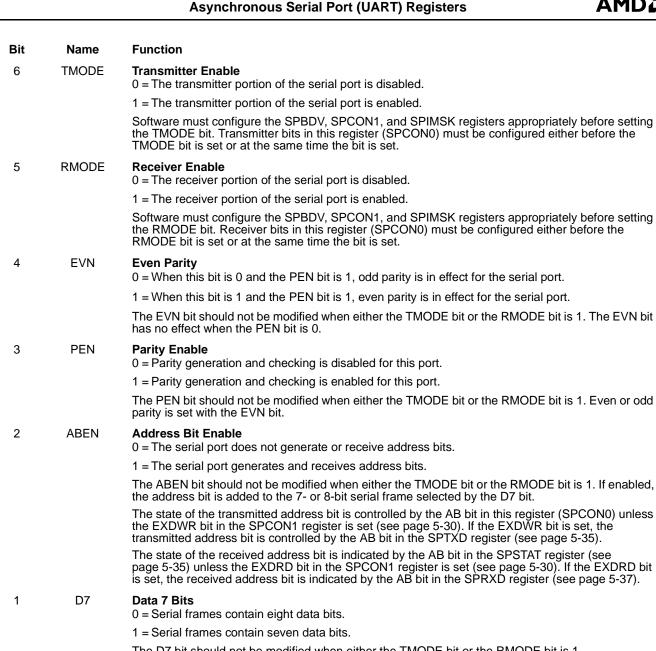

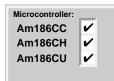

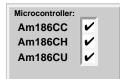

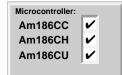

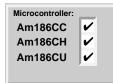

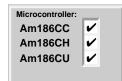

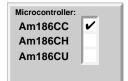

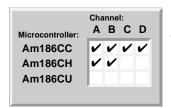

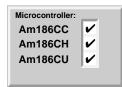

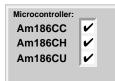

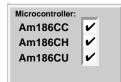

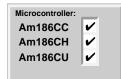

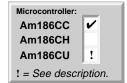

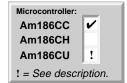

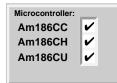

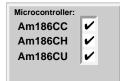

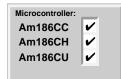

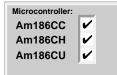

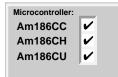

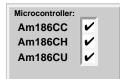

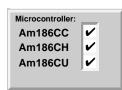

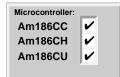

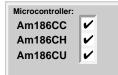

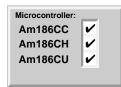

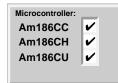

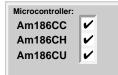

Throughout this manual, information is provided about differences between the Am186CC/CH/CU microcontrollers. A quick summary of differences is provided for each register description in a small diagram as shown in the following example.

Figure 0-1 Example Difference Diagram

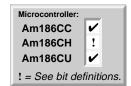

The box next to each microcontroller name indicates the extent to which that microcontroller supports register functions described in the accompanying text. The symbols in the diagram have the following meanings:

- Check mark (✓): the register's functions are fully supported as described.

- **Empty box:** the register described is not supported in this microcontroller.

- Exclamation point (!): if this symbol is present, one or more of the register's bit definitions include microcontroller-specific notes describing any differences that apply. Except for the noted differences, the register's functions are supported as described.

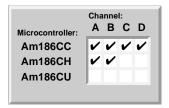

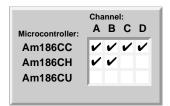

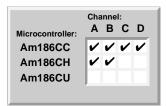

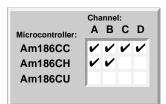

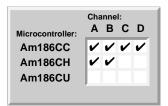

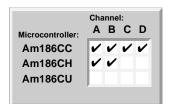

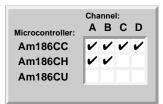

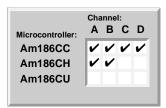

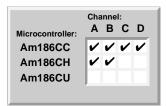

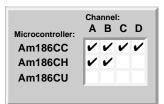

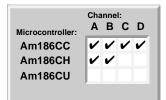

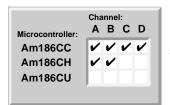

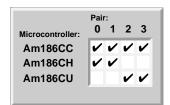

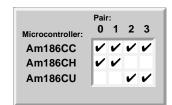

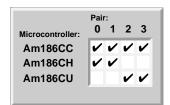

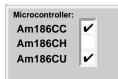

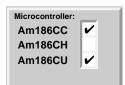

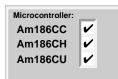

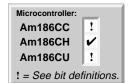

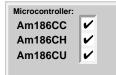

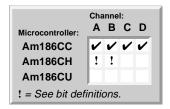

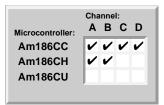

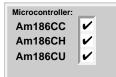

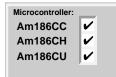

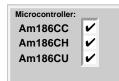

In some chapters, a single register description can apply to several different registers. For example, each register description in Chapter 2, "HDLC Registers (Am186CC and Am186CH Microcontrollers Only)", can apply to as many as four different HDLC channels, depending on the microcontroller. In this situation the difference diagram is expanded, as shown in Figure 0-2, to include information about which channels can be used with each microcontroller.

Figure 0-2 Example Difference Diagram for Multichannel Registers

**Note:** Registers that are not supported on a particular microcontroller must be left in their default states unless otherwise noted in the bit field descriptions. Changing the state of an unsupported register can have unpredictable effects.

CHAPTER

## PERIPHERAL CONTROL BLOCK REGISTER OVERVIEW

The Am186CC/CH/CU microcontrollers' internal peripherals are controlled by 16-bit read/write registers. The peripheral registers are contained within an internal 1-Kbyte control block called the peripheral control block (PCB). Registers are physically located in the peripheral devices they control, but they are addressed as a single 1-Kbyte block.

The configuration registers on the Am186CC microcontroller control the following peripherals:

- Four High-level Data Link Control (HDLC) channels

- Four general-purpose DMA and eight SmartDMA<sup>TM</sup> channels

- Six Universal Serial Bus (USB) endpoints (control, interrupt, and A–D)

- Asynchronous and high-speed asynchronous serial ports

- General Circuit Interface (GCI)

- Four Time Slot Assigners (TSAs)

- Synchronous Serial Interface (SSI)

- 15 interrupt controller channels (36 interrupt sources)

- Three timers

- Four programmable memory and peripheral chip selects, with DRAM control

- 48 programmable input/output pins

- Reset configuration inputs for design-specific jumper and switch settings

- Watchdog timer

**Am186CH Microcontroller:** The Am186CH HDLC microcontroller peripherals are similar to the Am186CC microcontroller, except the Am186CH HDLC microcontroller supports only two HDLC and TSA channels and it has no GCI or USB support. In addition, because it supports fewer internal peripherals, the Am186CH HDLC microcontroller uses only four SmartDMA channels and 32 interrupt sources.

**Am186CU Microcontroller:** The Am186CU USB microcontroller peripherals are similar to the Am186CC microcontroller, except the Am186CU USB microcontroller does not support HDLC, TSA, or GCI. In addition, because it supports fewer internal peripherals, the Am186CU USB microcontroller uses only four SmartDMA channels and 31 interrupt sources.

A System Configuration register is provided to select microcontroller modes of operation, and a read-only Processor Revision Level register provides information about the specific processor level being used.

The peripheral control block can be mapped into either memory or I/O space. The base address of the PCB must be on an even 1024-byte boundary (i.e., the lower ten bits of the base address are all 0b). Internal logic recognizes control block addresses and responds to bus cycles. During bus cycles to internal registers, the bus controller signals the operation

externally (i.e., the  $\overline{RD}$ ,  $\overline{WR}$ , status, address, and data lines are driven as in a normal bus cycle), but the data bus, SRDY, and ARDY are ignored.

On an external or watchdog timer reset, the Relocation (RELOC) register value is set to 20FCh, which maps the PCB to start at FC00h in I/O space. This places the RELOC register at FFFEh. Appendix A provides a summary of PCB registers in offset order, including default address locations. See Chapter 16, "Miscellaneous Configuration Registers" for a complete description of the Relocation register.

Table 1-1 shows peripheral control block ranges that are used for each functional block. Unused addresses within this block are reserved. The entire peripheral control block can be relocated in memory or I/O space by using the Relocation register.

Table 1-1 Peripheral Control Block Address Map Summary

| Function                            | I/O Offset Range       |

|-------------------------------------|------------------------|

| High-level Data Link Control (HDLC) | 000h–0F0h <sup>1</sup> |

| General-Purpose DMA                 | 100h-13Ch              |

| SmartDMA                            | 140h–198h              |

| Universal Serial Bus (USB)          | 1E0h–25Eh <sup>2</sup> |

| High-Speed Asynchronous Serial Port | 260h-27Ch              |

| Asynchronous Serial Port            | 280h-28Eh              |

| General Circuit Interface (GCI)     | 2A0h–2BEh <sup>3</sup> |

| Time Slot Assigner (TSA)            | 2C0h-2DCh <sup>1</sup> |

| Synchronous Serial Interface (SSI)  | 2F0h–2F8h              |

| Interrupt Controller                | 300h-338h              |

| Programmable Timers                 | 340h-354h              |

| Chip Select                         | 3A0h-3A8h              |

| DRAM Refresh                        | 3AAh–3ACh              |

| Programmable I/O (PIO)              | 3C0h-3DCh              |

| Reset Configuration                 | 3DEh                   |

| Watchdog Timer                      | 3E0h                   |

| System Configuration                | 3F0h                   |

| Processor Release Level             | 3F4h                   |

| Relocation                          | 3FEh                   |

#### Notes:

- 1. Reserved in the Am186CU USB microcontroller.

- 2. Reserved in the Am186CH HDLC microcontroller.

- 3. Reserved in the Am186CH and Am186CU microcontrollers.

# 2

## HDLC REGISTERS (Am186CC and Am186CH Microcontrollers Only)

## 2.1 OVERVIEW

This chapter describes the High-level Data Link Control (HDLC) registers on the Am186CC and Am186CH microcontrollers. *The Am186CU USB microcontroller does not support HDLC*.

The Am186CC microcontroller provides four HDLC channels. The Am186CH HDLC microcontroller provides two HDLC channels. The HDLCs are typically used to transmit and receive frames based on the HDLC or Synchronous Data Link Control (SDLC) formats. These formats use flags to determine the start and stop of a frame, and they use "bit stuffing" to maintain data transparency.

In the transmit direction (data leaving the device), the HDLCs add the required error detection bytes (cyclic redundancy check, or CRC) at the end of the frame, bit stuff the data as needed, and surround it with flags.

In the receive direction (data coming into the device), the HDLCs search for flags to determine the start and stop of the frame, remove any bit stuffing, and check the CRC bytes. The HDLCs also check the addresses of incoming frames and reject frames with the wrong address.

First-in-first-out buffers (FIFOs) are used in both directions to isolate data requests from the execution unit. The FIFOs can be filled or emptied using the SmartDMA controller (see Chapter 3, "DMA Registers") or using programmed I/O.

Each of the four HDLCs is used with a Time Slot Assigner (TSA). See Chapter 7, "TSA Registers (Am186CC and Am186CH Microcontrollers Only)".

For more information about using HDLCs and TSAs, see the *Am186CC/CH/CU Microcontrollers User's Manual*, order #21914.

The HDLC register sets are identical for each of the channels. This chapter describes registers with identical functions only once. The unique register names and offsets that apply are listed at the top of each register page. Table 2-1 lists the HDLC registers in offset order, with the corresponding description's page number.

## Table 2-1 HDLC Register Map

| Register Name                            | Mnemonic     | Offset      | Page Number |

|------------------------------------------|--------------|-------------|-------------|

| HDLC Channel A Registers (Am186CC and Am | 186CH HDLC M | icrocontrol | lers Only)  |

| HDLC Channel A Control                   | HACON        | 00h         | page 2-5    |

| HDLC Channel A Transmit Control 0        | HATCON0      | 02h         | page 2-7    |

| HDLC Channel A Transmit Control 1        | HATCON1      | 04h         | page 2-9    |

| HDLC Channel A Receive Control 0         | HARCON0      | 06h         | page 2-11   |

| HDLC Channel A Receive Max Length 1      | HARCON1      | 08h         | page 2-13   |

| HDLC Channel A Status                    | HASTATE      | 0Ah         | page 2-14   |

| HDLC Channel A Interrupt Status 0        | HAISTAT0     | 0Ch         | page 2-16   |

| HDLC Channel A Interrupt Mask 0          | HAIMSK0      | 0Eh         | page 2-18   |

Table 2-1 HDLC Register Map (Continued)

| Register Name                                   | Mnemonic     | Offset      | Page Number |

|-------------------------------------------------|--------------|-------------|-------------|

| HDLC Channel A Interrupt Status 1               | HAISTAT1     | 10h         | page 2-20   |

| HDLC Channel A Interrupt Mask 1                 | HAIMSK1      | 12h         | page 2-22   |

| HDLC Channel A Transmit FIFO Data               | HATD         | 14h         | page 2-24   |

| HDLC Channel A Receive FIFO Data                | HARD         | 16h         | page 2-25   |

| HDLC Channel A Receive FIFO Data Peek           | HARDP        | 18h         | page 2-27   |

| HDLC Channel A Receive Frame Status 1           | HARFS1       | 16h         | page 2-29   |

| HDLC Channel A Receive Frame Status 2           | HARFS2       | 16h         | page 2-31   |

| HDLC Channel A Receive Frame Status 3           | HARFS3       | 16h         | page 2-33   |

| HDLC Channel A Short Frame Counter              | HASFCNT      | 1Ah         | page 2-35   |

| HDLC Channel A Short Frame Counter Peek         | HASFCNTP     | 1Ch         | page 2-36   |

| HDLC Channel A Mismatch Address Counter         | HAMACNT      | 1Eh         | page 2-37   |

| HDLC Channel A Mismatch Address Counter<br>Peek | HAMACNTP     | 20h         | page 2-38   |

| HDLC Channel A Address 0                        | HAA0         | 22h         | page 2-39   |

| HDLC Channel A Address 1                        | HAA1         | 26h         | page 2-39   |

| HDLC Channel A Address 2                        | HAA2         | 2Ah         | page 2-39   |

| HDLC Channel A Address 3                        | HAA3         | 2Eh         | page 2-39   |

| HDLC Channel A Address Mask 0                   | HAA0MSK      | 24h         | page 2-41   |

| HDLC Channel A Address Mask 1                   | HAA1MSK      | 28h         | page 2-41   |

| HDLC Channel A Address Mask 2                   | HAA2MSK      | 2Ch         | page 2-41   |

| HDLC Channel A Address Mask 3                   | HAA3MSK      | 30h         | page 2-41   |

| HDLC Channel B Registers (Am186CC and An        | 186CH HDLC M | icrocontrol | lers Only)  |

| HDLC Channel B Control                          | HBCON        | 40h         | page 2-5    |

| HDLC Channel B Transmit Control 0               | HBTCON0      | 42h         | page 2-7    |

| HDLC Channel B Transmit Control 1               | HBTCON1      | 44h         | page 2-9    |

| HDLC Channel B Receive Control 0                | HBRCON0      | 46h         | page 2-11   |

| HDLC Channel B Receive Max Length 1             | HBRCON1      | 48h         | page 2-13   |

| HDLC Channel B Status                           | HBSTATE      | 4Ah         | page 2-14   |

| HDLC Channel B Interrupt Status 0               | HBISTAT0     | 4Ch         | page 2-16   |

| HDLC Channel B Interrupt Mask 0                 | HBIMSK0      | 4Eh         | page 2-18   |

| HDLC Channel B Interrupt Status 1               | HBISTAT1     | 50h         | page 2-20   |

| HDLC Channel B Interrupt Mask 1                 | HBIMSK1      | 52h         | page 2-22   |

| HDLC Channel B Transmit FIFO Data               | HBTD         | 54h         | page 2-24   |

| HDLC Channel B Receive FIFO Data                | HBRD         | 56h         | page 2-25   |

| HDLC Channel B Receive FIFO Data Peek           | HBRDP        | 58h         | page 2-27   |

| HDLC Channel B Receive Frame Status 1           | HBRFS1       | 56h         | page 2-29   |

| HDLC Channel B Receive Frame Status 2           | HBRFS2       | 56h         | page 2-31   |

| HDLC Channel B Receive Frame Status 3           | HBRFS3       | 56h         | page 2-33   |

| HDLC Channel B Short Frame Counter              | HBSFCNT      | 5Ah         | page 2-35   |

| HDLC Channel B Short Frame Counter Peek         | HBSFCNTP     | 5Ch         | page 2-36   |

| HDLC Channel B Mismatch Address Counter         | HBMACNT      | 5Eh         | page 2-37   |

Table 2-1 HDLC Register Map (Continued)

| Register Name                                   | Mnemonic        | Offset | Page Number |

|-------------------------------------------------|-----------------|--------|-------------|

| HDLC Channel B Mismatch Address Counter<br>Peek | HBMACNTP        | 60h    | page 2-38   |

| HDLC Channel B Address 0                        | HBA0            | 62h    | page 2-39   |

| HDLC Channel B Address 1                        | HBA1            | 66h    | page 2-39   |

| HDLC Channel B Address 2                        | HBA2            | 6Ah    | page 2-39   |

| HDLC Channel B Address 3                        | HBA3            | 6Eh    | page 2-39   |

| HDLC Channel B Address Mask 0                   | HBA0MSK         | 64h    | page 2-41   |

| HDLC Channel B Address Mask 1                   | HBA1MSK         | 68h    | page 2-41   |

| HDLC Channel B Address Mask 2                   | HBA2MSK         | 6Ch    | page 2-41   |

| HDLC Channel B Address Mask 3                   | HBA3MSK         | 70h    | page 2-41   |

| HDLC Channel C Registers (Am186CC Microc        | ontroller Only) |        |             |

| HDLC Channel C Control                          | HCCON           | 80h    | page 2-5    |

| HDLC Channel C Transmit Control 0               | HCTCON0         | 82h    | page 2-7    |

| HDLC Channel C Transmit Control 1               | HCTCON1         | 84h    | page 2-9    |

| HDLC Channel C Receive Control 0                | HCRCON0         | 86h    | page 2-11   |

| HDLC Channel C Receive Max Length 1             | HCRCON1         | 88h    | page 2-13   |

| HDLC Channel C Status                           | HCSTATE         | 8Ah    | page 2-14   |

| HDLC Channel C Interrupt Status 0               | HCISTAT0        | 8Ch    | page 2-16   |

| HDLC Channel C Interrupt Mask 0                 | HCIMSK0         | 8Eh    | page 2-18   |

| HDLC Channel C Interrupt Status 1               | HCISTAT1        | 90h    | page 2-20   |

| HDLC Channel C Interrupt Mask 1                 | HCIMSK1         | 92h    | page 2-22   |

| HDLC Channel C Transmit FIFO Data               | HCTD            | 94h    | page 2-24   |

| HDLC Channel C Receive FIFO Data                | HCRD            | 96h    | page 2-25   |

| HDLC Channel C Receive FIFO Data Peek           | HCRDP           | 98h    | page 2-27   |

| HDLC Channel C Receive Frame Status 1           | HCRFS1          | 96h    | page 2-29   |

| HDLC Channel C Receive Frame Status 2           | HCRFS2          | 96h    | page 2-31   |

| HDLC Channel C Receive Frame Status 3           | HCRFS3          | 96h    | page 2-33   |

| HDLC Channel C Short Frame Counter              | HCSFCNT         | 9Ah    | page 2-35   |

| HDLC Channel C Short Frame Counter Peek         | HCSFCNTP        | 9Ch    | page 2-36   |

| HDLC Channel C Mismatch Address Counter         | HCMACNT         | 9Eh    | page 2-37   |

| HDLC Channel C Mismatch Address Counter<br>Peek | HCMACNTP        | A0h    | page 2-38   |

| HDLC Channel C Address 0                        | HCA0            | A2h    | page 2-39   |

| HDLC Channel C Address 1                        | HCA1            | A6h    | page 2-39   |

| HDLC Channel C Address 2                        | HCA2            | AAh    | page 2-39   |

| HDLC Channel C Address 3                        | HCA3            | AEh    | page 2-39   |

| HDLC Channel C Address Mask 0                   | HCA0MSK         | A4h    | page 2-41   |

| HDLC Channel C Address Mask 1                   | HCA1MSK         | A8h    | page 2-41   |

| HDLC Channel C Address Mask 2                   | HCA2MSK         | ACh    | page 2-41   |

| HDLC Channel C Address Mask 3                   | HCA3MSK         | B0h    | page 2-41   |

## Table 2-1 HDLC Register Map (Continued)

| Register Name                                           | Mnemonic | Offset | Page Number |  |  |

|---------------------------------------------------------|----------|--------|-------------|--|--|

| HDLC Channel D Registers (Am186CC Microcontroller Only) |          |        |             |  |  |

| HDLC Channel D Control                                  | HDCON    | C0h    | page 2-5    |  |  |

| HDLC Channel D Transmit Control 0                       | HDTCON0  | C2h    | page 2-7    |  |  |

| HDLC Channel D Transmit Control 1                       | HDTCON1  | C4h    | page 2-9    |  |  |

| HDLC Channel D Receive Control 0                        | HDRCON0  | C6h    | page 2-11   |  |  |

| HDLC Channel D Receive Max Length 1                     | HDRCON1  | C8h    | page 2-13   |  |  |

| HDLC Channel D Status                                   | HDSTATE  | CAh    | page 2-14   |  |  |

| HDLC Channel D Interrupt Status 0                       | HDISTAT0 | CCh    | page 2-16   |  |  |

| HDLC Channel D Interrupt Mask 0                         | HDIMSK0  | CEh    | page 2-18   |  |  |

| HDLC Channel D Interrupt Status 1                       | HDISTAT1 | D0h    | page 2-20   |  |  |

| HDLC Channel D Interrupt Mask 1                         | HDIMSK1  | D2h    | page 2-22   |  |  |

| HDLC Channel D Transmit FIFO Data                       | HDTD     | D4h    | page 2-24   |  |  |

| HDLC Channel D Receive FIFO Data                        | HDRD     | D6h    | page 2-25   |  |  |

| HDLC Channel D Receive FIFO Data Peek                   | HDRDP    | D8h    | page 2-27   |  |  |

| HDLC Channel D Receive Frame Status 1                   | HDRFS1   | D6h    | page 2-29   |  |  |

| HDLC Channel D Receive Frame Status 2                   | HDRFS2   | D6h    | page 2-31   |  |  |

| HDLC Channel D Receive Frame Status 3                   | HDRFS3   | D6h    | page 2-33   |  |  |

| HDLC Channel D Short Frame Counter                      | HDSFCNT  | DAh    | page 2-35   |  |  |

| HDLC Channel D Short Frame Counter Peek                 | HDSFCNTP | DCh    | page 2-36   |  |  |

| HDLC Channel D Mismatch Address Counter                 | HDMACNT  | DEh    | page 2-37   |  |  |

| HDLC Channel D Mismatch Address Counter<br>Peek         | HDMACNTP | E0h    | page 2-38   |  |  |

| HDLC Channel D Address 0                                | HDA0     | E2h    | page 2-39   |  |  |

| HDLC Channel D Address 1                                | HDA1     | E6h    | page 2-39   |  |  |

| HDLC Channel D Address 2                                | HDA2     | EAh    | page 2-39   |  |  |

| HDLC Channel D Address 3                                | HDA3     | EEh    | page 2-39   |  |  |

| HDLC Channel D Address Mask 0                           | HDA0MSK  | E4h    | page 2-41   |  |  |

| HDLC Channel D Address Mask 1                           | HDA1MSK  | E8h    | page 2-41   |  |  |

| HDLC Channel D Address Mask 2                           | HDA2MSK  | ECh    | page 2-41   |  |  |

| HDLC Channel D Address Mask 3                           | HDA3MSK  | F0h    | page 2-41   |  |  |

HDLC Channel A Control (HACON)

HDLC Channel B Control (HBCON)

HDLC Channel C Control (HCCON)

HDLC Channel D Control (HDCON)

Offset 00h

Offset 40h

Offset 80h

Offset C0h

|                        | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 6   | 5    | 4      | 3     | 2     | 1   | 0    |

|------------------------|----|----|----|----|----|----|---|---|--------|-----|------|--------|-------|-------|-----|------|

| Bit<br>Name            |    |    |    | Re | es |    |   |   | HRESET | Res | NRZI | TRANSM | LOOPR | LOOPL | CRC | ГҮРЕ |

| Software<br>Read/Write |    | R  |    |    |    |    |   |   | R/W    | R   | R/W  | R/W    | R/W   | R/W   | R/  | W    |

| Hardware<br>Set/Clear  | -  |    |    |    |    |    |   |   | _      | _   | _    | _      | _     | _     | _   | _    |

| Chip Reset<br>Default  | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0      | 0   | 0    | 0      | 0     | 0     | 0   | 0    |

## **Register Description**

This register sets operating modes for both the receiver and transmitter.

#### **Bit Definitions**

| Bit  | Name   | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–8 | Res    | Reserved For compatibility with future devices, always write this bit field with its chip reset default value.                                                                                                                                                                                                                                                                                                                                                  |

| 7    | HRESET | HDLC Reset 0 = Allows FIFOs and state machines to operate normally.                                                                                                                                                                                                                                                                                                                                                                                             |

|      |        | 1 = Clears the transmit and receive FIFOs and asynchronously resets the transmitter and receiver state machines.                                                                                                                                                                                                                                                                                                                                                |

|      |        | Setting this bit does not clear the R/W0 interrupt bits in the HxISTAT0 and HxISTAT1 registers, but it does clear the HxSFCNT and HxMACNT registers.                                                                                                                                                                                                                                                                                                            |

|      |        | If the HDLC channel is used on a PCM highway in transparent mode, setting and then clearing this bit causes the HDLC channel to synchronize its byte alignment with the PCM highway. The first byte received or transmitted might be corrupted while the HDLC controller is performing the alignment. To mask this effect on the transmit side, clear the FLAGIDL bit in the HxTCON1 register (see page 2-9), and make the first transmitted byte all 1s (FFh). |

| 6    | Res    | Reserved For compatibility with future devices, always write this bit field with its chip reset default value.                                                                                                                                                                                                                                                                                                                                                  |

| 5    | NRZI   | Non-Return to Zero Invert 0 = Enables NRZ (normal) encoding.                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |        | 1 = Enables NRZI encoding.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4    | TRANSM | Transparent Mode 0 = Normal operation is selected.                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |        | 1 = Transparent mode is selected.                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |        | Transparent mode disables cyclic redundancy check (CRC) generation, flag generation/detection, abort detection, bit stuffing/unstuffing, and CTS lost abort generation. Before using Transparent mode, clear all of the channel's Address Mask (HAMSK) bit fields (see page 2-41) and its Flag Idle (FLAGIDL) bit (see page 2-9).                                                                                                                               |

|      |        | Do not change the TRANSM bit unless both the Transmitter Stop bit (see TSTOP on page 2-16)                                                                                                                                                                                                                                                                                                                                                                      |

and Receiver Stop bit (see RSTOP on page 2-12) are 1.

| Bit | Name    | Function                                                                                                                                                                                                                                                                                                                                                                |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | LOOPR   | Loop Remote 0 = Transmitter controls the transmitter output and uses the transmit clock (TCLK) signal.                                                                                                                                                                                                                                                                  |

|     |         | 1 = Receiver input is fed directly to the transmitter output. Both the transmit clock (TCLK) and the<br>receive clock (RCLK) signals are required. Do not change the LOOPR bit unless the TSTOP bit<br>is 1 (see page 2-16).                                                                                                                                            |

| 2   | LOOPL   | Loop Local 0 = Receiver input comes from the Time Slot Assigner (TSA) and the receive clock (RCLK) signal is used.                                                                                                                                                                                                                                                      |

|     |         | 1 = Transmitter output is fed directly to the receiver input. Only the transmit clock (TCLK) signal is used. The LOOPL bit should not be changed unless the RSTOP bit is 1 (see page 2-12).                                                                                                                                                                             |

| 1–0 | CRCTYPE | CRC Type The CRCTYPE bit selects the algorithm of CRC generation/checking. $00 = \text{CRC-CCITT (16 bit) } (x^{16} + x^{12} + x^5 + 1)$ $01 = \text{CRC-16 (16 bit) } (x^{16} + x^{15} + x^2 + 1)$ $10 = \text{CRC-32 (32 bit) } (x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1)$ $11 = \text{Reserved}$ |

HDLC Channel A Transmit Control 0 (HATCONO)

HDLC Channel B Transmit Control 0 (HBTCONO)

HDLC Channel C Transmit Control 0 (HCTCONO)

HDLC Channel D Transmit Control 0 (HDTCONO)

Offset 02h

Offset 42h

Offset 82h

Offset C2h

|                        | 15 | 14 | 13 | 12  | 11    | 10  | 9 | 8   | 7       | 6      | 5    | 4       | 3      | 2      | 1     | 0 |

|------------------------|----|----|----|-----|-------|-----|---|-----|---------|--------|------|---------|--------|--------|-------|---|

| Bit<br>Name            |    |    |    | TTH | RSH   | Res |   |     | TFIFOEN | FORABR | HTEN | IMSTART | CRCDIS | LBREAD | LBNOW |   |

| Software<br>Read/Write | R  |    |    |     | R/W R |     |   | R/W | R/W     | R/W    | R/W  | R/W     | R/W    | W      |       |   |

| Hardware<br>Set/Clear  | _  |    |    |     | -     | _   | _ |     |         | _      | _    | _       | _      | _      | _     | _ |

| Chip Reset<br>Default  | 0  | 0  | 0  | 0   | 0     | 0   | 0 | 0   | 0       | 0      | 0    | 0       | 0      | 0      | 0     | 0 |

## **Register Description**

This register sets operating modes for the transmitter.

#### **Bit Definitions**

| BIT Defi | Initions |                                                                                                                                                                                                                                                                                                                                                        |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit      | Name     | Function                                                                                                                                                                                                                                                                                                                                               |

| 15–12    | Res      | Reserved For compatibility with future devices, always write this bit field with its chip reset default value.                                                                                                                                                                                                                                         |

| 11–10    | TTHRSH   | Transmit Threshold The TTHRSH bit is used to program the amount of free space desired in the transmit FIFO before generating an interrupt. This same size is used to determine when to request a DMA access. When TTHRSH is set to 16 bytes, the IMSTART bit must be set to 1 to ensure proper operation of the transmitter.  00 = 1 byte 01 = 9 bytes |

|          |          | 10 = 16 bytes                                                                                                                                                                                                                                                                                                                                          |

|          |          | 11 = Reserved                                                                                                                                                                                                                                                                                                                                          |

| 9–7      | Res      | Reserved For compatibility with future devices, always write this bit field with its chip reset default value.                                                                                                                                                                                                                                         |

| 6        | TFIFOEN  | Transmit FIFO Enable 0 = Flushes the transmit FIFO of data; no requests are performed. The TFIFOEN bit should only be cleared when the TSTOP bit is 1 (see page 2-17).                                                                                                                                                                                 |

|          |          | 1 = Enables the transmit FIFO; the FIFO can request data.                                                                                                                                                                                                                                                                                              |

| 5        | FORABR   | Force Abort 0 = The transmitter operates normally.                                                                                                                                                                                                                                                                                                     |

|          |          | 1 = The transmitter sends abort sequences instead of data; the FIFO is flushed. The FORABR bit<br>must be cleared before the transmitter will resume operation.                                                                                                                                                                                        |

|          |          |                                                                                                                                                                                                                                                                                                                                                        |

If the FORABR bit is set and then immediately cleared, one abort sequence is transmitted. If the FORABR bit is set during the closing flag, the flag completes before the abort is sent. If the MLTDRP bit is 1 or the GCIDEN bit is 1 (see page 2-10), only one abort is sent and then the transmitter stops even if the FORABR bit is still 1.

An abort sequence is seven to fourteen 1s.

| Bit | Name    | Function                                                                                                                                               |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4   | HTEN    | Transmit Enable 0 = Disables transmission at the end of the current frame.                                                                             |

|     |         | 1 = Enables transmission, which begins when the channel's clear-to-send (CTS) signal is asserted and sufficient data is in the transmit FIFO.          |

| 3   | IMSTART | Immediate Start                                                                                                                                        |

|     |         | 0 = The transmitter waits to start transmission until the FIFO is half full or the end of the frame is<br>placed in the FIFO.                          |

|     |         | 1 = Immediate start. The transmitter begins transmitting as soon as data is in the transmit FIFO.                                                      |

|     |         | When the TTHRSH bit is programmed to 16 bytes (TTHRSH = 10b), the IMSTART bit must be set to 1 to ensure proper operation of the transmitter.          |

| 2   | CRCDIS  | CRC Disable                                                                                                                                            |

|     |         | 0 = The CRC is appended to the end of the frame. The receiver on the other end can interpret the last few bytes of the frame as the CRC.               |

|     |         | 1 = CRC generation is disabled. The CRC is not appended to the end of the frame.                                                                       |

|     |         | The CRCDIS bit should only be changed while the CRC is not being transmitted.                                                                          |

| 1   | LBREAD  | Last Byte Read                                                                                                                                         |

|     |         | 0 = Reading the transmit FIFO has no effect on frame transmission.                                                                                     |

|     |         | 1 = Software can indicate the last byte for a frame by reading the transmit FIFO immediately after<br>writing the last byte to the transmit FIFO.      |

| 0   | LBNOW   | Last Byte Now 0 = When read, the LBNOW bit is always zero.                                                                                             |

|     |         | 1 = When written with a 1 by software, the LBNOW bit indicates to the transmitter that the last byte for a frame has been placed in the transmit FIFO. |

| HDLC Channel A Transmit Control 1 (HATCON1) | Offset 04h |

|---------------------------------------------|------------|

| HDLC Channel B Transmit Control 1 (HBTCON1) | Offset 44h |

| HDLC Channel C Transmit Control 1 (HCTCON1) | Offset 84h |

| HDLC Channel D Transmit Control 1 (HDTCON1) | Offset C4h |

|                        | 15 | 14 | 13 | 12 | 11      | 10     | 9       | 8     | 7      | 6      | 5           | 4 | 3   | 2   | 1 | 0 |

|------------------------|----|----|----|----|---------|--------|---------|-------|--------|--------|-------------|---|-----|-----|---|---|

| Bit<br>Name            |    |    |    |    | FLAGIDL | MLTDRP | AUTOCTS | TMSBF | TXCINV | GCIDEN | ODRV TDELAY |   |     | LAY |   |   |

| Software<br>Read/Write | R  |    |    |    | R/W     | R/W    | R/W     | R/W   | R/W    | R/W    | R/          | W | R/W |     |   |   |

| Hardware<br>Set/Clear  | _  |    |    |    | _       | _      | _       | _     | _      | _      |             |   |     |     |   |   |

| Chip Reset<br>Default  | 0  | 0  | 0  | 0  | 0       | 0      | 0       | 0     | 0      | 0      | 0           | 0 | 0   | 0   | 0 | 0 |

## **Register Description**

This register sets operating modes for the transmitter.

## **Bit Definitions**

| Bit   | Name    | Function                                                                                                                                                                                                                                                                        |

|-------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–12 | Res     | Reserved For compatibility with future devices, always write this bit field with its chip reset default value.                                                                                                                                                                  |

| 11    | FLAGIDL | Flag Idle 0 = Mark idle. Mark sequences are transmitted in the idle state. A mark sequence is fifteen or more 1s.                                                                                                                                                               |

|       |         | 1 = Flag idle. Flag sequences are transmitted in the idle state. A flag sequence is one 0, then six 1s, then one 0.                                                                                                                                                             |

|       |         | The FLAGIDL bit should only be changed when the TSTOP bit is 1 (see page 2-17).                                                                                                                                                                                                 |

| 10    | MLTDRP  | Multidrop 0 = The multidrop bus mode is not enabled.                                                                                                                                                                                                                            |

|       |         | 1 = The multidrop bus mode is enabled. When the MLTDRP bit is 1, the AUTOCTS, FLAGIDL, and GCIDEN bits must be 0 and the output drive must be open drain (ODRV = 10b). TDELAY should be set for 8, 9, 10, or 11.                                                                |

| 9     | AUTOCTS | Automatic CTS 0 = CTS is ignored.                                                                                                                                                                                                                                               |

|       |         | 1 = CTS is used to automatically enable and disable transmission.                                                                                                                                                                                                               |

| 8     | TMSBF   | Transmit MSB First 0 = Transmit data least-significant bit (LSB) first.                                                                                                                                                                                                         |

|       |         | 1 = Transmit data most-significant bit (MSB) first.                                                                                                                                                                                                                             |

|       |         | HDLC normally is LSB first. Data could be corrupted if the TMSBF bit is changed when the TSTOP bit is 0 (see page 2-17).                                                                                                                                                        |

| 7     | TXCINV  | Transmit Clock Invert 0 = The transmit clock is not inverted.                                                                                                                                                                                                                   |

|       |         | 1 = The transmit clock is inverted.                                                                                                                                                                                                                                             |

|       |         | The TXCINV bit should only be changed when the TSTOP bit is 1 (see page 2-17). Inversion of the transmit clock (TCLK) signal is only recommended for Data Communications Equipment (DCE) operation and does not operate properly with time-division-multiplexed configurations. |

| Bit | Name   | Function                                                                                                                                                                                                                                                                                                                                                           |

|-----|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6   | GCIDEN | GCI D Channel Enable 0 = The HDLC channel's transmission is independent of control of the GCI D-channel.                                                                                                                                                                                                                                                           |

|     |        | 1 = Transmission will not begin until the GCI interface has control of the D-channel. Only one HDLC channel at a time should have the GCIDEN bit set. When the GCIDEN bit is 1, the time slot assigner must be programmed for this HDLC to use the D-channel time slot. When the GCIDEN bit is 1, the FLAGIDL bit should be 0.                                     |

|     |        | The GCIDEN bit should only be changed when the TSTOP bit is 1 (see page 2-17).                                                                                                                                                                                                                                                                                     |

| 5–4 | ODRV   | Output Drive The ODRV bit controls the state of the transmit data output. The ODRV bit has no effect when in Pulse Code Modulation (PCM) Highway or GCI mode.                                                                                                                                                                                                      |

|     |        | 00 = Three state                                                                                                                                                                                                                                                                                                                                                   |

|     |        | 01 = Totem pole (normal drive)                                                                                                                                                                                                                                                                                                                                     |

|     |        | 10 = Open drain                                                                                                                                                                                                                                                                                                                                                    |

|     |        | 11 = Reserved                                                                                                                                                                                                                                                                                                                                                      |

| 3–0 | TDELAY | Transmit Delay The TDELAY bit field controls the number of 1s to wait before transmitting in multidrop mode. The TDELAY bit field must be 0000 if the MLTDRP bit is 0. The TDELAY bit should only be changed when the TSTOP bit is 1 (see page 2-17).  0000 = Do not wait.  0001 = Wait for one 1.  0010 = Wait for two 1s. and so on  1111 = Wait for fifteen 1s. |

HDLC Channel A Receive Control 0 (HARCON0)

HDLC Channel B Receive Control 0 (HBRCON0)