# 29K<sup>™</sup> Family Simulators Reference Manual

#### 29K<sup>™</sup> Family Simulators Reference Manual, Release 3.3

© 1995 by Advanced Micro Devices, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Advanced Micro Devices, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause at 252.227–7013. Advanced Micro Devices, Inc., 5204 E. Ben White Blvd., Austin, TX 78741–7399.

Am29000 and AMD are registered trademarks, and 29K, Am29005, Am29030, Am29035, Am29040, Am29050, Am29200, Am29205, Am29240, Am29243, Am29245, MiniMON29K, and XRAY29K are trademarks of Advanced Micro Devices, Inc. High C is a registered trademark of MetaWare, Inc.

Other product or brand names are used solely for identification and may be the trademarks or registered trademarks of their respective companies.

The text pages of this document have been printed on recycled paper consisting of 50% recycled fiber and 50% virgin fiber; the post-consumer waste content is 10%. These pages are recyclable.

Advanced Micro Devices, Inc. 5204 E. Ben White Blvd. Austin, TX 78741–7399

#

# Contents

### About the 29K Family Simulators

| Product Documentation        | vi  |

|------------------------------|-----|

| About This Manual            | vi  |

| Suggested Reference Material | vii |

| Standards and Conventions    | ix  |

| Standards                    | ix  |

| Conventions                  | X   |

### Chapter 1

### **Using the Simulators**

| Using the 29K Family Simulators | 1-3 |

|---------------------------------|-----|

| isstip                          | 1-3 |

| sim29                           | 1-4 |

| Invoking isstip                 | 1-5 |

| Invoking sim29                  | 1-9 |

### Chapter 2

### **ISSTIP Example**

| Example Tutorial For MS-DOS Hosts | 2-2 |

|-----------------------------------|-----|

| Example Tutorial For UNIX Hosts   | 2-5 |

### 29K Family Three-Bus Processor Architecture Simulation

#### Chapter 4

# 29K Family Two-Bus Processor Architecture Simulation

| Simulator Command-Line Syntax | 4-2 |

|-------------------------------|-----|

| The Event File                | 4-4 |

Chapter 5

| 29K Family Microcontroller Architecture Simul                                            | ation |  |  |

|------------------------------------------------------------------------------------------|-------|--|--|

| Simulator Command-Line Syntax                                                            |       |  |  |

| The Event File                                                                           |       |  |  |

| Chapter 6                                                                                |       |  |  |

| SIM29 OS Interface                                                                       |       |  |  |

| Register Initialization                                                                  |       |  |  |

| Trap Interface                                                                           |       |  |  |

| Appendix A                                                                               |       |  |  |

| Error Messages                                                                           |       |  |  |

| Error Messages                                                                           | A-2   |  |  |

| Register Initialization         Trap Interface         Appendix A         Error Messages |       |  |  |

### Index

# **Figures and Tables**

# Figures

| Figure 3-1. | Simple Access in Three-Bus Microprocessors                                    | 3-29 |

|-------------|-------------------------------------------------------------------------------|------|

| Figure 3-2. | Burst Access in Three-Bus Microprocessors                                     | 3-30 |

| Figure 3-3. | Pipelined Access in Three-Bus Microprocessors                                 | 3-30 |

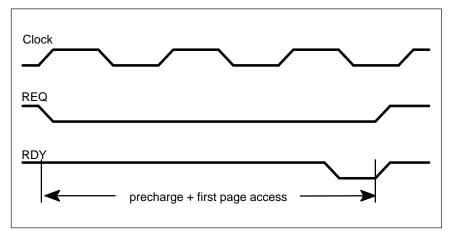

| Figure 3-4. | First Access on Page Crossing in Paged Memory<br>in Three-Bus Microprocessors | 3-31 |

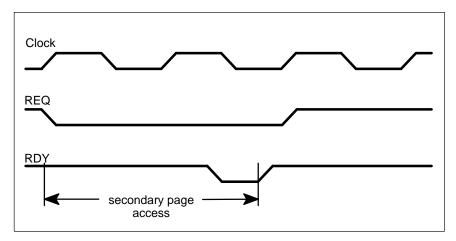

| Figure 3-5. | Secondary Access Within the Page in Three-Bus<br>Microprocessors              | 3-31 |

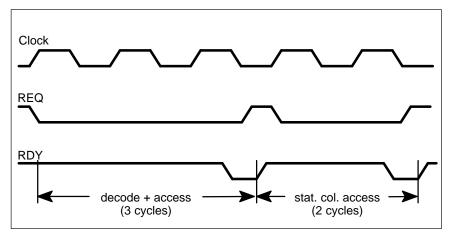

| Figure 3-6. | Static Column Access in Three-Bus Microprocessors                             | 3-32 |

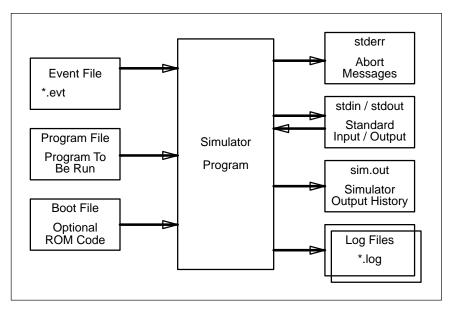

| Figure 3-7. | Simulator I/O                                                                 | 3-35 |

### Tables

| xi   | Notational Conventions                                                               | Table 0-1. |

|------|--------------------------------------------------------------------------------------|------------|

|      | CFG Register Default Settings for the Three-Bus<br>Microprocessor Simulators         | Table 3-1. |

| 3-7  | CPS Register Default Settings for the Three-Bus<br>Microprocessor Simulators         | Table 3-2. |

| 3-13 | Three-Bus Microprocessor Simulator Events                                            | Table 3-3. |

| 3-25 | IRAM Memory Model Access Codes and Values for<br>Three-Bus Microprocessor Simulation | Table 3-4. |

| 3-26 | IROM Memory Model Access Codes and Values for<br>Three-Bus Microprocessor Simulation | Table 3-5. |

| 3-27 | DRAM Memory Model Access Codes and Values for<br>Three-Bus Microprocessor Simulation | Table 3-6. |

| 3-36 | Simulator Input/Output File Assignments                                              | Table 3-7. |

| 6-2  | General-Purpose Register Initialization                                              | Table 6-1. |

# **About the 29K Family Simulators**

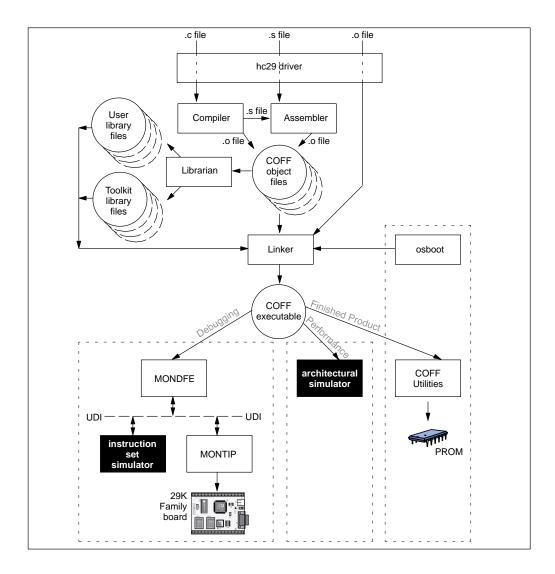

The AMD<sup>®</sup> 29K<sup>m</sup> Family simulators, **isstip** and **sim29**, enable the user to execute 29K Family processor programs on a host system, without any 29K Family processor hardware. The following pages list and describe each chapter in this product manual, and then discuss the standards and conventions.

# **Product Documentation**

This documentation is written for the experienced program developer, who is assumed to have a working knowledge of the C language and the specific 29K Family microprocessor or microcontroller being used. For further information on a particular 29K Family microprocessor or microcontroller, see the appropriate user's manual.

### **About This Manual**

Chapter 1: "Using the Simulators" describes the syntax for invoking the instruction set simulator **isstip** and the architectural simulator **sim29**.

Chapter 2: "ISSTIP Example" provides examples of using the 29K Family instruction set simulator, **isstip**, with the MiniMON29K<sup>m</sup> user interface, **mondfe**.

Chapter 3: "29K Family Three-Bus Processor Architecture Simulation" describes how to use **sim29** to simulate the Am29000<sup>®</sup>, Am29005<sup>™</sup>, and Am29050<sup>™</sup> microprocessors.

Chapter 4: "29K Family Two-Bus Processor Architecture Simulation" describes how to use **sim29** to simulate the Am29030<sup>™</sup>, Am29035<sup>™</sup>, and Am29040<sup>™</sup> microprocessors.

Chapter 5: "29K Family Microcontroller Architecture Simulation" describes how to use **sim29** to simulate the Am29200<sup>™</sup>, Am29205<sup>™</sup>, Am29240<sup>™</sup>, Am29243<sup>™</sup>, and Am29245<sup>™</sup> microcontrollers.

Chapter 6: "SIM29 OS Interface" discusses the simulator's general interface to the **osboot** and trap code.

Appendix A: "Error Messages" lists and explains the simulator error messages.

### **Suggested Reference Material**

The following additional reference documents may be of interest to the user:

- Am29000<sup>®</sup> and Am29005<sup>™</sup> User's Manual and Data Sheet Advanced Micro Devices, order number 16914.

- Am29030<sup>™</sup> and Am29035<sup>™</sup> Microprocessors User's Manual and Data Sheet Advanced Micro Devices, order number 15723.

- Am29040<sup>™</sup> Microprocessor Data Sheet Advanced Micro Devices, order number 18459.

- Am29040<sup>™</sup> Microprocessor User's Manual Advanced Micro Devices, order number 18458.

- Am29050<sup>™</sup> Microprocessor Data Sheet Advanced Micro Devices, order number 15039.

- Am29050<sup>™</sup> Microprocessor User's Manual Advanced Micro Devices, order number 14778.

- Am29200<sup>™</sup> and Am29205<sup>™</sup> RISC Microcontrollers Data Sheet Advanced Micro Devices, order number 16361.

- Am29200<sup>™</sup> and Am29205<sup>™</sup> RISC Microcontrollers User's Manual Advanced Micro Devices, order number 16362.

- Am29240<sup>™</sup>, Am29245<sup>™</sup>, and Am29243<sup>™</sup> RISC Microcontrollers Data Sheet Advanced Micro Devices, order number 17787.

- Am29240<sup>™</sup>, Am29245<sup>™</sup>, and Am29243<sup>™</sup> RISC Microcontrollers User's Manual Advanced Micro Devices, order number 17741.

- Harbison, Samuel P. and Guy L. Steele, Jr.: *C: A Reference Manual, Second Edition*, Prentice-Hall, Inc., Englewood Cliffs, NJ 07632, 1987.

- *Host Interface (HIF) Specification* Advanced Micro Devices, order number 11539.

- Kernighan, Brian W. and Dennis M. Ritchie: *The C Programming Language*, *First Edition*. Prentice-Hall, Inc., Englewood Cliffs, NJ 07632, 1978.

- Kernighan, Brian W. and Dennis M. Ritchie: *The C Programming Language*, *Second Edition*. Prentice-Hall, Inc., Englewood Cliffs, NJ 07632, 1988.

- *Programming Language C*, American National Standards Institute, 311 First St. NW, Suite 500, Washington, DC, 20001. ANSI document X3.159, 1989. Available from Global Engineering Documents, telephone 1–800–854–7179.

- *Programming the 29K<sup>™</sup> RISC Family* by Daniel Mann, P T R Prentice-Hall, Inc. 1994

# **Standards and Conventions**

### Standards

This product complies with the following standards:

• COFF: AMD Common Object File Format

Conforms to the AMD-augmented version of AT&T COFF, as described in the AMD *Common Object File Format (COFF) Specification.*

• HIF: AMD Host Interface

Conforms to the AMD Host Interface (HIF) Specification.

• IEEE 754, 1985

Conforms to the IEEE-approved standard for binary floating-point arithmetic.

• UDI: AMD Universal Debugger Interface

Conforms to the AMD Universal Debugger Interface (UDI) Specification.

### Conventions

- UNIX pathnames use a forward slash (/) to separate directories, while MS-DOS pathnames use a backslash (\). For brevity, only the DOS backslash is used when specifying pathnames. In some cases, code examples are specified as either for UNIX or MS-DOS environments and the correct slash is used.

- The following abbreviations may be used in this manual:

- LSB least significant bit

- LSW least significant word

- MSB most significant bit

- MSW most significant word

- NaN not a number

- QNaN quiet not a number

- In this manual, a data word signifies a 32-bit entity; a data halfword signifies a 16-bit entity.

- This manual uses the notational conventions shown in Table 0-1 (unless otherwise noted). These same conventions are used in all the 29K Family support products manuals.

| Symbol Usage    |                                                                                                                                                |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Boldface        | Indicates that characters must be entered exactly as<br>shown. The alphabetic case is significant only when<br>indicated.                      |

| Italic          | Indicates a descriptive term to be replaced with a user-specified term.                                                                        |

| Typewriter face | Indicates computer text input or output in an example or listing.                                                                              |

| []              | Encloses an optional argument. To include the information described within the brackets, type only the arguments, not the brackets themselves. |

| { }             | Encloses a required argument. To include the information described within the braces, type only the arguments, not the braces themselves.      |

|                 | Indicates an inclusive range.                                                                                                                  |

|                 | Indicates that a term can be repeated.                                                                                                         |

|                 | Separates alternate choices in a list—only one of the choices can be entered.                                                                  |

| :=              | Indicates that the terms on either side of the sign are equivalent.                                                                            |

Table 0-1.

Notational Conventions

Simulators

# Chapter 1

# **Using the Simulators**

This chapter provides a brief overview of the available simulators and then describes how to invoke each on UNIX and MS-DOS systems. (The commands are the same for all systems.)

If the user types an incorrect command, the resulting error message is written to the standard error device.

The return codes are as follows:

0 =success not 0 =failure

# **Using the 29K Family Simulators**

There are two simulators available for executing 29K Family application code: the instruction set simulator, **isstip**, and the architectural simulator, **sim29**.

Both simulators support all current 29K Family microprocessors and microcontrollers: the Am29000, Am29005, Am29030, Am29035, Am29040, and Am29050 microprocessors, and the Am29200, Am29205, Am29240, Am29243, and Am29245 microcontrollers.

The intended users of isstip are:

• Software engineers developing and/or debugging 29K Family applications.

The intended users of sim29 are:

- Engineers evaluating the performance of the 29K Family of microprocessors for possible application designs.

- Board designers evaluating different memory configurations to achieve a desired performance.

- Software developers using the profiling capabilities of **sim29** to optimize their code.

### isstip

**isstip** is useful as an introductory evaluation platform and as a debugging tool for many applications. Because it is hardware free, it is low cost and convenient. Being entirely virtual can also aid significantly in debugging critical kernel or interrupt level code, since breakpoints can be set even if interrupts are disabled. The disadvantage is that it is not as fast as hardware, but performance is improving, making the simulator practical for a large set of applications.

**isstip** is compliant with the AMD Universal Debugger Interface (UDI), so it can be invoked from multiple debugger front ends (DFEs). Although most Target Interface Processes (TIPs) use UDI to provide the communication between the target and the DFE, in the case of **isstip**, there is no distinction between the TIP and the target, which is the Instruction Set Simulator. All are contained in one executable called **isstip**. See the UDI online documentation for more information on UDI. Simulators

### sim29

The architectural simulator program, **sim29**, can execute the same application programs as **isstip** but rather than being used as a debugging tool, **sim29** is designed for performance estimation. **sim29** models the processor pipeline, cache, and memory latencies in order to accurately report the elapsed time for a benchmark or application. In addition to simple cycles, several profiling statistics are available, making the simulator useful for optimizing the performance of applications. However, the extra modelling done by the simulator slows its performance, making it impractical for large scale debugging. In addition, its debugging features are limited.

**sim29** is not currently UDI-based but UDI support is planned for a future release.

Simulator options vary according to the processor being simulated. Option variations occur due to architectural differences between processors, and because some processors are simulated with entirely separate implementations than others.

The simulator is implemented by several different programs. The program invoked by the **sim29** "driver" depends on which microprocessor or microcontroller is specified. One program implements the Am29000, Am29005, and Am29050 microprocessors. The second program implements the Am29030 and Am29035 microprocessors. The third program implements the Am29040 microprocessor, and the fourth program implements the Am29200, Am29205, Am29240, Am29243, and Am29245 microcontrollers.

The Am29000, Am29005, and Am29050 processor program mimics the microprocessor's actual implementation in considerable detail, beyond the cycle-by-cycle state defined by the microprocessor's architecture. As such, the performance estimates are quite accurate, but the programs execute somewhat slower and are more prone to failure due to the increased complexity of the program. The remaining programs (those that simulate the Am29030, Am29035, and Am29040 microprocessors, and the Am29200, Am29205, Am29240, Am29243, and Am29245 microcontrollers) model only those parts of the implementation relevant to performance, namely the pipeline and memory channel. As such, they run considerably faster than the Am29000, Am29005, and Am29050 processor simulators, which is an important feature when hundreds of millions of cycles are being simulated.

## **Invoking isstip**

**NOTE:** The **isstip.exe** for MS-DOS hosts supplied with this product uses extended memory on a PC. This facilitates running larger programs on the simulator, the sizes of which are not limited by the amount of conventional memory.

**isstip** is a UDI-conformant Target Interface Process (TIP) for the 29K Family Instruction Set Simulator. It implements the Instruction Set Simulator with an interface defined by the UDI Specification. **isstip** can be used with any UDI-conformant Debugger Front End, such as **mondfe** or the XRAY29K<sup>™</sup> product's **xray29u**.

The **isstip** command and its options should be provided in the UDI Configuration File with its entry. The format of the UDI Configuration for UNIX (**udi\_soc** file) and MS-DOS (**udiconfs.txt** file) hosts is explained in the UDI online documentation.

The UDI Configuration File entry's TIP ID (first field of the entry) acts as the link between the DFE being used and **isstip**. The TIP ID is provided as a command-line argument to the DFE being used. For example, the command-line option –**TIP** of **mondfe** can be used to specify the TIP you want to use:

```

mondfe -D -TIP tip_id

```

This makes the DFEs independent of TIP-specific features and options. Please refer to the appropriate DFE documentation for more information on DFE command-line syntax and options.

Simulators

0395

- **Syntax:** isstip *processor* [-id {0|1}] [-le] [-n] [-p |-v] [-r *boot\_prog*] [-sp {0|1}] [-st *hexaddr*] [-t] [-tm] [-ww]

- **NOTE:** These options are case sensitive.

#### where:

- processor Is one of: -29000, -29005, -29030, -29035, -29040, -29050, -29200, -29205, -29240, -29243 or -29245. These options specify which 29K Family microprocessor to simulate. Based on the option specified, isstip downloads the default ROM file, which can be overridden using the -r option (see the -r option for the default files). The -n option can be used to prevent downloading of any ROM file. Note that the *processor* is required and must be the first argument specified.

- -id {0|1} Specifies whether to simulate a separate Instruction and Data address space. The default is 0, which means that the Instruction and Data spaces are the same. This option only applies to the Am29000, Am29005, and Am29050 processor simulators.

- -le Specifies to simulate a little endian system. The default is big endian.

- -n Can be used to bring up **isstip** without downloading a ROM file.

This may be used if an application has its boot code already linked into the application.

- $-p \mid -v$  When the -p option is specified, the execution mode of the programs is physical mode. When -v is specified, virtual mode execution is simulated. The TLB traps provided implement a one-to-one mapping of physical addresses to virtual addresses. The default mode is physical.

- -r boot\_prog Specifies the osboot or ROM program. The boot\_prog is a full pathname to the file. By default, the simulator will attempt to load the appropriate boot code needed by the compiler, based on the processor specified on the command line.

3395

The default *boot\_prog* depends on the *processor* specified. The defaults are:

| osb00x | For <b>-29000</b> and <b>-29005</b>                   |

|--------|-------------------------------------------------------|

| osb03x | For <b>-29030</b> , <b>-29035</b> , and <b>-29040</b> |

| osb050 | For <b>-29050</b>                                     |

| osb20x | For <b>-29200</b> and <b>-29205</b>                   |

| osb24x | For <b>-29240</b> , <b>-29243</b> , and <b>-29245</b> |

When the **-r** option is specified, **isstip** first looks for *boot\_prog* in the current working directory. If the file is not found, the directories specified in the **PATH** environment variable are searched after replacing the last branch with **lib**. For example, if **PATH** is:

C:\29k\bin;c:\29k\lib;d:\c600\bin;

Then the directories searched by isstip are:

C:\29k\lib and c:\29k\lib and d:\c600\lib

The code contained in this "ROM" file is downloaded and executed by **isstip** before executing the application program. Therefore, if the user's application has the startup code in it, do not use this option.

- -sp {0|1} Specifies whether to simulate a separate ROM and Instruction RAM space. The default is 1, which means that the ROM space is different from Instruction RAM space. By using 0, the Instruction RAM and ROM can be made to refer to the same address space. This is useful when using **isstip** with the XRAY29K debugger.

- -st *hexaddr* For special programs, this can be used to specify the address to be used by the operating system as the highest addressable data address. The default value of 0 is ignored by the operating system.

- -t When specified, enables "trap"ping on certain instructions (like floating-point operations), thus using the trapware installed. When disabled, the simulator performs the necessary operation and produces the result. The default is trap disabled, which may improve the simulation speed for some applications.

- -tm When specified, enables the Timer during simulation. The default is Timer disabled, which provides a slight boost to simulation speed.

- -ww Specifies to simulate word-write only. The default is byte-write allowed.

Simulators

### Example

A sample entry in **udiconfs.txt** for executing on MS-DOS hosts would be:

iss\_id isstip.exe -29000

In the above entry, iss\_id is any ID name of the user's choice.

To use **isstip**, invoke the debugger front end, giving it the TIP ID defined in the configuration file. Make sure that the **udiconfs.txt** file is either in the current working directory, or is defined by the environment variable **UDICONF**. Also, make sure that the **PATH** environment variable is set up so that **isstip.exe** and the *boot\_prog* for the **-29000** option, **osb00x**, can be found. After completing the above steps, the **hello** program can be run using **mondfe** on an MS-DOS host by typing:

mondfe -TIP iss\_id hello

The **-TIP** option of **mondfe** is used to specify which TIP ID to use from the UDI configuration file. By specifying the TIP ID as **iss\_id**, **isstip.exe** is invoked and is passed **-29000** as an argument.

### Invoking sim29

**Syntax:** sim29 processor [processor\_options] [-d] [-e event\_file] [-f frequency] [-h heap\_size] [-0 output\_file ] [-r boot\_prog] [-v] [app\_prog [prog\_args]]

**NOTE:** These options are case sensitive.

#### where:

processor Is one of: -29000, -29005, -29030, -29035, -29040, -29050, -29200, -29205, -29240, -29243 or -29245. These options specify which 29K Family microprocessor to simulate. Note that the *processor* is required and must be the first argument specified.

processor\_options

Are options specific to a processor and can be either *3-bus\_options*, *2-bus\_options*, or *controller\_options*, as described on the following pages, and in more detail in Chapters 3, 4, and 5.

*3-bus\_options* are for the 29K Family three-bus microprocessors, which currently include the Am29000, Am29005, and Am29050 processors; *2-bus\_options* are for the 29K Family two-bus microprocessors, which currently include the Am29030, Am29035, and Am29040 processors; and *controller\_options* are for the 29K Family microcontrollers, which currently include the Am29200, Am29205, Am29240, Am29243, and Am29245 microcontrollers.

*3-bus\_options* Are the options for the Am29000, Am29005, and Am29050 microprocessors:

-cfg=xxSpecifies the setting of the configuration<br/>register, where xx is a 1- to 5-digit<br/>hexadecimal number. This setting overrides<br/>the default setting. No run-time modification<br/>of the configuration register is permitted if<br/>this option is specified.

Simulators

| —n              | Does not allocate two extra words at the end<br>of data sections. The default is to put two<br>extra words at the end of data sections so<br>that the read-ahead library routines, <b>str</b> *()<br>and <b>mem</b> *(), will not try to read beyond the<br>end of memory. |                                      |  |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| –p range        | Specifies code profiling to take place in the specified <i>range</i> of RAM memory space. The <i>range</i> parameter is required, and it specifies a range of hexadecimal values in the form: 1000–2ACE.                                                                   |                                      |  |

| -t max_syscalls | Specifies the maximum number of system<br>call types that will be used during the<br>simulation. This option is used to allocate<br>the array for storing the system call count<br>for different calls. The default is 256 types.                                          |                                      |  |

| -x[error_code]  |                                                                                                                                                                                                                                                                            |                                      |  |

|                 | S                                                                                                                                                                                                                                                                          | An error in the event file occurred. |  |

2-bus\_options controller\_options

| controller_option     |                                                                                                                                                                                                                                                         | for the Am29030 Am29035 and Am29040                                                                                                                       |  |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                       | Are the options for the Am29030, Am29035, and Am29040 microprocessors, and the Am29200, Am29205, Am29240, Am29243, and Am29245 microcontrollers:                                                                                                        |                                                                                                                                                           |  |

|                       | -dcacheoff                                                                                                                                                                                                                                              | Disables the data cache (applies only to the Am29040, Am29240, and Am29243 processors).                                                                   |  |

|                       | $-dynmem \{0 1\}$                                                                                                                                                                                                                                       | Dynamically allocates memory for address<br>references not defined by the application<br>Common Object File Format (COFF) file. 1<br>enables; 0 disables. |  |

|                       | -help                                                                                                                                                                                                                                                   | Outputs ASCII text to standard output that<br>briefly describes all command-line and<br>event-file options.                                               |  |

|                       | -icacheoff                                                                                                                                                                                                                                              | Disables the instruction cache.                                                                                                                           |  |

|                       | p                                                                                                                                                                                                                                                       | Profiles opcode, PC, Load, Store, and trap usage.                                                                                                         |  |

|                       | -SV                                                                                                                                                                                                                                                     | Passes a parameter to <b>osboot</b> indicating that the application is to run in supervisor mode.                                                         |  |

|                       | —u                                                                                                                                                                                                                                                      | Configures memory wait states and enable caches via application software instead of simulator options.                                                    |  |

| -d                    | Dumps the contents of the registers at the end of simulation.                                                                                                                                                                                           |                                                                                                                                                           |  |

| –e event_file         | Specifies the simulator event input file, which is used for other miscellaneous commands. The <i>event_file</i> is a full pathname to the file.                                                                                                         |                                                                                                                                                           |  |

| -f frequency          | Specifies the CPU frequency in MHz.                                                                                                                                                                                                                     |                                                                                                                                                           |  |

| –h heap_size          | Specifies the size of the system heap (in kilobytes). The <i>heap_size</i> parameter is a decimal value. The default system heap size is 32 Kbytes, or <b>–h 32</b> .                                                                                   |                                                                                                                                                           |  |

| –o <i>output_file</i> | Specifies the simulation summary file ( <b>sim.out</b> is the default name). The <i>output_file</i> is a full pathname to the file.                                                                                                                     |                                                                                                                                                           |  |

| -r boot_prog          | Specifies the <b>osboot</b> or ROM program. The <i>boot_prog</i> is a full pathname to the file. By default, the simulator will attempt to load the appropriate boot code needed by the compiler, based on the processor specified on the command line. |                                                                                                                                                           |  |

Simulators

The default *boot\_prog* depends on the *processor* specified. The defaults are:

| osb00x | For <b>-29000</b> and <b>-29005</b> options                   |

|--------|---------------------------------------------------------------|

| osb03x | For <b>-29030</b> , <b>-29035</b> , and <b>-29040</b> options |

| osb050 | For <b>–29050</b> option                                      |

| osb20x | For <b>-29200</b> and <b>-29205</b> options                   |

| osb24x | For <b>-29240</b> , <b>-29243</b> , and <b>-29245</b> options |

When the **-r** option is specified, **sim29** first looks for *boot\_prog* in the current working directory. If the file is not found, the directories specified in the **PATH** environment variable are searched after replacing the last branch with **lib**. For example, if **PATH** is:

C:\29k\bin;c:\29k\lib;d:\c600\bin;

Then the directories searched by **sim29** are:

C:\29k\lib and c:\29k\lib and d:\c600\lib

The code contained in this "ROM" file is downloaded and executed by **sim29** before executing the application program. Therefore, if the user's application has the startup code in it, specify that application file as the *boot\_prog*.

- -v Passes a parameter to **osboot** which will turn on instruction and data address virtual memory translation. This option does not apply to the Am29200 or Am29205 microcontrollers.

- app\_progSpecifies the filename of the program to be simulated. The<br/>app\_prog parameter is not required if the user's application<br/>has boot code linked in, and the -r option is used. Otherwise,<br/>the app\_prog must be provided, and is a full pathname to the<br/>program object file.

- *prog\_args* Specifies command-line options for the program to be simulated. This argument is optional. Programs need not have command-line options to execute properly.

The output generated by the simulator includes the output generated by the program being simulated and the performance statistics, such as the number of processor cycles simulated, and the MIPS (millions of instructions per second).

For a more extensive discussion of the options for each processor type, see Chapters 3, 4, and 5.

#### Example

sim29 -29000 -e mysim.evt -o mysim.out myprog -Wcf

The -29000 option specifies the Am29000 microprocessor is being simulated.

The -e option specifies an event input file. The parameter following the option, **mysim.evt** in this case, is the name of a file that is opened by the simulator at the beginning of run. Events specified within this file are used to control the actions of the simulator.

The –o option specifies that the following filename, **mysim.out**, be assigned as the output file to contain a transcript of the current simulation's results. If the -o option is not specified, the simulator will write the transcript on the file sim.out.

The –o option is the last option in this example, and the following command-line argument (**myapp**) is treated as the filename of the program whose execution is to be simulated. The program file must be in object form, already linked to execute in the simulator's execution environment.

The **-Wcf** argument at the end of the command line represents a hypothetical command-line argument to the myapp program. Command-line arguments for programs whose execution is to be simulated are specified last, in the form the program requires.

#### Example

sim29 -29000 -e dhry2.evt -o dhry2.out dhry2 < dhry2.in

This example illustrates how the command line would be entered for a program that requires input from the standard input device (stdin). The angled bracket indicates (for both MS-DOS and UNIX systems) that the standard input is to be taken from a file whose name immediately follows (**dhry2.in** in this case). Simulator options are specified first, followed by the filename of the program to be simulated (dhry2 in this case).

#### Example

sim29 -29035 -r myboot -sv my\_program

This example illustrates the command line entered to simulate in Am29035 processor mode using the ROM file myboot. The -sv option causes the program to run in supervisor mode.

1 - 13

Simulators

#### Example

sim29 -29050 -r myboot -cfg=b0 my\_program

This example illustrates the command line entered to simulate in Am29050 microprocessor mode using the ROM file **myboot**. The **-cfg** option prevents the simulator from setting the configuration register to the default value at start-up and also prevents any instruction in the ROM or RAM file from setting the configuration register. In this example, the simulator will set the configuration register to the value 0xb0, which sets the register's early load enable (EE), data width (DW), and vector fetch (VF) bits.

### Example

sim29 -29200 hello.lap

This example illustrates the command line to simulate the **hello.lap** program in the Am29200 microcontroller. Because the  $-\mathbf{r}$  option is not specified, the default boot file **osb20x** is used.

### Example

sim29 -29240 -e sim.evt test.lap

This example illustrates simulating the execution of program **test.lap** on the Am29240 microcontroller using the default boot file **osb24x** with the memory configuration as specified in the **sim.evt** file.

# Chapter 2

# **ISSTIP Example**

This chapter provides examples of using the 29K Family instruction set simulator, **isstip**, with the MiniMON29K user interface, **mondfe**. **isstip** is a UDI-conformant Target Interface Process (TIP) that can be used with any UDI-conformant Debugger Front End (DFE). The TIP and the DFE run as separate processes and communicate with each other according to AMD's *Universal Debugger Interface (UDI) Specification*.

There are three items needed before simulating a program using **isstip** and **mondfe**:

- **isstip** The 29K Family Instruction Set Simulator. (Note: Unlike other TIPs, in the case of **isstip**, there is no distinction between the Target Interface Process (TIP) and the target, which is the Instruction Set Simulator. All are contained in one executable called **isstip**.)

- **mondfe** A UDI-conformant Debugger Front End (DFE) to issue commands. For more information, see the **mondfe** documentation.

- UDI Configuration File The communication link for **mondfe** and **isstip**.

There are two environment variables that are used if they are defined: **PATH** and **UDICONF**. See the UDI online documentation for more information on these environment variables.

This chapter first provides an example tutorial for MS-DOS hosts (page 2-2), and then a tutorial for UNIX hosts (page 2-5).

# **Example Tutorial For MS-DOS Hosts**

This tutorial assumes that High C<sup>®</sup> 29K<sup>m</sup> compiler and libraries have been installed on the C:\ drive. Complete the following steps to set up the environment.

1. Create a file with the following contents:

set PATH=C:\29K\BIN;%PATH%

set UDICONF=C:\29K\LIB\UDICONFS.TXT

Name this file udisetup.bat.

2. Run the batch file created above:

udisetup

Now the **PATH** variable is set to pick up the newly installed **mondfe** and **isstip** from the **C:\29K\BIN** directory. The **UDICONF** variable is pointing to the UDI configuration file, **udiconfs.txt**, in the **C:\29K\LIB** directory.

Take a few minutes to go through the **udiconfs.txt** file and the various line-entries. Remember that the first column gives the ID, which is given as a command-line argument to **mondfe**.

3. The line-entry from **udiconfs.txt** that will be used in this example is for the ID, **iss000**. Here is the complete line:

iss000 isstip.exe -29000

The first column, **iss000**, gives the unique ID for the rest of that line. This ID is used as a command-line argument to **mondfe**. The second column gives the executable name of the TIP to use. In this case, it is **isstip.exe**, which is the Instruction Set Simulator TIP. If there is no **isstip.exe** in the current working directory, the **PATH** environment variable is searched to locate the executable. Since the **PATH** has already been set up above, the **isstip.exe** from the **C:\29K\BIN** directory will be used. (NOTE: Remove any files named **isstip.exe** from the current working directory if it is *not* **C:\29K\BIN**.) The rest of the line following "isstip.exe" gives the string of options that will be passed to **isstip.exe** when it is invoked.

The **-29000** option above specifies the "ROM" file that **isstip** must download (to ROM space) before executing any user commands. **isstip** will search the **PATH** variable to locate the osboot file to download (**osb00x** is the default file for the **-29000** option). As per the **PATH** environment variable, **isstip** will download the osboot file found under the **C:\29K\LIB** directory, unless the osboot file exists in the current working directory. The default settings of the rest of the options apply. Refer to page 1-6 for more information on the different options to **isstip**, their meanings, and their default values.

4. To use mondfe to invoke isstip according to the above entry, specify the entry ID, iss000, to mondfe. The –TIP option of mondfe allows you to do exactly that. This example uses the –D command-line option of mondfe to start an interactive debug session. Thus, the complete command-line to use is:

mondfe -D -TIP iss000

The default settings for the remaining command-line options apply. Refer to the **mondfe** manual for more information on the various **mondfe** options, their meanings, and their default values.

5. When **mondfe** is invoked using the above command-line, a sign-on message similar to the following appears:

>AMD MONDFE Version: 4.3.5 IPC Version: 1.4.0 UDI Rev. 1.4.0 <

>TIP Version: 4.0.2 IPC Version: 1.3.0 UDI Rev. 1.3.0<

UDI 1.3 ISSTIP for 29K Family: ROM file: c:\29k\lib\osb00x

MONDFE.EXE>

The first line is printed by **mondfe**, and it gives the version number, the UDI revision of the IPC implementation **mondfe** is using, and the version of the IPC implementation itself. The second line is a formatted display of the version numbers of the different components of **isstip**. The third line is a descriptive string returned by **isstip** about itself. The last line displayed is the **mondfe** prompt, which is **MONDFE.EXE**>.

6. From here on, there are two processes actually running that are transparent to the user: the DFE (mondfe) and the instruction set simulator (isstip). The mondfe Y (Yank) command can be used to download the program as shown below:

```

MONDFE.EXE> Y hello.out

loading hello.out

Loaded TEXT section from 0x00010000 to 0x00013fb4

Loaded DATA section from 0x80003000 to 0x800033a0

Loaded LIT section from 0x800033a0 to 0x80003694

Cleared BSS section from 0x80003698 to 0x80003874

Ignoring COMMENT section (32 bytes) ...

MONDFE.EXE>

```

Then, type a G (Go) command to execute the program as shown below:

```

MONDFE.EXE> G

MONDFE.EXE>Hello, world!

Hello World Stderr!

Process exited with 0x0

MONDFE.EXE>

```

Use the **Q** (**Quit**) command to terminate the debug session as shown below:

MONDFE.EXE> Q MONDFE.EXE> Goodbye.

When exiting from the front end (using the  $\mathbf{Q}$  command), the TIP also is killed.

# **Example Tutorial For UNIX Hosts**

This tutorial assumes that High  $C^{\otimes} 29K^{\mathbb{M}}$  compiler and libraries have been installed under the **/usr** directory. Complete the following steps to set up the environment.

1. Set the **PATH** and **UDICONF** environment variables using the following commands:

setenv PATH /usr/29k/bin:`echo \$PATH`

setenv UDICONF /usr/29k/lib/udi\_soc

Now the **PATH** environment variable is set to pick up the newly installed **mondfe** and **isstip** from the **/usr/29k/bin** directory. The **UDICONF** variable is pointing to the UDI configuration file, **udi\_soc**, in the **/usr/29k/lib** directory.

Take a few minutes to go through the **udi\_soc** file and the various line-entries. Remember that the first column gives the ID, which is given as a command-line argument to **mondfe**.

2. The line-entry from **udi\_soc** that will be used in this example is for the ID, **isstip\_unix**. Here is the complete line:

isstip\_unix AF\_UNIX sockiss -ux isstip -29000

The first column, **isstip\_unix**, gives the unique ID for the rest of that line. This ID is used as a command-line argument to **mondfe**. The second column gives the socket address family, which is **AF\_UNIX**. This means that both the DFE, **mondfe**, and the TIP, **isstip**, are executing on the same machine. The third field is the name of the socket itself. The fourth field gives the executable name of the TIP to use. In this case, it is **isstip**, which is the Instruction Set Simulator TIP. If there is no **isstip** in the current working directory, the **PATH** environment variable is searched to locate the executable.

Since the **PATH** has already been set up above, the **isstip** from the **/usr/29k/bin** directory will be used. (NOTE: Remove any file named **isstip** from the current working directory if it is *not* **/usr/29k/bin**.) The rest of the line following "isstip" gives the string of options that will be passed to **isstip** when it is invoked.

The **-29000** option above specifies the ROM file that **isstip** must download (to ROM space) before executing any user commands. The **isstip** will search the **PATH** variable to locate the osboot file to download (**osb00x** is the default file for the **-29000** option). As per the **PATH** environment variable, **isstip** will download the osboot file found under the **/usr/29k/lib** directory, unless the osboot file exists in the current working directory. The default settings of the rest of the options apply. Refer to page 1-6 for more information on the different options to **isstip**, their meanings, and their default values.

3. To use **mondfe** to invoke **isstip** according to the above entry, specify the entry ID, **isstip\_unix**, to **mondfe**. The **-TIP** option of **mondfe** allows you to do exactly that. This example uses the **-D** command-line option of **mondfe** to start an interactive debug session. Thus, the complete command-line to use is:

mondfe -D -TIP isstip\_unix

The default settings for the remaining command-line options apply. Refer to the **mondfe** manual for more information on the various **mondfe** options, their meanings, and their default values.

4. When **mondfe** is invoked using the above command-line, a sign-on message similar to the following appears:

>AMD MONDFE Version: 4.3.5 IPC Version: 1.4.0 UDI Rev. 1.4.0 <

>TIP Version: 4.0.2 IPC Version: 1.3.1 UDI Rev. 1.3.0<

UDI 1.3 ISSTIP for 29K Family: ROM File: /usr/29k/lib/osb00x

mondfe>

The first line is printed by **mondfe**, and it gives the version number, the UDI revision of the IPC implementation **mondfe** is using, and the version of the IPC implementation itself. The second line is a formatted display of the version numbers of the different components of **isstip**. The third line is a descriptive string returned by **isstip** about itself. The last line displayed is the **mondfe** prompt, which is **mondfe**>.

From here, there are two processes actually running that are transparent to the user: the DFE (mondfe) and the instruction set simulator (isstip). The mondfe Y (Yank) command can be used to download the program as shown below:

```

mondfe> y hello.out

loading hello.out

Loaded TEXT section from 0x00010000 to 0x00013fb4

Loaded DATA section from 0x80003000 to 0x800033a0

Loaded LIT section from 0x800033a0 to 0x80003694

Cleared BSS section from 0x80003698 to 0x80003874

Ignoring COMMENT section (32 bytes) ...

mondfe>

```

Then, type a G (Go) command to execute the program as shown below:

```

mondfe> g

mondfe>Hello, world!

Hello World Stderr!

Process exited with 0x0

mondfe>

```

Use the **Q** (**Quit**) command to terminate the debug session as shown below:

MONDFE.EXE> q MONDFE.EXE> Goodbye.

When exiting from the front end (using the  ${\bf Q}$  command), the TIP also is killed.

Chapter 3

# 29K Family Three-Bus Processor Architecture Simulation

This chapter describes how to use **sim29** to simulate the Am29000, Am29005, and Am29050 microprocessors. The following topics are discussed:

- Simulator Command-Line Syntax on page 3-2

- Default Configuration on page 3-6

- The Event File on page 3-8

- Simulator I/O on page 3-35

# Simulator Command-Line Syntax

| -                   | sim29 processor [-cfg=xx] [-d] [-e event_file] [-f frequency]<br>[-h heap_size] [-n] [-o output_file ] [-p range]<br>[-r boot_prog ] [-t max_syscalls] [-v] [-x [error_code]]<br>[app_prog [prog_args]]                                                             |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| where:              |                                                                                                                                                                                                                                                                     |

| processor           | Is one of: <b>-29000</b> , <b>-29005</b> , or <b>-29050</b> . These options specify which 29K Family three-bus microprocessor to simulate. Note that the <i>processor</i> is required and must be the first argument specified.                                     |

| -cfg=xx             | Specifies the setting of the configuration register, where <i>xx</i> is a 1- to 5-digit hexadecimal number. This setting overrides the default setting. No run-time modification of the configuration register is permitted if this option is specified.            |

| -d                  | Dumps the contents of the registers at the end of simulation.                                                                                                                                                                                                       |

| –e event_file       | Specifies the simulator event input file, which is used for other miscellaneous commands. The <i>event_file</i> is a full pathname to the file.                                                                                                                     |

| -f frequency        | Specifies the CPU frequency in MHz. The default values are 25 for the Am29000 processor, 16 for the Am29005 processor, and 40 for the Am29050 processor.                                                                                                            |

| –h <i>heap_size</i> | Specifies the size of the system heap (in kilobytes). The <i>heap_size</i> parameter is a decimal value. The default system heap size is 32 Kbytes, or <b>–h 32</b> .                                                                                               |

| —n                  | Does not allocate two extra words at the end of data sections.<br>The default is to put two extra words at the end of data<br>sections so that the read-ahead library routines, <b>str*()</b> and<br><b>mem*()</b> , will not try to read beyond the end of memory. |

| –o output_file      | <ul> <li>Specifies the simulation summary file (sim.out is the default name). The <i>output_file</i> is a full pathname to the file.</li> </ul>                                                                                                                     |

| –p <i>range</i> | Specifies code profiling to take place in the specified range of |

|-----------------|------------------------------------------------------------------|

|                 | RAM memory space. The <i>range</i> parameter is required, and it |

|                 | specifies a range of hexadecimal values in the form:             |

|                 | 1000–2ACE.                                                       |

- -r boot\_prog Specifies the osboot or ROM program. (Default is osb00x for the Am29000 and Am29005 microprocessors, and osb050 for the Am29050 microprocessor.) The boot\_prog is a full pathname to the file. By default, the simulator will attempt to load the appropriate boot code needed by the compiler, based on the processor specified on the command line. If the user's application has its boot code linked in, specify that application file as the boot\_prog.

- -t *max\_syscalls* Specifies the maximum number of system call types that will be used during the simulation. This option is used to allocate the array for storing the system call count for different calls. The default is 256 types.

- -v Passes a parameter to **osboot** which will turn on instruction and data address virtual memory translation.

-x[error\_code] Specifies that the simulator exits if an error occurs for one of the enabled error\_code values. The error\_code parameter is optional, and if not given, all codes are enabled. By default, no error codes are enabled. Codes are entered in uppercase letters, immediately following the -x option (e.g., -xAP). Possible values for error\_code are:

- A Address error occurred (e.g., out of bounds).

- K Kernel error occurred (i.e., an error in supervisor mode).

- O Illegal opcode error occurred.

- F An arithmetic trap occurred (e.g., divide by zero).

- P A protection violation occurred.

- S An error in the event file occurred.

- $app\_prog$ Specifies the filename of the program to be simulated. The<br/> $app\_prog$  parameter is not required if the user's application<br/>has boot code linked in, and the  $-\mathbf{r}$  option is used. Otherwise,<br/>the  $app\_prog$  must be provided, and is a full pathname to the<br/>program object file.

*prog\_args* Specifies command-line options for the program to be simulated. This argument is optional. Programs need not have command-line options to execute properly.

The output generated by the simulator includes the output generated by the program being simulated and the performance statistics. Some of the performance statistics are as follows: the number of processor cycles simulated; the MIPS (millions of instructions per second); the percentage time the pipeline was held for various reasons, such as instruction fetch wait, data fetch wait, or LOADM/STOREM wait; register spill and fill count; histogram of different instruction opcodes executed; and memory parameters.

### Example

sim29 -29000 -e mysim.evt -o mysim.out myprog -Wcf

The -29000 option specifies the Am29000 microprocessor is being simulated.

The **-e** option specifies an event input file. The parameter following the option, **mysim.evt** in this case, is the name of a file that is opened by the simulator at the beginning of run. Events specified within this file are used to control the actions of the simulator.

The –o option specifies that the following filename, **mysim.out**, be assigned as the output file to contain a transcript of the current simulation's results. If the –o option is not specified, the simulator will write the transcript on the file **sim.out**.

The **-o** option is the last to be specified, and the following command-line argument (**myprog**) is treated as the filename of the program whose execution is to be simulated. The program file must be in object form, already linked to execute in the simulator's execution environment.

The **–Wcf** argument at the end of the command line represents a hypothetical command-line argument to the **myprog** program. Command-line arguments for programs whose execution is to be simulated are specified last, in the form the program requires.

#### Example

sim29 -29000 -e dhry2.evt -o dhry2.out dhry2 < dhry2.in</pre>

This example illustrates how the command line would be entered for a program that requires input from the standard input device (**stdin**). The angled bracket indicates (for both MS-DOS and UNIX systems) that the standard input is to be taken from a file whose name immediately follows (**dhry2.in** in this case). Simulator options are specified first, followed by the filename of the program to be simulated (**dhry2** in this case).

### Example

sim29 -29050 -r myboot -cfg=b0 my\_program

This example illustrates the command line entered to simulate in Am29050 microprocessor mode using the ROM file **myboot**. The **-cfg** option prevents the simulator from setting the configuration register to the default value at start-up and also prevents any instruction in the ROM or RAM file from setting the configuration register. In this example, the simulator will set the configuration register to the value 0xb0, which sets the register's early load enable (EE), data width (DW), and vector fetch (VF) bits.

# **Default Configuration**

The default settings of the simulator are specified by the Configuration (CFG) register and the Current Processor Status (CPS) register. The contents of these registers on simulator start-up, simulating different 29K Family microprocessors, are described in Table 3-1 and Table 3-2.

If the **-cfg** command-line option is used, the CFG register setting is as specified by the option, except the PRL field, which is set by the simulator according to the mode of simulation.

| Field           | Setting | Description                                                     |

|-----------------|---------|-----------------------------------------------------------------|

| BO              | 0       | Bytes are numbered from left-to-right, big endian               |

| $CD^1$          | 0       | Branch Target Cache enabled                                     |

| $CO^2$          | 0       | Branch Target Cache organized as 64 entries of 4 words each     |

| СР              | 0       | No coprocessor                                                  |

| DW              | 0       | Byte and half-word access not permitted                         |

| EE <sup>2</sup> | 1       | Early loads permitted                                           |

| PRL             | 2       | Processor release level for Am29000 and Am29005 microprocessors |

|                 | 32      | Processor release level for Am29050 processor                   |

| VF              | 1       | Vector area is a block of 256 vector addresses                  |

| RV              | 0       | ROM Vector Area (setting is irrelevant since VF=1)              |

#### Table 3-1. CFG Register Default Settings for the Three-Bus Microprocessor Simulators

#### NOTES:

<sup>1</sup>Not applicable to the Am29005 microprocessor <sup>2</sup>Not applicable to the Am29000 and Am29005 microprocessors.

| Field  | Setting | Description                                   |

|--------|---------|-----------------------------------------------|

| $MM^1$ | 0       | Not monitor mode                              |

| CA     | 0       | Coprocessor inactive                          |

| IP     | 0       | No external interrupts pending                |

| TE     | 0       | Trace enabled                                 |

| TP     | 0       | No trace pending                              |

| TU     | 0       | Unaligned access trap disabled                |

| FZ     | 1       | In freeze mode                                |

| LK     | 0       | LOCK controlled by LOADSET, LOADL, and STOREL |

| RE     | 1       | Instruction access from ROM                   |

| WM     | 0       | Wait mode disabled                            |

| PD     | 1       | Data address translation disabled             |

| PI     | 1       | Instruction address translation disabled      |

| SM     | 1       | Supervisor mode                               |

| IM     | 0       | Interrupt mask cleared                        |

| DI     | 1       | Interrupts enabled                            |

| DA     | 1       | Interrupt and traps enabled                   |

#### Table 3-2. CPS Register Default Settings for the Three-Bus Microprocessor Simulators

#### NOTE:

<sup>1</sup>Not applicable to the Am29000 and Am29005 microprocessors.

# **The Event File**

The event file is a command file used to specify simulation control parameters, most of which are not handled by the command line. These options primarily consist of memory configuration and wait states.

The simulator executes a program by a combination of direct execution and interpretation. The simulation control program is in charge at all times. A simulated CPU clock drives the simulation. Both rising and falling edges are simulated, and register contents become valid outputs on rising edges, while new contents are clocked in on falling edges, in general.

In addition to reading signals from the processor clock—on which the simulator depends to fetch, decode and execute instructions successively in the target program—the simulator optionally will read an event file that contains 1 or more single-line entries, each consisting of a processor clock value and a command. The processor clock value tells the simulator when the event is to occur, and the command specifies a task for the simulator to do at that time. Commands are provided for entering comments into the output file, stopping the simulation at a particular time, setting simulator parameters, showing current state information, and the like.

## Specifying Constants in the Event File

The Am29000, Am29005, and Am29050 processor simulators will accept constant values encoded in decimal, hexadecimal, octal, and binary format, as well as character constants. The rules to express constants in these various radices are straightforward. In general, they conform to similar rules for expressing constant values in the C language, with a few exceptions.

### **Decimal Constants**

The simulator assumes that constant values are expressed in decimal form, unless explicitly declared otherwise. A decimal constant can be expressed either as a contiguous series of digits in the range 0–9, or as a group of decimal digits preceded by the prefix **D** or **d**, and enclosed within single-quote characters. In the case where digits are enclosed within single quotes, embedded space characters are permitted. When expressed as simple decimal integers, space characters serve to separate values. Leading zero digits are ignored in any case. Examples of legal decimal constants are shown below:

0 19 d'27' d'1 3' d'025' 0189

#### **Hexadecimal Constants**

Traditionally, hexadecimal constants are entered by prefixing the value with the characters 0X or 0x; however, the simulator also allows them to be entered as a group, prefixed by **H**, **h**, **X** or **x**, and enclosed within single-quote characters. Hexadecimal values are restricted to the characters 0–9 and A–F or a–f. In the case where hexadecimal values are enclosed within single-quote characters, embedded space characters are permitted. When expressed as simple hexadecimal integers, space characters serve to separate values. Leading zero digits are ignored in any case. Examples of legal hexadecimal constants are shown below:

OxbE OX H'FF' h'7 8' x'2a' Oxee123

### **Octal Constants**

Octal constants are entered by prefixing the value with the letter  $\mathbf{O}$  or  $\mathbf{o}$ , and enclosing the octal digits within single-quote characters. Octal values are restricted to sequences of digits in the range 0–7. Embedded spaces within the octal integer value are allowed. Examples of legal octal integer values are shown below:

O'13' O'17 7' O'06352'

## **Binary Constants**

Binary constants are entered by prefixing the value with the letter **B** or **b**, and enclosing the binary digits within single-quote characters. Binary values are restricted to sequences of the digits 0 or 1. Embedded spaces within the binary integer value are allowed. Alternatively, binary constant values can be expressed by prefixing the sequence of digits with **0b** or **0B**, in which case, embedded spaces are not allowed. Examples of legal binary integer values are shown below:

B'1010 0000 1001 0101' 0b10111000

### **Character Constants**

Character constants consist of single-byte values, which are enclosed by single-quote characters. The value of a character constant is taken to be its ASCII equivalent numeric value. Each character occupies a single 8-bit byte. Only one character can be entered in any of the legal representations; character "strings" are not allowed.

A character may be expressed by its keyboard equivalent (e.g., A), or for control or unprintable characters in the ASCII set, a backslash (\) character, followed by its octal numeric equivalent is allowed. For example, the character constant \014 is assumed to represent a decimal value of 12, which is the ASCII form-feed character.

Examples of common character constants are shown below:

'A' 'a' '+' '\*' '=' '9' '@'

Examples of character constants expressed using the leading backslash provision are shown on the following line:

'\014' '\177' '\376' '\0' '\256'

An extension to the leading backslash representation includes commonly used control and quotation characters expressed as shown below:

| \t                      | Horizontal tab         |

|-------------------------|------------------------|

| ∖n                      | Newline = linefeed     |

| \0                      | ASCII NULL character   |

| $\backslash \backslash$ | Backslash              |

| $\backslash$ '          | Single-quote character |

| $\setminus$ "           | Double-quote character |

| \f                      | Form-feed              |

| \v                      | Vertical tab           |

| \r                      | Return                 |

| ∖b                      | Backspace              |

## **Event File Syntax**

**Syntax:** cyclenum command

#### where:

- *cyclenum* Specifies a time in processor clock cycles when the event is to be executed by the simulator, or a + sign can be used before the time to indicate relative time (+n cycles after the last command). All values are integral numbers of cycles, as would be reported by the CPU clock.

- *command* Specifies a simulator command. These are discussed in detail in the following pages. Each command must be completely specified on a single line. The commands are case insensitive.

Multiple events with the same *cyclenum* can be specified; however, the events must be in ascending time order in the file. That is, each entry must have an equal or greater time value than the previous entry. Events with equal time values are "executed" by the simulator all at once, one following the other, in the order they occur in the file.

When the processor clock value equals an event's *cyclenum*, the event command is executed. Events that the user wishes to be executed at the beginning of the simulation can be entered with a time value of 0. This will guarantee that they are acted on immediately when the simulation begins.

Commands vary in composition, but each command begins with a keyword that designates the function it performs. A command must fit on a single line in the event file, as there is no way to continue a command from one line to another. This does not present a problem, because all simulator commands are short.

The simulator processes events on each pass through its main loop. In this way, the simulator can faithfully reproduce the effect of an external stimulus, or delay, and report the resulting performance effects in the output log.

Table 3-3 shows the list of available simulator commands, and includes a short description of each. The individual commands are fully described in the pages that follow.

| Command | Description                                                                      | Page |

|---------|----------------------------------------------------------------------------------|------|

| COM     | Places a comment in the simulator output file                                    | 3-14 |

| DELTA   | Selects addresses and registers to monitor for changed values                    | 3-15 |

| DUMP    | Permits dumping segment, data, instruction, TLB, BTC, and register file contents | 3-17 |

| LOG     | Selects logging of instructions, floating-point unit, and channel activity       | 3-19 |

| ONERROR | Specifies action to perform if an error occurs                                   | 3-22 |

| SET     | Sets simulator parameters and configuration                                      | 3-24 |

| STOP    | Stops the simulator                                                              | 3-33 |

| TITLE   | Changes the title on simulator output                                            | 3-34 |

Table 3-3.

Three-Bus Microprocessor Simulator Events

## **COM** — Simulator Comment

**Syntax:** cyclenum COM string

#### where:

- *cyclenum* Specifies the time at which the comment should be written into the simulator output file.

- *string* Specifies a string of characters, up to an end of line, that is to be written to the simulator output file.

The **COM** command writes a message, specified by the *string* parameter, to the simulator's output file at the designated time. This facility is useful to indicate that a particular portion of a program has been reached, or to title succeeding output.

### Example

| 105233 | COM | ========== | ======= | === | ========= | ===: | ===== |

|--------|-----|------------|---------|-----|-----------|------|-------|

| 105233 | COM | SIMULATOR  | OUTPUT  | IN  | VICINITY  | OF   | BUG   |

| 105233 | COM | =========  | ======  | === | ========  | ===: | ===== |

In the example above, three comments are to be written to the simulator output file when the simulator clock value is equal to or greater than **105233** cycles.

## **DELTA** — Enable Delta Monitor

| Syntax:  | cyclenum DELTA SHOW class format address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| where:   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| cyclenum | Specifies when the <b>DELTA</b> command is to take place.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| SHOW     | Specifies that the contents of the changed location are to be written<br>to the simulator's output file.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| class    | Specifies the class of data to be monitored. The class can be one ofthe following:Specifies a general purpose register.REGSpecifies a general purpose register.DATASpecifies a data memory location.IROMSpecifies an instruction ROM location.IRAMSpecifies an instruction RAM location.SPECIALSpecifies a special register.PERIPHERALSpecifies a peripheral register.                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |