# Processor Initialization and Run-Time Services OSBOOT

#### Processor Initialization and Run-Time Services: OSBOOT, Release 3.3

© 1991–1995 by Advanced Micro Devices, Inc.

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of Advanced Micro Devices, Inc.

Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subdivision (b)(3)(ii) of the Rights in Technical Data and Computer Software clause at 252.227–7013. Advanced Micro Devices, Inc., 5204 E. Ben White Blvd., Austin, TX 78741–7399.

29K, Am29005, Am29030, Am29035, Am29040, Am29050, Am29200, Am29205, Am29240, Am29243, Am29245, MiniMON29K and XRAY29K are trademarks of Advanced Micro Devices, Inc.

AMD and Am29000 are registered trademarks of Advanced Micro Devices, Inc.

High C is a registered trademark of MetaWare, Inc.

Other product or brand names are used solely for identification and may be the trademarks or registered trademarks of their respective companies.

The text pages of this document have been printed on recycled paper consisting of 50% recycled fiber and 50% virgin fiber; the post-consumer waste content is 10%. These pages are recyclable.

Advanced Micro Devices, Inc. 5204 E. Ben White Blvd. Austin, TX 78741–7399

#

# Contents

#### About OSBOOT

| OSBOOT Documentation         | viii |

|------------------------------|------|

| About This Manual            | viii |

| Suggested Reference Material | x    |

| Standards and Conventions    | xi   |

| Standards                    | xi   |

| Conventions                  | xii  |

#### Chapter 1

#### **Overview of OSBOOT**

| The Bootstrap Module                       | 1-2 |

|--------------------------------------------|-----|

| The Kernel                                 |     |

| MiniMON29K <sup>™</sup> and OSBOOT         | 1-3 |

| About DBG_CORE                             | 1-3 |

| About MONTIP                               | 1-3 |

| The OSBOOT/DBG_CORE/MONTIP/DFE Environment | 1-4 |

#### Chapter 2

#### Using OSBOOT

| OSBOOT/Simulator Model | 2-2 |

|------------------------|-----|

| OSBOOT/DBG_CORE Model  | 2-3 |

| Stand-Alone OSBOOT/Application Model          | 2-5 |

|-----------------------------------------------|-----|

| Stand-Alone OSBOOT/DBG_CORE/Application Model | 2-6 |

#### Chapter 3

#### **OSBOOT Directory and File Organization**

| he boot Subdirectory  | 4 |

|-----------------------|---|

| he traps Subdirectory | 6 |

#### Chapter 4

#### **OSBOOT Bootstrap Module**

| OSBOOT Global Register Usage      |      |

|-----------------------------------|------|

| OS Start-Up and WARN Trap Handler |      |

| OS Cold Start                     |      |

| Processor Initialization          |      |

| Memory Configuration              | 4-13 |

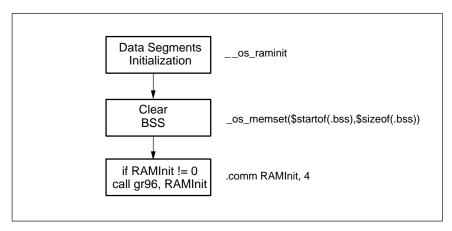

| Data Segments Initialization      | 4-16 |

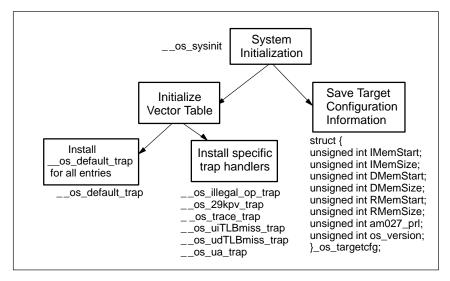

| System Initialization             | 4-18 |

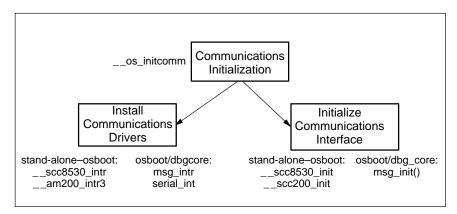

| Communications Initialization     | 4-21 |

#### Chapter 5

#### **OSBOOT Trap Handlers**

| Protection Violation Trap Handler | 5-2 |

|-----------------------------------|-----|

| Unaligned Access Trap Handler     | 5-4 |

| Arithmetic Trap Handlers          | 5-7 |

#### Chapter 6

#### **HIF Run-Time Services**

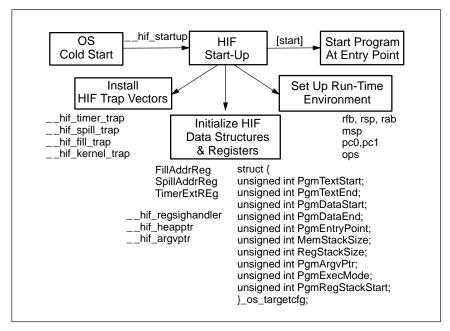

| HIF Kernel Start-Up Module | 6-2 |

|----------------------------|-----|

| Run-Time Environment       | 6-5 |

| Register Stack and Memory Stack Arrangement                                |      |

|----------------------------------------------------------------------------|------|

| HIF Services                                                               | 6-9  |

| Host HIF Services                                                          | 6-11 |

| Stand-Alone OSBOOT/Application Model                                       | 6-11 |

| OSBOOT/Simulator Model                                                     | 6-11 |

| OSBOOT/DBG_CORE Model and Stand-Alone<br>OSBOOT/DBG_CORE/Application Model | 6-12 |

| DBG_CORE Message System Interface                                          | 6-14 |

| How the MiniMON29K Messages are Used                                       | 6-15 |

| Implementation of os_V_msg Message Interrupt Handler                       | 6-20 |

| Implementation of Message Communications in HIF Kernel                     | 6-21 |

|                                                                            |      |

#### Chapter 7

## Building OSBOOT or OSBOOT/DBG\_CORE

| Building OSBOOT for Simulators                         |      |

|--------------------------------------------------------|------|

| MS-DOS                                                 | 7-5  |

| UNIX                                                   | 7-6  |

| Building OSBOOT/DBG_CORE for Target Hardware Platforms | 7-8  |

| MS-DOS                                                 |      |

| UNIX                                                   | 7-11 |

| Building OSBOOT for Stand-Alone Systems                | 7-14 |

| Building a Relocatable Version of OSBOOT               | 7-14 |

| Building a Relocatable Version of OSBOOT/DBG_CORE      | 7-16 |

| Building a Stand-Alone System                          | 7-18 |

| OSBOOT Configuration                                   | 7-21 |

| Sample Linker Command File                             |      |

#### Appendix A

#### Examples

| Building the Stand-Alone OSBOOT/Application Model for the SE29240<br>Evaluation Board        | A-2  |

|----------------------------------------------------------------------------------------------|------|

| Building the Stand-Alone OSBOOT/DBG_CORE/ Application Model for the SE29040 Evaluation Board | A-4  |

| Building the OSBOOT/Application Model to Transfer from<br>ROM to SRAM                        | A-6  |

| Building the OSBOOT/Application Model to Transfer from<br>ROM to DRAM                        | A-9  |

| Building OSBOOT/DBG_CORE for a System Without DRAM                                           | A-11 |

#### Appendix B

#### Using the HIF IOCTL Service for Non-Blocking Reads

| The Problem         | B-1 |

|---------------------|-----|

| The Solution        | B-2 |

| Suggested Reference | B-5 |

#### Appendix C

#### Defining a Trap to Switch to Supervisor Mode

| Switching to Supervisor Mode | C-2 |

|------------------------------|-----|

| Remaining in Supervisor Mode | C-2 |

| Example Code                 | C-2 |

#### Index

iv

# Figures and Tables

### Figures

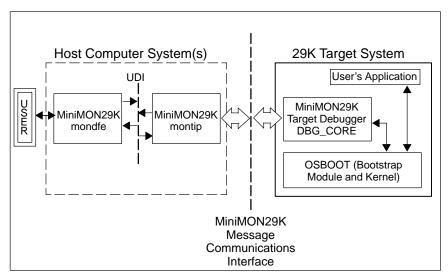

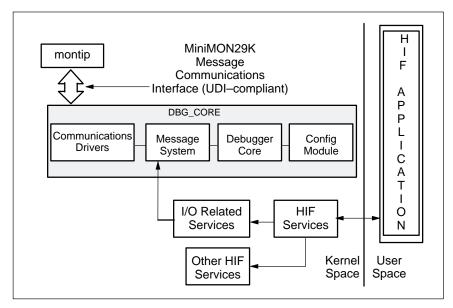

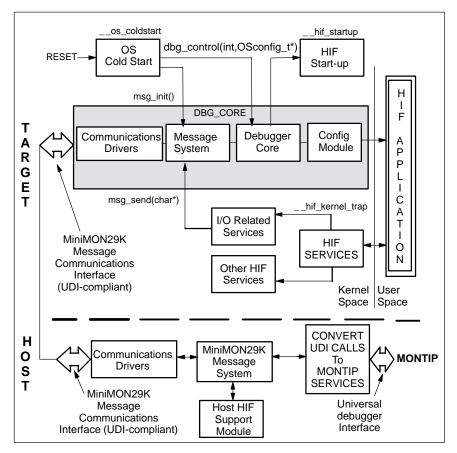

| Figure 1-1. | MiniMON29K Software Components                | 1-1  |

|-------------|-----------------------------------------------|------|

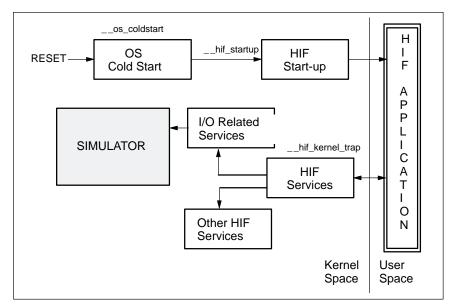

| Figure 2-1. | OSBOOT/Simulator Model                        | 2-2  |

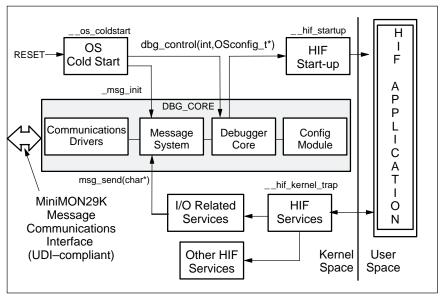

| Figure 2-2. | OSBOOT/DBG_CORE Model                         | 2-4  |

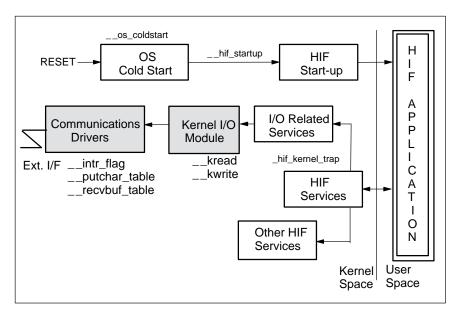

| Figure 2-3. | Stand-Alone OSBOOT/Application Model          | 2-5  |

| Figure 2-4. | Stand-Alone OSBOOT/DBG_CORE/Application Model | 2-6  |

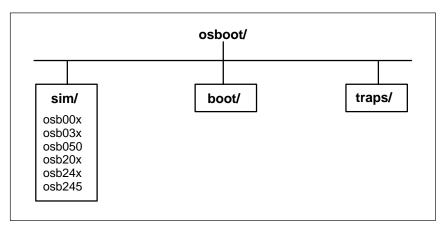

| Figure 3-1. | OSBOOT Directory and File Organization        | 3-3  |

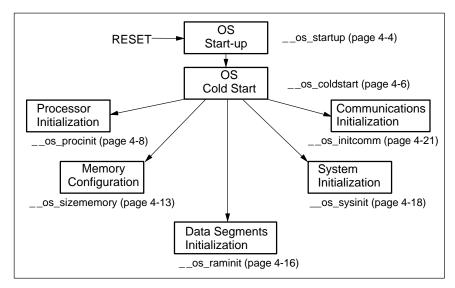

| Figure 4-1. | OSBOOT Bootstrap Module                       | 4-1  |

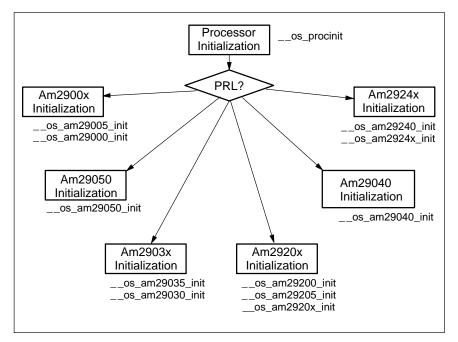

| Figure 4-2. | Processor Initialization                      | 4-8  |

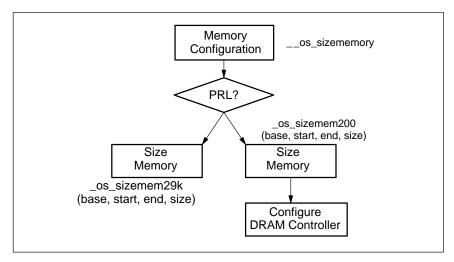

| Figure 4-3. | Memory Configuration                          | 4-13 |

| Figure 4-4. | Data Segments Initialization                  | 4-16 |

| Figure 4-5. | System Initialization                         | 4-18 |

| Figure 4-6. | Communications Initialization                 | 4-21 |

| Figure 6-1. | HIF Kernel Start-Up Module                    | 6-2  |

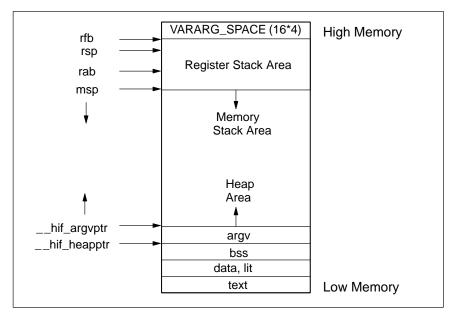

| Figure 6-2. | Register Stack and Memory Stack Arrangement   | 6-8  |

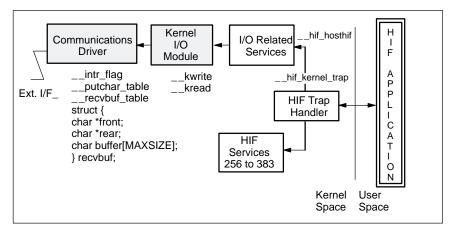

| Figure 6-3. | HIF Services Module                           | 6-9  |

| Figure 6-4. | OSBOOT/DBG_CORE Model and MONTIP              | 5-13 |

| Figure 7-1. | OSBOOT Directory and File Organization        | 7-3  |

| Figure 7-2. | Subdirectory for Simulator Versions of OSBOOT | 7-4  |

| Figure 7-3. | Naming Conventions for OSBOOT/DBG_CORE Files  | 7-8  |

#### Tables

| Table 0-1. | Notational Conventions                      | ciii |

|------------|---------------------------------------------|------|

| Table 3-1. | OSBOOT Linker Command Files                 | 3-2  |

| Table 3-2. | OSBOOT Source Files under boot Subdirectory | 3-4  |

| Table 3-3. | Arithmetic Trap Handler Source Files        | 3-7  |

| Table 4-1. | Register Definitions                                  | 4-2  |

|------------|-------------------------------------------------------|------|

| Table 4-2. | Processor PRL Fields                                  | 4-10 |

| Table 5-1. | Special Virtual Registers                             | 5-2  |

| Table 5-2. | Unique Protection Violation Trap Handlers             | 5-3  |

| Table 5-3. | Option (OPT) Bit Definitions                          | 5-4  |

| Table 5-4. | Unaligned Access Combinations                         | 5-4  |

| Table 5-5. | Unaligned Access Unique Handlers                      | 5-6  |

| Table 6-1. | Registers and Symbolic Names for Run-Time Information | 6-5  |

| Table 6-2. | Run-Time Setup Data                                   | 6-6  |

| Table 7-1. | OSBOOT for Simulators                                 | 7-1  |

| Table 7-2. | Sample OSBOOT Configurations                          | 7-2  |

| Table 7-3. | Linker Command Files for Simulator Versions of OSBOOT | 7-5  |

| Table 7-4. | Linker Command Filenames for Supported Targets        | 7-22 |

| Table 7-5. | Configuration Parameters                              | 7-23 |

| Table 7-6. | Configuration Parameters                              | 7-24 |

| Table 7-7. | Configuration Parameters                              | 7-25 |

# About OSBOOT

The Advanced Micro Devices (AMD<sup>®</sup>) **osboot** software contains the bootstrap module for the 29K<sup>™</sup> Family of processors. The arithmetic instruction emulation routines for certain 29K Family instructions are part of the bootstrap module. **osboot** also includes a small kernel, called the HIF kernel, that provides the run-time support for application programs written in high-level languages. In addition, **osboot** isolates the processor dependencies from the application programs, offering a considerable decrease in design time for the developer.

**osboot** is ported to work with the AMD MiniMON29K<sup>m</sup> debugger core, **dbg\_core**. This manual describes the interactions between **osboot** and **dbg\_core**.

**osboot** is used as the bootstrap program by the architectural simulator, **sim29**, and the instruction set simulator, **isstip**, in the AMD High  $C^{\otimes} 29K^{\mathbb{M}}$  and MiniMON29K Software Development Kit.

This chapter provides an overview of the contents of the **osboot** documentation and describes the formatting conventions used within it.

### **OSBOOT** Documentation

This documentation is written for advanced programmers using **osboot** to develop applications for the 29K Family of microprocessors and microcontrollers. For more information on these microprocessors and microcontrollers, see the list of suggested reference materials that follows.

#### **About This Manual**

Chapter 1: "Overview of OSBOOT" describes the major components of the **osboot** software and how it can be used to debug application programs using 29K Family microprocessors.

Chapter 2: "Using OSBOOT" describes the different ways **osboot** can be used. Models are used to show the various roles that **osboot** can play.

Chapter 3: "OSBOOT Directory and File Organization" describes the files used to make **osboot** and the directories in which they reside.

Chapter 4: "OSBOOT Bootstrap Module" describes the steps performed by the initialization module.

Chapter 5: "OSBOOT Trap Handlers" describes the Protection Violation, Unaligned Access, and Floating-Point Arithmetic Trap Handlers.

Chapter 6: "HIF Run-Time Services" describes the functions provided by the **osboot** HIF kernel, the run-time register and memory stack arrangements, and the implementations of the HIF services. The implementation of the HIF services is described in the context of the three models of **osboot** usage.

Chapter 7: "Building OSBOOT or OSBOOT/DBG\_CORE" describes the steps involved in building **osboot** for simulators and the MiniMON29K debugger core, **dbg\_core**. Both MS-DOS and UNIX environments are discussed. The chapter also describes the configurable link-time parameters of **osboot**.

Appendix A: "Examples" provides several examples of common test models using the **osboot** software, both with and without **dbg\_core**.

Appendix B: "Using the HIF IOCTL Service for Non-Blocking Reads" provides an example of how a non-blocking read can be used to create an interactive menu that allows subsequent processing to continue while waiting for user input.

Appendix C: "Defining a Trap to Switch to Supervisor Mode" describes how to place a 29K Family microprocessor or microcontroller in supervisor mode.

"Index" provides an index to the manual.

#### **Suggested Reference Material**

The following reference documents may be of use to the osboot user:

- *Programming the 29K<sup>™</sup> RISC Family* by Daniel Mann, P T R Prentice-Hall, Inc. 1994.

- Am29000<sup>®</sup> and Am29005<sup>™</sup> User's Manual and Data Sheet Advanced Micro Devices, order number 16914.

- Am29030<sup>™</sup> and Am29035<sup>™</sup> Microprocessors User's Manual and Data Sheet Advanced Micro Devices, order number 15723.

- Am29040<sup>™</sup> Microprocessor Data Sheet Advanced Micro Devices, order number 18459.

- Am29040<sup>™</sup> Microprocessor User's Manual Advanced Micro Devices, order number 18458.

- Am29050<sup>™</sup> Microprocessor Data Sheet Advanced Micro Devices, order number 15039.

- Am29050<sup>™</sup> Microprocessor User's Manual Advanced Micro Devices, order number 14778.

- Am29200<sup>™</sup> and Am29205<sup>™</sup> RISC Microcontrollers Data Sheet Advanced Micro Devices, order number 16361.

- Am29200<sup>™</sup> and Am29205<sup>™</sup> RISC Microcontrollers User's Manual Advanced Micro Devices, order number 16362.

- Am29240<sup>™</sup>, Am29245<sup>™</sup>, and Am29243<sup>™</sup> RISC Microcontrollers Data Sheet Advanced Micro Devices, order number 17787.

- Am29240<sup>™</sup>, Am29245<sup>™</sup>, and Am29243<sup>™</sup> RISC Microcontrollers User's Manual Advanced Micro Devices, order number 17741.

- Harbison, Samuel P. and Guy L. Steele, Jr.: *C: A Reference Manual, Second Edition*, Prentice-Hall, Inc., Englewood Cliffs, NJ 07632, 1987.

- *Host Interface (HIF) Specification* Advanced Micro Devices, order number 11539.

## **Standards and Conventions**

#### Standards

This product complies with the following standards:

• ANSI C: American National Standards Institute C

Conforms to the ANSI-approved document "Programming Language C," document X3.159, 1989.

• COFF: AMD Common Object File Format

Conforms to the AMD-augmented version of AT&T COFF, as described in the AMD *Common Object File Format (COFF) Specification.*

• HIF: AMD Host Interface

Conforms to the AMD Host Interface (HIF) Specification.

• IEEE 754, 1985

Conforms to the IEEE-approved standard for binary floating-point arithmetic.

• UDI: AMD Universal Debugger Interface

Conforms to the AMD Universal Debugger Interface (UDI) Specification.

#### Conventions

- UNIX pathnames use a forward slash (/) to separate directories, while MS-DOS pathnames use a backslash (\). For brevity, only the DOS backslash is used when specifying pathnames. In some cases, code examples are specified as either for UNIX or MS-DOS environments and the correct slash is used.

- The following abbreviations may be used in this manual:

- LSB least significant bit

- LSW least significant word

- MSB most significant bit

- MSW most significant word

- NaN not a number

- QNaN quiet not a number

- In this manual, a data word signifies a 32-bit entity; a data halfword signifies a 16-bit entity.

- This manual uses the notational conventions shown in Table 0-1 (unless otherwise noted). These same conventions are used in all the 29K Family support products manuals.

| Symbol          | Usage                                                                                                                                          |  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Boldface        | Indicates that characters must be entered exactly as<br>shown. The alphabetic case is significant only when<br>indicated.                      |  |

| Italic          | Indicates a descriptive term to be replaced with a user-specified term.                                                                        |  |

| Typewriter face | Indicates computer text input or output in an example or listing.                                                                              |  |

| []              | Encloses an optional argument. To include the information described within the brackets, type only the arguments, not the brackets themselves. |  |

| { }             | Encloses a required argument. To include the information described within the braces, type only the arguments, not the braces themselves.      |  |

|                 | Indicates an inclusive range.                                                                                                                  |  |

|                 | Indicates that a term can be repeated.                                                                                                         |  |

|                 | Separates alternate choices in a list—only one of the choices can be entered.                                                                  |  |

| :=              | Indicates that the terms on either side of the sign are equivalent.                                                                            |  |

Table 0-1.

Notational Conventions

# Chapter 1

# **Overview of OSBOOT**

AMD's **osboot** software, developed for the 29K Family of RISC microprocessors and microcontrollers, is a bootstrap program that resides in the ROM or instruction space of a 29K Family microprocessor target system. **osboot**'s main function is to control the execution states of the 29K Family microprocessor or microcontroller based on different hardware configurations. When a target system is reset, the microprocessor begins to fetch instructions from the **osboot** module in order to perform the target's initialization process.

There are two major components in the **osboot** module: a configurable bootstrap module and a small kernel for application programs. Each is described in this chapter. In addition, this chapter describes how **osboot** works with **dbg\_core** and **montip**. Figure 1-1 illustrates the role of **osboot** in the High C 29K and MiniMON29K Software Development Kit.

Figure 1-1. MiniMON29K Software Components

#### The Bootstrap Module

The bootstrap module of **osboot** provides the processor start-up functions, the optional floating-point emulation routines, the routines used to configure external memory dynamically, and the routines that provide for the RESET of any external or internal hardware that needs to be reset. These functions take control of the processor upon reset and perform the necessary tasks to initialize the target system to a defined state. The process of initializing the system at processor reset is called the *bootstrap* process or the *cold start* process. The bootstrap module must be loaded at offset 0x0 (zero) in the ROM address space or at offset 0x0 (zero) in the instruction address space from which the processor initiates its first instruction fetch.

Certain arithmetic instructions (mostly floating-point operations) of the 29K Family instruction set are not supported directly in the hardware of some members of the 29K Family. These instructions cause a trap when they are executed, and are emulated by the software trap routines. For more information on the trapped operations, see the "OSBOOT Trap Handlers" chapter.

#### **The Kernel**

The kernel takes control after the completion of the bootstrap process. It creates a single-threaded operating system environment in which programs can execute. It provides run-time support for application programs, especially for those written in high-level languages. In providing this support, the kernel implements the processor-specific services defined in AMD's *Host Interface (HIF) Specification* (as opposed to file and I/O services). Processor-specific services are those services with a task/request number over 256. Hence, this kernel is called the HIF kernel of **osboot**.

## MiniMON29K and OSBOOT

AMD's MiniMON29K software provides a means of debugging and testing 29K Family microprocessor application programs. The two major sections of the MiniMON29K software discussed in this manual are the debug core module (**dbg\_core**) and the MiniMON29K target interface process (**montip**). **osboot** provides a simple operating system that can be linked with **dbg\_core** to provide an environment to develop, execute, and debug embedded applications based on 29K Family microcontroller or microprocessor targets. The following sections provide an overview of this environment.

#### About DBG\_CORE

**dbg\_core** is the *target-resident* debugger module of the MiniMON29K product. "Target-resident" means that **dbg\_core** resides on the target hardware. Linking **osboot** with **dbg\_core** creates an environment in which the programmer can develop, execute, and debug 29K Family microprocessor embedded applications on the target itself.

#### About MONTIP

**montip** is the *host-resident* debugger module of the MiniMON29K product. "Host-resident" means that **montip** resides on a PC or UNIX workstation (rather than the target hardware). **montip** and **dbg\_core** share a common message system and can understand each other's communications. The communication system used by **montip** is media-independent, but has been implemented to support serial ports and parallel ports.

**montip** is implemented according to AMD's Universal Debugger Interface (UDI) specification. To use **montip** for debugging, it must be connected to a UDI-compliant Debugger Front End (DFE). DFEs provide the user interface for the debugging process. Because of the UDI standard, the DFE is isolated from the execution vehicle. In this way, the same debug tools can be used with a software target, emulator, or monitor. UDI-compliant DFEs currently available include **mondfe** (provided with the MiniMON29K product), XRAY29K<sup>TM</sup>, UDB<sup>TM</sup>, and gdb. Other DFEs are currently in development.

#### The OSBOOT/DBG\_CORE/MONTIP/DFE Environment

Within the MiniMON29K product, **osboot** is linked with **dbg\_core** to provide an environment to develop, execute, and debug embedded applications on targets based on 29K Family microprocessors. The following example (illustrated in Figure 1-1 on page 1-1) provides a high-level overview of the interactions between **osboot**, **dbg\_core**, **montip**, and the DFE during the debugging process. In Figure 1-1, **mondfe** is used as the DFE. A more thorough example is provided in the "Using OSBOOT" chapter.

Suppose a user wants to view the contents of a register on the target's 29K Family microprocessor. Using a UDI-compliant DFE on the host computer system, the user requests the contents of a register on the 29K Family target. This request is passed via UDI to **montip** (still on the host computer system). Upon receiving the request from the DFE, **montip** passes the request via MiniMON29K messages on to the **dbg\_core** module on the target. In turn, the **dbg\_core** module communicates with **osboot** through the debug channel to retrieve the results of the request. The results are passed back to the user's DFE by reversing the process. Executing a program or setting a breakpoint from the DFE is done in a similar manner.

The advantage of separating UDI and MiniMON29K messages is that UDI messages can travel over (for example) an Ethernet network (local- or wide-area), while MiniMON29K messages travel over a serial link (or parallel link or shared memory) to the target board. This flexibility allows communications to take place over the most convenient available media.

#

# Chapter 2 Using OSBOOT

The **osboot** software is used as the bootstrap program by the architectural simulator, **sim29**, and the instruction set simulator, **isstip**, of AMD's High C 29K and MiniMON29K Software Development Kit. **osboot** is also a simple operating system which is ported to the MiniMON29K debugger core, **dbg\_core**. The design of **osboot** is such that all or portions of it can be linked with application programs to produce stand-alone systems.

The following sections briefly discuss several models using the **osboot** software:

- OSBOOT/Simulator Model on page 2-2

- OSBOOT/DBG\_CORE Model on page 2-3

- Stand-Alone OSBOOT/Application Model on page 2-5

- Stand-Alone OSBOOT/DBG\_CORE/Application Model on page 2-6

## **OSBOOT/Simulator Model**

The simplest implementation among those described in this chapter is the OSBOOT/Simulator Model, shown in Figure 2-1. Because a simulator is a software target (that is, no actual hardware is involved), **osboot** uses a stripped-down version of the bootstrap module. In the model shown in Figure 2-1, **osboot** neither implements routines to configure external memory dynamically, nor does it initialize the external communications interface. In this model, when the application program requests an I/O service, the simulator intercepts the I/O requests to the HIF kernel and performs the necessary operations using the services of its host operating system.

AMD provides two different simulators: the 29K Family architectural simulator (**sim29**, which provides timing and statistical information about the application), and the target interface process instruction set simulator (**isstip**, which runs the program without timing or statistical information). "Building OSBOOT for Simulators," on page 7-4, discusses how to build the **osboot** module for simulators.

Figure 2-1. OSBOOT/Simulator Model

# OSBOOT/DBG\_CORE Model

In the OSBOOT/DBG\_CORE model shown in Figure 2-2, **osboot** is linked with the MiniMON29K debugger core, **dbg\_core**, to provide an environment to debug, develop, and execute embedded applications on targets based on the 29K Family microprocessors.

Figure 2-2 shows the **osboot** bootstrap module as modified to initialize the **dbg\_core** message system and to install the trap handlers provided by **dbg\_core**. After the completion of the bootstrap process, the bootstrap module transfers control temporarily to **dbg\_core** to initialize the debug core by calling the **dbg\_control**() function inside **dbg\_core**.

The HIF kernel of **osboot** is invoked when the call to the **dbg\_control**() function returns control to **osboot**. The **dbg\_control**() function returns the application program information in general purpose registers **gr96** through **gr103**. The HIF kernel uses the return values and prepares an operating environment for the application program.

As shown in Figure 2-2, the HIF kernel performs the I/O operations requested by the application program using the **dbg\_core** message system. It sends a UDI-compliant MiniMON29K message to the MiniMON29K target interface process, **montip**, over a communication interface (such as a serial interface or shared memory). The message is received by **montip** and is processed on an intelligent host. **montip** sends a MiniMON29K message back to the HIF kernel that contains the results of the I/O operation. Refer to the "HIF Run-Time Services" chapter for a more detailed explanation.

In this model (shown in Figure 2-2), the **osboot** and **dbg\_core** modules reside in the ROM units of the target. The program to be tested and debugged is downloaded to the RAM units of the target. To test and debug an application program in this manner requires that the target hardware meet the following minimum requirements:

- There must be a communication channel between the **montip** host and the target. A PC-hosted **montip** supports both serial and parallel interfaces. A UNIX workstation-hosted **montip** supports only serial interfaces.

- The ROM unit of the target must have at least 64 Kbyte of memory.

- The RAM units of the target must have at least 16 Kbyte of memory.

"Building OSBOOT/DBG\_CORE for Hardware Platforms" on page 7-8 describes how to build the OSBOOT/DBG\_CORE model.

Figure 2-2. OSBOOT/DBG\_CORE Model

## **Stand-Alone OSBOOT/Application Model**

In the Stand-Alone OSBOOT/Application Model shown in Figure 2-3, the application program is linked with **osboot** and executed from the ROM memory space on the target system. Program information such as entry point, stack requirements, and execution mode must be provided at compile time. The HIF kernel requires this information to establish an operating environment for the application. In this model, the HIF kernel uses its own communications drivers or those provided by the application program to perform the I/O operations. The shaded boxes shown in Figure 2-3 represent the modules specific to the stand-alone **osboot** software.

This model is usually used in the final stages of testing, when the target hardware and the application software are fully debugged and ready to be released.

Figure 2-3. Stand-Alone OSBOOT/Application Model

## Stand-Alone OSBOOT/DBG\_CORE/Application Model

The Stand-Alone OSBOOT/DBG\_CORE/Application Model (shown in Figure 2-4) provides the same functionality included in the Stand-Alone OSBOOT/Application Model (described previously), with the addition of the debugging and testing capabilities provided by the MiniMON29K software's **dbg\_core** module.

Figure 2-4. Stand-Alone OSBOOT/DBG\_CORE/Application Model

In this model, the application program is linked with the **osboot/dbg\_core** module and executed from ROM memory space on the target hardware. As shown in Figure 2-4, the HIF kernel performs the I/O operations requested by the application program using the **dbg\_core** message system. It sends a UDI-compliant MiniMON29K message to the MiniMON29K target interface process, **montip**, over a communication interface (such as a serial interface, or shared memory). The message is received by **montip** and is processed on an intelligent host. **montip** sends a MiniMON29K message that contains the results of the I/O operation back to the HIF kernel. Refer to the "HIF Run-Time Services" chapter for a more detailed explanation.

#

# OSBOOT Directory and File Organization

The complete **osboot** source code is provided for educational and customization purposes. However, porting **osboot** to new targets often only requires that changes be made to the linker command file – no changes need to be made to source files.

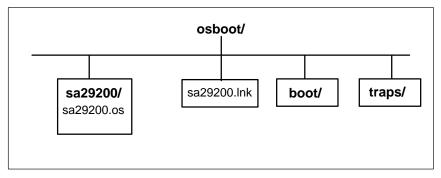

The sources of **osboot** are located in the **29k\src\osboot** directory of the AMD tree structure. This is the top-level directory of the **osboot** sources.-Figure 3-1 on page 3-3 shows the files in the **osboot** directory.

The **29k\src\osboot** directory contains the following make files and MS-DOS batch files:

- UNIX make files:

- makefile.os to build osboot for simulators or to build a relocatable osboot module to link with a stand-alone debugged application

- makefile.mon to build osboot/dbg\_core for debugging applications

- MS-DOS batch files:

- makeosb.bat to build osboot for simulators or to build a relocatable osboot module to link with a debugged stand-alone application

- makemon.bat to build osboot/dbg\_core for debugging applications

The linker command files used by the make files and MS-DOS batch files to produce relocatable objects and absolute images of **osboot** and **osboot/dbg\_core** for different targets are shown in Table 3-1.

The linker command filename extensions have the following meanings:

- .inc files produce relocatable osboot

- .mon files produce a relocatable image of osboot for linking with dbg\_core

- .lnk files produce absolute objects of osboot or osboot/dbg\_core

The **29k\src\osboot** directory contains two subdirectories, **boot** and **traps**, which are explained in the sections starting on pages 3-4 and 3-6, respectively.

| Target Name                                                   | Linker Command File   |              |                                    |

|---------------------------------------------------------------|-----------------------|--------------|------------------------------------|

|                                                               | Relocatable<br>osboot | Absolute     | Relocatable<br>osboot–<br>dbg_core |

| AMD's EB29030                                                 | eb29030.inc           | eb29030.lnk  | eb29030.mon                        |

| AMD's EB29K                                                   | eb29k.inc             | eb29k.lnk    | eb29k.mon                          |

| AMD's EZ030                                                   | ez030.inc             | ez030.1nk    | ez030.mon                          |

| Laser29K-030 board                                            | la29030.inc           | la29030.lnk  | la29030.mon                        |

| Laser29K-200 board                                            | la29200.inc           | la29200.lnk  | la29200.mon                        |

| YARC's ATM sprinter                                           | lcb29k.inc            | lcb29k.lnk   | lcb29k.mon                         |

| Netrom                                                        | netrom.inc            | netrom.lnk   | netrom.mon                         |

| AMD's PCEB29K                                                 | pceb.inc              | pceb.lnk     | pceb.mon                           |

| AMD's SA29030                                                 | sa29030.inc           | sa29030.lnk  | sa29030.mon                        |

| AMD's SA29200                                                 | sa29200.inc           | sa29200.lnk  | sa29200.mon                        |

| AMD's SA29205                                                 | sa29200.inc           | sa29200.lnk  | sa29200.mon                        |

| AMD's SE29240                                                 | sa29240.inc           | sa29240.lnk  | sa29240.mon                        |

| AMD's SE29040                                                 | se29040.inc           | se29040.lnk  | se29040.mon                        |

| STEP's STEB29K                                                | steb.inc              | steb.lnk     | steb.mon                           |

| YARC's Rev 8                                                  | yarcrev8.inc          | yarcrev8.lnk | yarcrev8.mon                       |

| Instruction Set Simulator                                     | sim.inc               | sim00x.lnk   |                                    |

| ( <b>isstip</b> ) or Architectural Simulator ( <b>sim29</b> ) | sim245.inc            | sim03x.lnk   |                                    |

|                                                               |                       | sim050.lnk   |                                    |

|                                                               |                       | sim20x.lnk   |                                    |

|                                                               |                       | sim24x.lnk   |                                    |

Table 3-1. OSBOOT Linker Command Files

**NOTE:** Some of these boards are no longer available commercially, but are still in use. Note also that the names of some boards' linker command files do not correspond directly to the board's name.

Directory and File Organization

| traps/      | tr_mdv.s<br>tr_pvspr.s<br>tr_sqrt.s<br>tr_decl.h<br>dmul.s<br>frdmul.s<br>fpeinit.c<br>uatrap.s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tr          | makefile tr_class.s<br>makepc.bat tr_cnvt.s<br>tr_cand.s<br>tr_dand.s<br>tr_dind.s<br>tr_dind.s<br>tr_fadd.s<br>tr_fadd.s<br>tr_fanul.s<br>tr_fanul.s<br>tr_fanul.s<br>tr_fanul.s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| nom         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | eb29K.mon<br>eb29K.mon<br>k la2930.mon<br>la29200.mon<br>k promice.mon<br>pceb.mon<br>k sa29200.mon<br>k sa29030.mon<br>k sa29030.mon<br>tru.mon<br>tru.mon<br>tru.mon<br>trud16.mon<br>trud16.mon<br>trud16.mon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| eb29030.Ink | eb29k.ink<br>e2030.ink<br>la29200.ink<br>la29200.ink<br>lcb29k.ink<br>promice.ink<br>sa29200.ink<br>sa29200.ink<br>sa29240.ink<br>steb.ink<br>tru.ink<br>tru.ink<br>tru.ink<br>sim00x.ink<br>sim00x.ink<br>sim00x.ink<br>sim00x.ink<br>sim00x.ink<br>sim00x.ink<br>sim00x.ink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| makefile.os | makenle.mon<br>makeosb.bat<br>makeosb.bat<br>eb29030.inc<br>eb29k.inc<br>eb29k.inc<br>la29200.inc<br>la29200.inc<br>la29200.inc<br>pceb.inc<br>promice.inc<br>sa29240.inc<br>sa29240.inc<br>sa29240.inc<br>sa29240.inc<br>sa29240.inc<br>steb.inc<br>tru.inc<br>tru.inc<br>tru.inc<br>tru.inc<br>steb.inc<br>steb.inc<br>tru.inc<br>tru.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb.inc<br>steb |

|             | equates.ah<br>hif.ah<br>hif.ah<br>hif.ah<br>macros.ah<br>register.ah<br>register.ah<br>scc200.ah<br>scc200.ah<br>scc200.ah<br>stats.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah<br>traps.ah                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| boot/       | sa200hw.s<br>scc200.s<br>scc8530.s<br>sec040hw.s<br>sim.s<br>sim.a<br>sim245.s<br>sim245.s<br>sim245.s<br>sim245.s<br>sim245.s<br>startup.s<br>startup.s<br>tlbtraps.s<br>uratp.s<br>vrev8hw.s<br>date.h<br>prlinfo.h<br>stats.h<br>symbl.h<br>vectors.h                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | autils.s<br>coldstrt.s<br>eb030hws<br>eb29khws<br>ecoldstrt.s<br>ecoldstrt.s<br>eb030hws<br>heapbase.s<br>hif.s<br>hif.s<br>hif.s<br>hosthif.s<br>kio.s<br>kio.s<br>kio.s<br>la030hws<br>la200hws<br>p_icehws<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s<br>procinit.s                                                                                                       |

Figure 3-1. OSBOOT Directory and File Organization

### The boot Subdirectory

The **boot** subdirectory contains the source files that implement the bootstrap module and the HIF kernel of **osboot**.

The filename extensions of the source files in the **29k/src/osboot/boot** directory are explained below:

- .s indicates assembly language functions

- .ah indicates assembler header files

- .c indicates C functions

- .h indicates C header files

Table 3-2 lists the source files in the **boot** subdirectory and the function(s) that they implement.

| Source<br>Filename | Function Name(s)                                                                                                                                       |  |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| startup.s          | os_startup                                                                                                                                             |  |

| sim.s, sim245.s    | os_coldstart,os_raminit,os_memset                                                                                                                      |  |

| coldstrt.s         | os_coldstart,os_raminit                                                                                                                                |  |

| procinit.s         | os_procinit,os_am29000_init,os_am29005_init<br>os_am29050_init,os_am29030_init,<br>os_am29035_init,os_am29200_init,<br>os_am29205_init,os_am29240_init |  |

| init24x.c          | os_am2924x_init                                                                                                                                        |  |

| memory.s           | os_sizememory,os_memset                                                                                                                                |  |

| sizemem.c          | os_sizemem29k                                                                                                                                          |  |

| sysinit.s          | os_sysinit                                                                                                                                             |  |

| gentraps.s         | os_warn_mm_trap,os_unexpected_trap,<br>os_illegal_op_trap,os_trace_trap                                                                                |  |

| simtraps.s         | os_warn_mm_trap,os_raminit,os_memset,<br>os_illegal_op_trap,os_unexpected_trap,<br>os_trace_traphif_hosthif                                            |  |

| uatrap.s           | os_ua_trap                                                                                                                                             |  |

Table 3-2. OSBOOT Source Files under boot Subdirectory

| Source<br>Filename | Function Name(s)                                                         |  |  |

|--------------------|--------------------------------------------------------------------------|--|--|

| tlbtraps.s         | os_uiTLBmiss_trap,os_udTLBmiss_trap                                      |  |  |

| tlb24x.s           | os_uiTLBmiss24x_trap,os_udTLBmiss24x_trap                                |  |  |

| register.s         | defines the register mnemonics used                                      |  |  |

| hif.s              | hif_startup,hif_flushTLB,hif_reboot,<br>hif_spillhandler,hif_fillhandler |  |  |

| hifserv.s          | hif_timer_trap,hif_spill_trap,hif_fill_trap,<br>hif_kernel_trap          |  |  |

| hosthif.s          | hif_hosthif                                                              |  |  |

| msgio.s            | hif_hosthif (uses <b>dbg_core</b> message system)                        |  |  |

| eb030hw.s          | os_initcomm for EB29030 card                                             |  |  |

| ez030hw.s          | os_initcomm for EZ030 card                                               |  |  |

| eb29khw.s          | os_initcomm for EB29K card                                               |  |  |

| la030hw.s          | os_initcomm for Laser29K-030 board                                       |  |  |

| la200hw.s          | os_initcomm for Laser29K-200 board                                       |  |  |

| lcb29khw.s         | os_initcomm for YARC ATM Sprinter card                                   |  |  |

| pcebhw.s           | os_initcomm for PCEB29K card                                             |  |  |

| sa030hw.s          | os_initcomm for SA29030 board                                            |  |  |

| sa200hw.s          | os_initcomm for SA29200, SE29240, and SA29205 boards                     |  |  |

| se040hw.s          | _ os_initcomm for SE29040 board                                          |  |  |

| stebhw.s           | os_initcomm for STEB board                                               |  |  |

| yrev8hw.s          | os_initcomm for YARC Rev 8 card                                          |  |  |

| kio.s              | kread,kwrite                                                             |  |  |

| scc200.s           | scc200_init,scc200_putchar,scc200_getchar                                |  |  |

| scc8530.s          | scc8530_init,scc8530_putchar,scc8530_getchar,<br>scc8530_intr            |  |  |

## The traps Subdirectory

The **traps** subdirectory contains the source files that implement the trap handlers for arithmetic operations which the processor hardware does not support directly. It also contains the sources for the Protection Violation trap handler, which are used to access the virtual special-purpose registers.

The following files are also included in the **traps** subdirectory to build a library of trap routines:

- UNIX make file: makefile

- MS-DOS batch file: makepc.bat

The bootstrap module of **osboot** is linked with the trap routine library. The necessary trap handlers are installed during the bootstrap process.

The trap handler source files and floating-point trap routine(s) are listed in Table 3-3. The filename extensions are explained below:

- .s indicates assembly language functions

- .h indicates assembler header files

| Files      | Routines                                                                                               |  |

|------------|--------------------------------------------------------------------------------------------------------|--|

| fpeinit.c  | Floating-point emulation handlers                                                                      |  |

| tr_class.s | CLASS instruction emulation routine                                                                    |  |

| tr_cnvt.s  | CONVERT instruction emulation routine                                                                  |  |

| tr_comp.s  | FEQ, FGE, FGT, DEQ, DGE and DGT instruction emulation routines                                         |  |

| tr_dadd.s  | DADD and DSUB instruction emulation routines                                                           |  |

| tr_ddiv.s  | DDIV instruction emulation routines                                                                    |  |

| tr_div4.s  | DIVIDE and DIVIDU instruction emulation<br>routines using Am29240 <sup>™</sup> processor INTE register |  |

| tr_dmul.s  | DMUL instruction emulation routines using 32x32 bit multiplier                                         |  |

| tr_drnd.s  | Double-precision round/range check routines                                                            |  |

| tr_excp.s  | Floating-point exception trap routine                                                                  |  |

| tr_fadd.s  | FADD and FSUB instruction emulation                                                                    |  |

| tr_fdiv.s  | FDIV instruction emulation routine                                                                     |  |

| tr_fdmul.s | FDMUL instruction emulation routine                                                                    |  |

| tr_fmul.s  | FMUL instruction emulation routine                                                                     |  |

| tr_frnd.s  | Single-precision round/range check routine                                                             |  |

| tr_mldv.s  | MULTIPLY, MULTIPLU, MULTM, MULTMU, DIVIDE and DIVIDU instruction emulation routines                    |  |

| tr_pvspr.s | Protection violation trap handler,os_29kpv_trap                                                        |  |

| tr_sqrt.s  | SQRT instruction emulation                                                                             |  |

| uatrap.s   | Unaligned access trap handler                                                                          |  |

Table 3-3. Arithmetic Trap Handler Source Files

**NOTE:** The register definitions of the mnemonics used in the files listed above are in **register.s** and **register.ah** files in the **boot** subdirectory.

# Chapter 4

# **OSBOOT Bootstrap Module**

When the target system is powered on (RESET), the processor begins to fetch and execute instructions from offset 0x0 in ROM space or instruction space. These instructions initialize the processor and the external target system to a defined state. This process of bringing up the system from RESET to a defined state is called the *bootstrap process* or the *cold start* process. The tasks performed during the bootstrap process are implemented in the **osboot** bootstrap module.

Figure 4-1 illustrates in a left-to-right sequence the tasks performed by the **osboot** bootstrap module. The implementation and the associated file(s) of each task are described in the following sections, as listed in Figure 4-1.

Figure 4-1. OSBOOT Bootstrap Module

## **OSBOOT Global Register Usage**

Table 4-1 shows the registers used by **osboot** to implement the floating-point emulation routines and the HIF kernel services. The files **register.s** and **register.ah** define the symbolic register names and their associated physical processor registers. The **register.s** file, when assembled and linked with other **osboot** files, provides a global linkage to the registers listed in Table 4-1. The **register.ah** file contains external references to each of the registers defined in the **register.s** file, and is included in **osboot** source files containing assembler programs.

| Register | Symbols Used    | Description                                  |

|----------|-----------------|----------------------------------------------|

| gr64     | it0, TempReg0   | Interrupt or trap handler temporary register |

| gr65     | it1, TempReg1   | Interrupt or trap handler temporary register |

| gr66     | it2, TempReg2   | Interrupt or trap handler temporary register |

| gr67     | it3, TempReg3   | Interrupt or trap handler temporary register |

| gr68     | kt0, TempReg4   | Kernel temporary register                    |

| gr69     | kt1, TempReg5   | Kernel temporary register                    |

| gr70     | kt2, TempReg6   | Kernel temporary register                    |

| gr71     | kt3, TempReg7   | Kernel temporary register                    |

| gr72     | kt4, TempReg8   | Kernel temporary register                    |

| gr73     | kt5, TempReg9   | Kernel temporary register                    |

| gr74     | kt6, TempReg10  | Kernel temporary register                    |

| gr75     | kt7, TempReg11  | Kernel temporary register                    |

| gr76     | kt8, TempReg12  | Kernel temporary register                    |

| gr77     | kt9, TempReg13  | Kernel temporary register                    |

| gr78     | kt10, TempReg14 | Kernel temporary register                    |

| gr79     | kt11, TempReg15 | Kernel temporary register                    |

| gr89     | TimerExt        | Timer extension register                     |

| gr90     | SpillAddrReg    | Spill trap handler address                   |

#### Table 4-1. Register Definitions

| Register | Symbols Used | Description                                 |

|----------|--------------|---------------------------------------------|

| gr91     | FillAddrReg  | Fill trap handler address                   |

| gr92     | FPStat3      | Floating-point trap handler static register |

| gr93     | FPStat2      | Floating-point trap handler static register |

| gr94     | FPStat1      | Floating-point trap handler static register |

| gr95     | FPStat0      | Floating-point trap handler static register |

**NOTE:** Please refer to the comments in the **register.ah** file in the **29k/src/osboot/boot** directory for further information on register usage.

## **OS Start-Up and WARN Trap Handler**

#### File

startup.s

The file **startup.s** implements the **osboot** start-up function that takes control of the processor on RESET. It also contains the processor WARN trap handler, which is also the Monitor Mode trap handler for the Am29050<sup>™</sup> microprocessor. The functions implemented in the **startup.s** file are contained in a single text section called Reset. The code below shows the contents of the Reset text section. This section must be loaded and ordered at offset 0x0 in the ROM address space or in the instruction/data memory in the linker command file.

#### Functions

\_\_os\_startup, address16

#### **External Functions**

\_\_os\_coldstart, \_\_os\_warn\_mm\_trap

#### **Reset Text Section**

| .extern     | os_coldstart    |

|-------------|-----------------|

| .extern     | os_warn_mm_trap |

| .sect       | Reset, text     |

| .use        | Reset           |

| .global     | os_startup      |

| os_startup: |                 |

| jmp         | os_coldstart    |

| nop         |                 |

| nop         |                 |

| nop         |                 |

| address16:  |                 |

| jmp         | os_warn_mm_trap |

| nop         |                 |

| nop         |                 |