# **Intel<sup>®</sup> Ethernet Switch FM5000/FM6000**

1 Gb/2.5 Gb/10 Gb/40 Gb Ethernet (GbE) L2/L3/L4 Chip

**Datasheet**

**Networking Division (ND)**

# **Revision History**

| Revision | Date              | Comments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

|----------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3.4      | July 24, 2017     | General updates, including:  • Updated Table 11-2, "Pin List Ordered by Name" to remove reference to DIODE2_IN and DIODE2_OUT pins (i.e. pins T39 and T40 are now correctly labeled as "Reserved".                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 3.3      | November 10, 2014 | <ul> <li>Section 1.1, "Part Numbering" — Revised description of package type to include FCBGA.</li> <li>Table 1-2, "Definition of Terms" — Revised the cut-through latency value for the FlexPipe™ definition.</li> <li>Section 3.3.10, "JTAG Pins" — Updated description of TRST_N pin.</li> <li>Table 6-6, "EPL Standard Modes" — Updated SFI information.</li> <li>Section 9.4, "SerDes Management" — Added notes regarding SBus IDs.</li> </ul>                                                                                                                                                                                          |  |  |

| 3.2      | March 26, 2014    | General updates, including:  • Section 9.9, "LED Controller" — Updated LED controller state decoding in Table 9-7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 3.1      | February 11, 2014 | <ul> <li>General updates, including:         <ul> <li>Section 10.2.2, "Maximum Peak Current" — Revised maximum peak current values for AVDD in Table 10-3, Table 10-4 and Table 10-5.</li> </ul> </li> <li>Section 10.2.3, "Maximum Sustained Power" — Revised maximum sustained power values for AVDD in Table 10-6, Table 10-7 and Table 10-8.</li> <li>Section 11.4, "Pin List Ordered by Name" — Correct pin errors in Table 11-2.</li> </ul>                                                                                                                                                                                            |  |  |

| 3.0      | November 22, 2013 | <ul> <li>General updates, including:</li> <li>Reordered chapter sequence, and renamed Section 2.0, "FM5000/FM6000 Capabilities" to Section 5.0, "Frame Processing".</li> <li>Moved overview information from Section 5.0, "Frame Processing"and added to new Section 2.0, "Architecture Overview".</li> <li>In Section 10.0, "Electrical Specification", updated power sequencing drawing and added REFCLK specification.</li> <li>In Section 11.0, "Mechanical Specification", added legend to ballout diagram.</li> <li>Replaced Figure 11-2, "1677-Ball Package Top/Side View"with new drawing containing notes for call-outs.</li> </ul> |  |  |

| 2.3      | August 7, 2013    | General updates, including:  Revised pin description tables in Section 3.0, "Pin Descriptions".  Revised Table 3-1, "Boot Mode Selection by GPIO[97] Pin Strap Latched at Reset".  Revised Section 10.0, "Electrical Specification".  Revised Section 11.0, "Mechanical Specification".                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 2.2      | June 11, 2013     | Initial release (Intel confidential).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

# **Contents**

| 1.0 | Introd    | luction                                | 11 |

|-----|-----------|----------------------------------------|----|

| 1.1 | Part Nun  | mbering                                | 11 |

| 1.2 | Definitio | ons                                    | 12 |

| 2.0 | Archite   | ecture Overview                        | 15 |

| 2.1 |           | w                                      |    |

|     | 2.1.1     | EPL                                    |    |

|     | 2.1.2     | Ingress Crossbar                       | 16 |

|     | 2.1.3     | Packet Memory                          |    |

|     | 2.1.4     | Frame Handler                          |    |

|     | 2.1.5     | Scheduler                              |    |

|     | 2.1.6     | Egress Crossbar                        | 17 |

|     | 2.1.7     | Egress Modifier                        | 17 |

|     | 2.1.8     | MSB                                    | 17 |

|     | 2.1.9     | PCIe                                   | 17 |

|     | 2.1.10    | Management                             | 17 |

|     | 2.1.11    | Global Resource Tag (GloRT) Definition | 17 |

|     | 2.1.12    | Multi-chip and Intel® Tags             | 18 |

| 3.0 | Pin De    | escriptions                            | 21 |

| 3.1 | Pin Over  | rview                                  | 21 |

| 3.2 | Signal N  | Name Convention                        | 22 |

| 3.3 | Detailed  | Pin Descriptions                       | 22 |

|     | 3.3.1     | Ethernet Port Pins                     |    |

|     | 3.3.2     | PCIe Pins                              | 23 |

|     | 3.3.3     | Power Pins                             | 23 |

|     | 3.3.4     | External Bus Interface Pins            | 24 |

|     | 3.3.5     | DMA Interface Pins                     | 24 |

|     | 3.3.6     | GPIOs and Strapping Pins               | 25 |

|     | 3.3.7     | I <sup>2</sup> C Pins                  | 26 |

|     | 3.3.8     | MDIO Pins                              | 26 |

|     | 3.3.9     | LED Pins                               | 26 |

|     | 3.3.10    | JTAG Pins                              | 26 |

|     | 3.3.11    | Miscellaneous Pins                     | 27 |

| 3.4 | Boot Mo   | ode Selection                          | 27 |

| 4.0 | Power     | Up, Reset and Interrupts               | 29 |

| 4.1 | Power     |                                        | 29 |

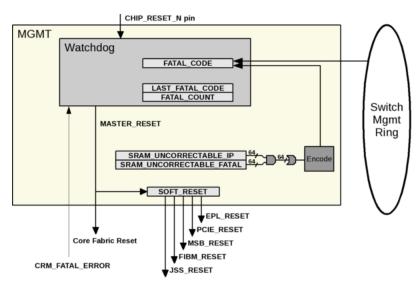

| 4.2 | Reset     |                                        | 29 |

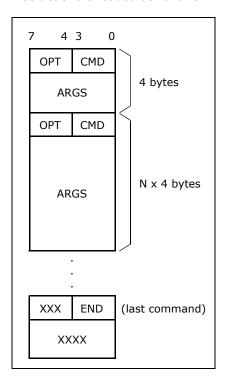

| 4.3 | Serial Bo | oot ROM Format                         | 32 |

| 4.4 |           | ot Controller                          |    |

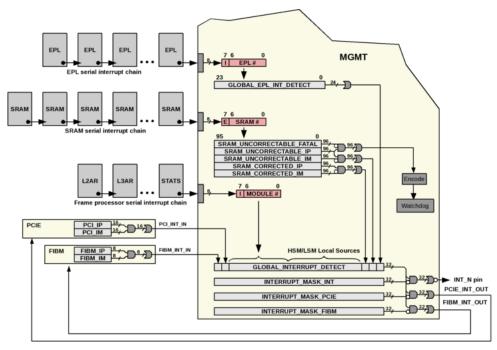

|     | 4.4.1     | Normal Interrupts                      | 36 |

|     | 4.4.2     | Fatal Interrupts                       | 38 |

| 5.0 | Frame     | Processing                             | 39 |

| 5.1 |           | /FM6000 Capabilities                   |    |

| 5.2 |           | ion                                    |    |

| 5.3 | • •       | Processor                              |    |

|     | 5.3.1     | Frame Processing Pipeline              |    |

|     | 5.3.2     | Frame Tail                             |    |

|     | 5.3.3     | Coloring                               | 44 |

| 5.4 | Chip Mana  | gement Logic                    | . 45 |

|-----|------------|---------------------------------|------|

|     | 5.4.1      | I <sup>2</sup> C/CRM Block      | .46  |

|     | 5.4.2      | EBI Block                       | .46  |

|     | 5.4.3      | PCIe Block                      | . 47 |

|     | 5.4.4      | MSB Block                       | .47  |

|     | 5.4.5      | SPICO JTAG Block                | .47  |

|     | 5.4.6      | EPL Manager                     | .47  |

|     | 5.4.7      | Frame Handler Manager           | .47  |

|     | 5.4.8      | L2 Sweeper Manager              | .48  |

|     | 5.4.9      | Congestion Management Monitor   | .48  |

|     | 5.4.10     | Scheduler Manager               | .48  |

| 5.5 | Parsing an | d Association                   | .48  |

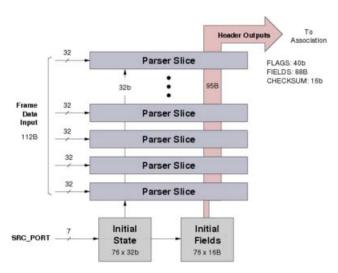

|     | 5.5.1      | Parser                          | .48  |

|     | 5.5.2      | Channel Initialization          | .50  |

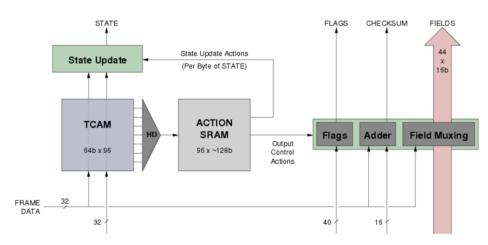

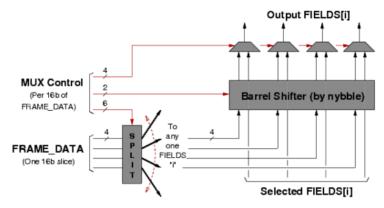

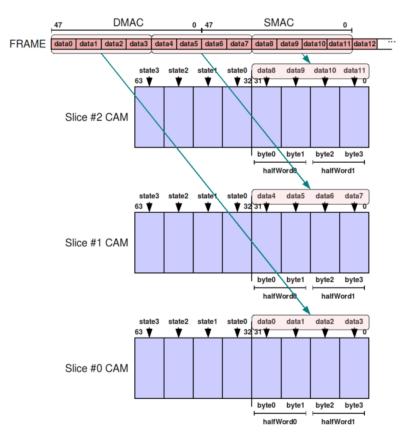

|     | 5.5.3      | Parser Slice                    | .50  |

|     | 5.5.4      | Parser Byte Ordering            | . 52 |

|     | 5.5.5      | Action Encoding                 | .53  |

|     | 5.5.6      | Header Flags                    |      |

|     | 5.5.7      | Association Named Channels      |      |

|     | 5.5.8      | QoS Handling                    | . 57 |

|     | 5.5.9      | Action Flags                    | . 57 |

| 5.6 | Mapper     |                                 |      |

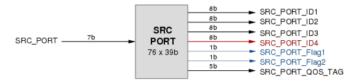

|     | 5.6.1      | SRC PORT TABLE                  |      |

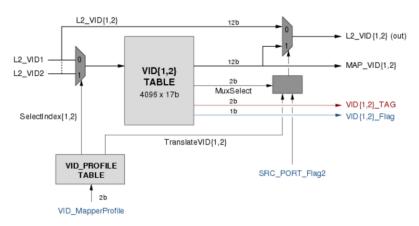

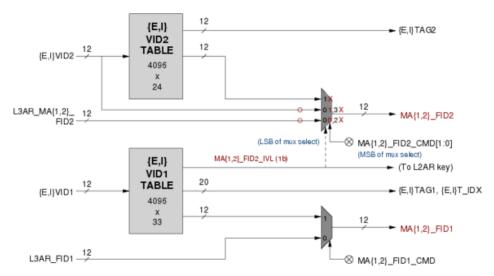

|     | 5.6.2      | VID Tables                      |      |

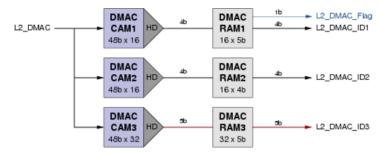

|     | 5.6.3      | L2 CAM/RAM Mapping              |      |

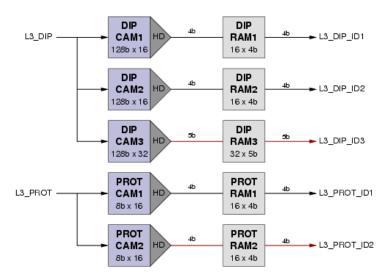

|     | 5.6.4      | L3 CAM/RAM Mapping              |      |

|     | 5.6.5      | L3_LENGTH_COMPARE               |      |

|     | 5.6.6      | L4 Port Mapping                 |      |

|     | 5.6.7      | FFU Initialization              |      |

|     | 5.6.8      | SCENARIO FLAGS                  |      |

|     | 5.6.9      | FFU Action Data                 |      |

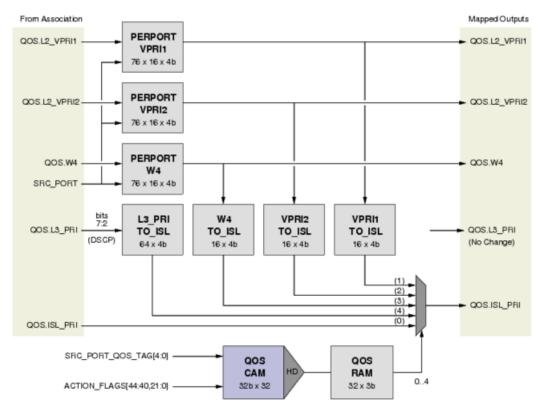

|     | 5.6.10     | QoS Mapping                     |      |

|     | 5.6.11     | Mapper Outputs                  |      |

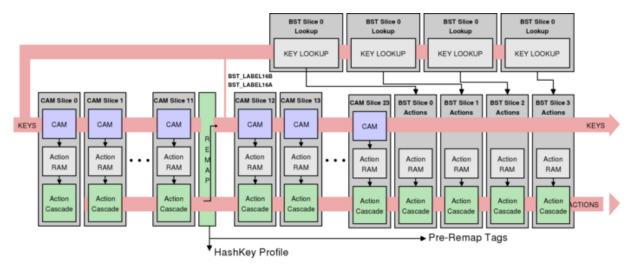

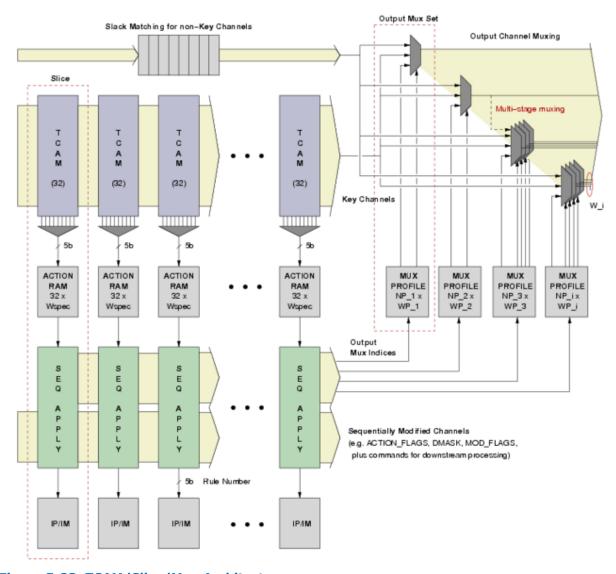

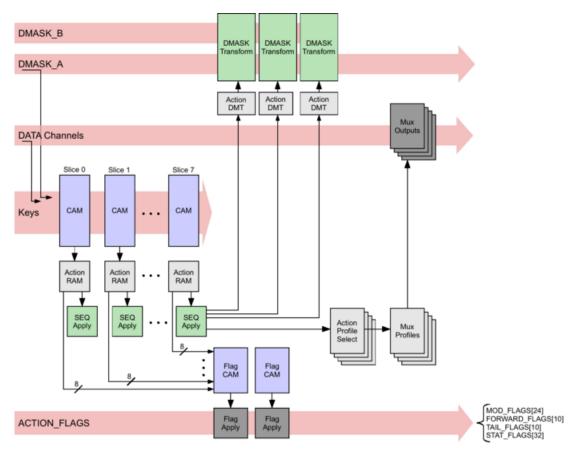

| 5.7 |            | ering and Forwarding Unit (FFU) |      |

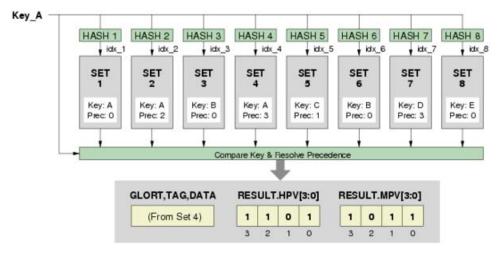

|     | 5.7.1      | Overview                        |      |

|     | 5.7.2      | Keys                            |      |

|     | 5.7.3      | Scenario Key                    |      |

|     | 5.7.4      | Action Channels                 |      |

|     | 5.7.5      | Action Precedence               |      |

|     | 5.7.6      | CAM Slice Chaining              |      |

|     | 5.7.7      | CAM Slice Exclusion Sets        |      |

|     | 5.7.8      | Action Chains                   |      |

|     | 5.7.9      | Egress Actions                  |      |

|     | 5.7.10     | Remap Stage                     |      |

|     | 5.7.11     | Action SRAM                     |      |

|     | 5.7.11     | Route Action                    |      |

|     | 5.7.11.1   | Switch Action                   |      |

|     | 5.7.11.2   | All Other Actions               |      |

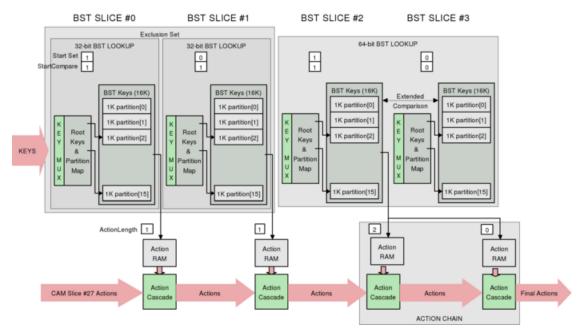

|     | 5.7.11.3   | BST Key Generation and Matching |      |

|     | 5.7.12     | Atomic Modifications            |      |

|     | 5.7.15     | Atomic modifications            | .02  |

#### Contents-FM5000/FM6000 Datasheet

|      | 5.7.14    | FFU Output                       | 83  |

|------|-----------|----------------------------------|-----|

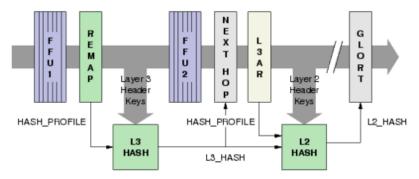

| 5.8  | Frame Ha  | shingshing                       | 84  |

|      | 5.8.1     | L2 and L3 Frame Hashing Overview | 84  |

|      | 5.8.2     | Hash Rotations                   | 85  |

|      | 5.8.3     | Random Hashing                   | 86  |

|      | 5.8.4     | L3 Key Generation                | 86  |

|      | 5.8.5     | L2 Key Generation                | 86  |

|      | 5.8.6     | Symmetrization                   | 87  |

|      | 5.8.7     | Outputs                          | 87  |

| 5.9  | Next Hop  | Table                            | 88  |

|      | 5.9.1     | Overview                         | 88  |

|      | 5.9.2     | Input Interface                  | 88  |

|      | 5.9.3     | Index Calculation and Lookup     | 89  |

|      | 5.9.4     | Narrow Entry Formats             | 89  |

|      | 5.9.5     | Wide Entry Format                | 90  |

|      | 5.9.6     | Outputs                          | 91  |

| 5.10 | L3 Action | Resolution                       | 92  |

|      | 5.10.1    | Overview                         | 92  |

|      | 5.10.2    | Keys                             | 94  |

|      | 5.10.3    | Actions                          | 95  |

|      | 5.10.4    | Outputs                          | 97  |

|      | 5.10.5    | SetFlags                         | 98  |

|      | 5.10.6    | TrapHeader                       | 99  |

|      | 5.10.7    | MuxOutput                        | 100 |

|      | 5.10.7.1  | GloRTs                           | 101 |

|      | 5.10.7.2  | Action Data W8{AD}               | 101 |

|      | 5.10.7.3  | Action Data W8{E,F}              | 102 |

|      | 5.10.7.4  | Action Data W16{AC}              | 102 |

|      | 5.10.7.5  | L2 Lookup Channels               | 104 |

|      | 5.10.7.6  | Layer 2 Hash Rotation            | 106 |

|      | 5.10.7.7  | ALU Operands                     | 106 |

|      | 5.10.7.8  | Policer Indices                  | 107 |

|      | 5.10.7.9  | QoS                              | 109 |

| 5.11 | L2 Lookup | o                                | 110 |

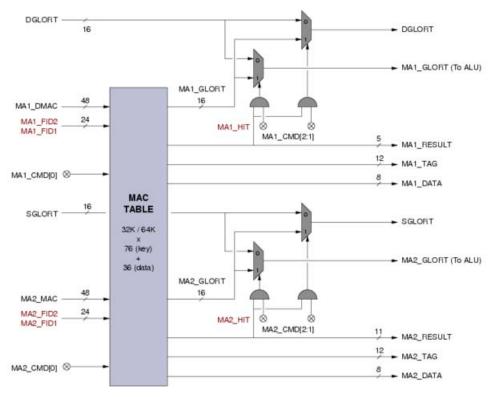

|      | 5.11.1    | Basic Architecture               | 111 |

|      | 5.11.2    | FID Mapping                      | 112 |

|      | 5.11.3    | Performance Versus Capacity      | 113 |

|      | 5.11.4    | Key Precedence                   | 113 |

|      | 5.11.5    | Source Lookup Writeback          | 114 |

|      | 5.11.6    | Output Handling                  | 114 |

|      | 5.11.7    | Command and Result Encodings     | 116 |

|      | 5.11.8    | Direct Management Access         | 117 |

|      | 5.11.9    | Table Sweepers                   | 117 |

|      | 5.11.10   | Table Access Arbitration         | 119 |

| 5.12 | ALU       |                                  | 120 |

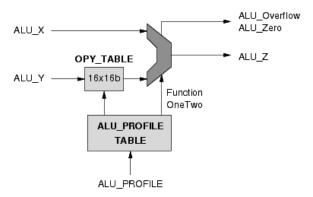

|      | 5.12.1    | Overview                         | 120 |

|      | 5.12.2    | Inputs                           | 121 |

|      | 5.12.3    | Command Encoding                 | 122 |

|      | 5.12.4    | Outputs                          | 123 |

| 5.13 | Policers  |                                  | 124 |

|      | 5.13.1     | Overview                                 | . 124 |

|------|------------|------------------------------------------|-------|

|      | 5.13.2     | Evaluation, Reporting, and Crediting     | . 125 |

|      | 5.13.3     | Entry Formats                            | . 125 |

|      | 5.13.4     | Token Bucket Dynamics                    | . 126 |

|      | 5.13.5     | Sweeper Configuration                    | . 128 |

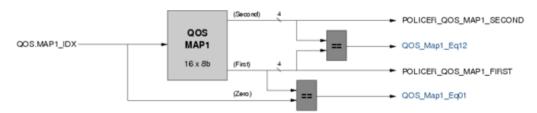

|      | 5.13.6     | QoS Mark-Down Mapping                    | . 128 |

|      | 5.13.7     | Outputs                                  | . 130 |

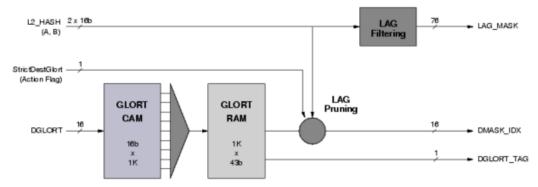

| 5.14 | GloRT Loc  | kup                                      | . 131 |

|      | 5.14.1     | Overview                                 | . 131 |

|      | 5.14.2     | GloRT CAM and Table                      | . 132 |

|      | 5.14.3     | LAG Pruning                              | . 133 |

|      | 5.14.4     | LAG Filtering                            | . 134 |

|      | 5.14.4.1   | Rev A: LAG_PORT_TABLE                    | . 135 |

|      | 5.14.4.2   | Rev B+: LAG_FILTERING_CAM                | . 135 |

|      | 5.14.5     | Outputs                                  | . 137 |

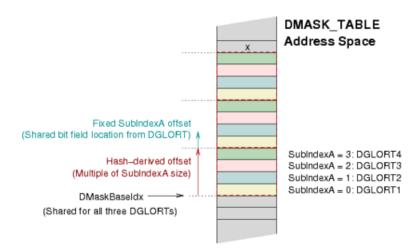

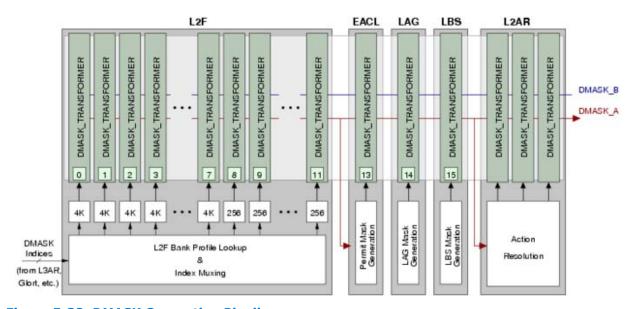

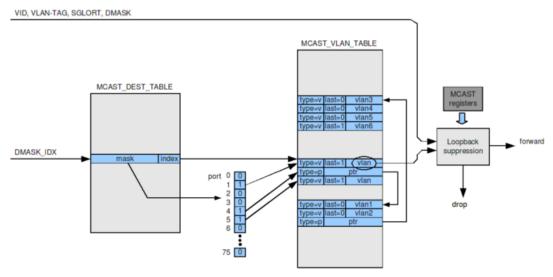

| 5.15 | Destinatio | n Mask Generation                        | . 138 |

|      | 5.15.1     | Overview                                 | . 138 |

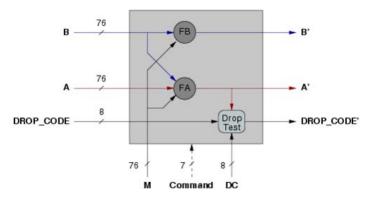

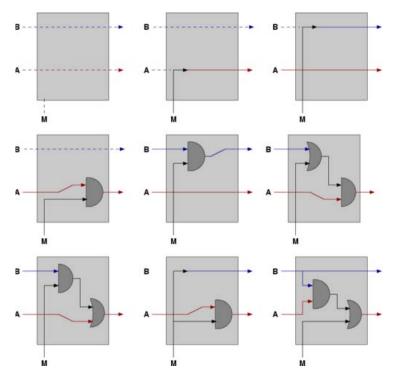

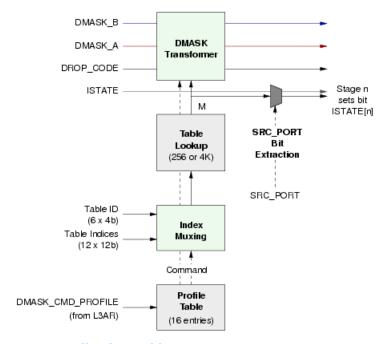

|      | 5.15.2     | DMASK Transformer                        | . 139 |

|      | 5.15.3     | L2 Filtering Tables                      | . 142 |

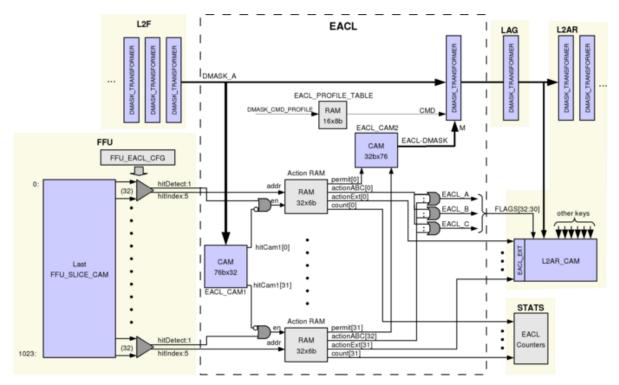

|      | 5.15.4     | EACLs                                    | . 144 |

|      | 5.15.5     | LAG Filtering                            | . 144 |

|      | 5.15.6     | LBS Filtering                            | . 144 |

|      | 5.15.7     | Outputs to L2AR                          | . 144 |

| 5.16 | Egress AC  | Ls                                       | . 145 |

|      | 5.16.1     | Functional Description                   | . 145 |

|      | 5.16.2     | Registers                                | . 148 |

| 5.17 | L2 Action  | Resolution                               | . 148 |

|      | 5.17.1     | Overview                                 | . 149 |

|      | 5.17.2     | Keys                                     | . 150 |

|      | 5.17.3     | EACL Extended Actions                    | . 151 |

|      | 5.17.4     | Actions                                  | . 152 |

|      | 5.17.5     | Action Flags                             | . 154 |

|      | 5.17.6     | TransformDestMask                        | . 155 |

|      | 5.17.7     | Output Flags                             | . 156 |

|      | 5.17.8     | SetMirror                                | . 157 |

|      | 5.17.9     | MuxOutput                                | . 159 |

|      | 5.17.9.1   | MOD_DATA Outputs                         | . 160 |

|      | 5.17.9.2   | Named Forward Channel Outputs            | . 163 |

|      | 5.17.9.3   | QoS                                      | . 164 |

|      | 5.17.9.4   | MAC Table Write-Back                     | . 165 |

|      | 5.17.9.5   | Statistics Index Channels                | . 166 |

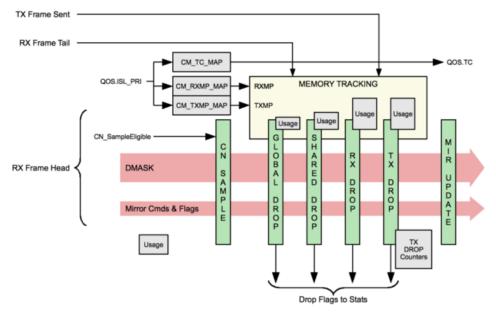

| 5.18 | Congestio  | n Management                             | . 168 |

|      | 5.18.1     | Linkage to the Frame Processing Pipeline | . 169 |

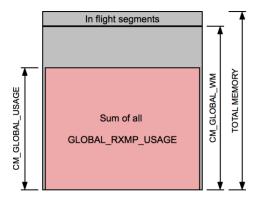

|      | 5.18.2     | Memory Management                        | . 170 |

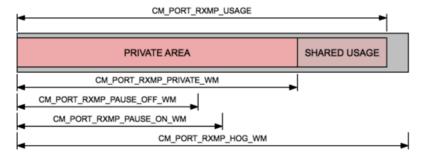

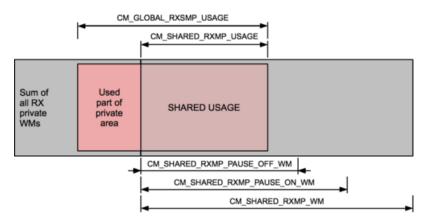

|      | 5.18.3     | Watermarks                               | . 172 |

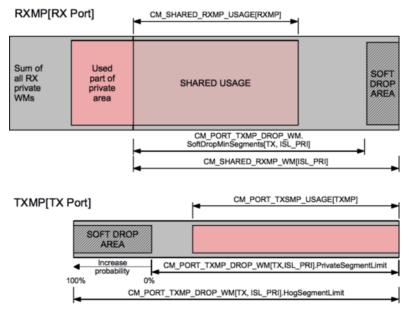

|      | 5.18.4     | Rx Watermark Evaluation                  | . 174 |

|      | 5.18.5     | Tx Watermark Evaluation                  | . 176 |

|      | 5.18.6     | Update Mirror Commands                   | . 179 |

|      | 5.18.7     | Pause Frame Reception                    | . 180 |

|      | 5.18.8     | Pause Frame Generation                   | . 181 |

|      |            |                                          |       |

#### Contents-FM5000/FM6000 Datasheet

|      | 5.18.9     | Pause Pacing                           | 184   |

|------|------------|----------------------------------------|-------|

|      | 5.18.10    | Congestion Notification Frame Sampling | 185   |

|      | 5.18.11    | Interrupt Notification                 | 186   |

| 5.19 | Packet Re  | plication                              | . 187 |

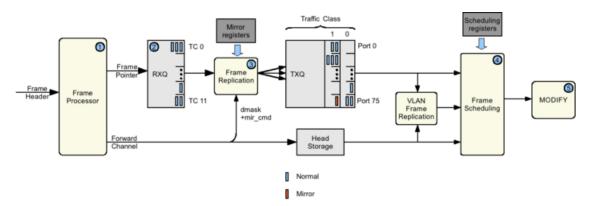

|      | 5.19.1     | Frame Replication                      | 188   |

|      | 5.19.2     | Frame VLAN Replication                 | 188   |

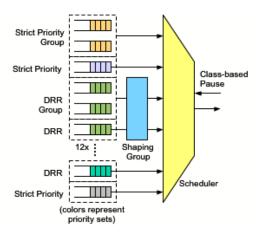

| 5.20 | Scheduler  |                                        | . 191 |

|      | 5.20.1     | Group Eligibility                      | . 192 |

|      | 5.20.2     | Class Selection                        | 193   |

|      | 5.20.3     | Algorithm Notes                        | 193   |

|      | 5.20.4     | Deficit Round-Robin                    | 194   |

|      | 5.20.5     | Bandwidth Shaping                      | 195   |

|      | 5.20.6     | Frame Timeout                          | 196   |

|      | 5.20.7     | Configuration Registers                | 196   |

|      | 5.20.8     | Definition of Terms                    | 197   |

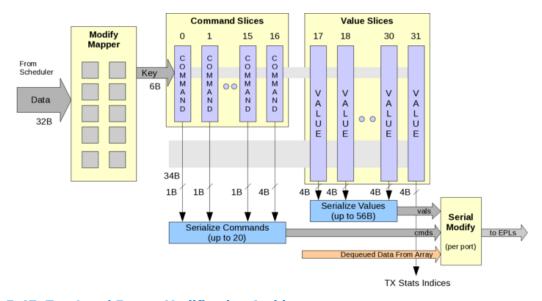

| 5.21 | Egress Mo  | dificationdification                   | . 198 |

|      | 5.21.1     | Basic Properties                       | 198   |

|      | 5.21.2     | Top Level Organization                 | 199   |

|      | 5.21.2.1   | Data from Scheduler                    | . 200 |

|      | 5.21.2.2   | PAUSE Generation                       | . 201 |

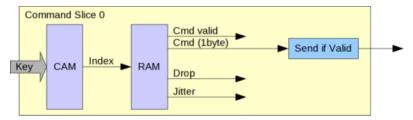

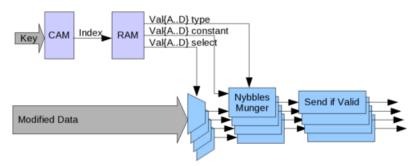

|      | 5.21.3     | Modify Mapper                          | 201   |

|      | 5.21.4     | Modify Slices                          | 203   |

|      | 5.21.4.1   | TCAM Key                               | . 203 |

|      | 5.21.4.2   | Modify Command Slices                  | . 204 |

|      | 5.21.4.3   | Modify Value Slices                    | . 205 |

|      | 5.21.4.4   | Transmit Disposition Flags             | . 207 |

|      | 5.21.4.5   | Statistics Interface                   | 208   |

|      | 5.21.5     | Serial Modify                          | 208   |

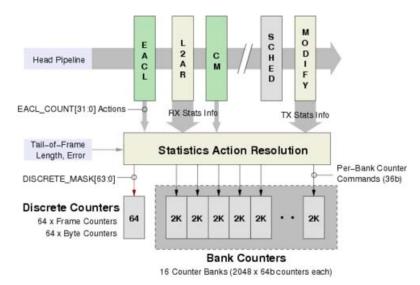

| 5.22 | Statistics |                                        | . 209 |

|      | 5.22.1     | Overview                               | 209   |

|      | 5.22.2     | Action Resolution Structure            | 212   |

|      | 5.22.3     | Per-Port Counters                      | 213   |

|      | 5.22.4     | Discrete Counters                      | 213   |

|      | 5.22.5     | Counter Performance                    | 213   |

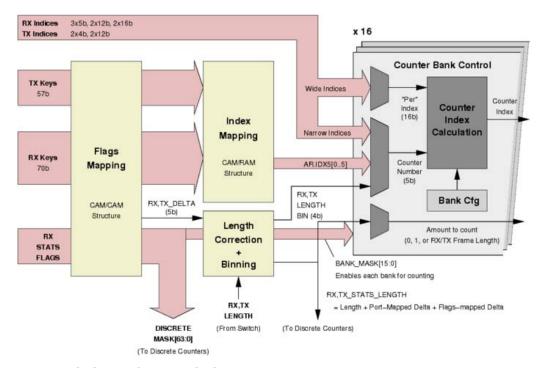

|      | 5.22.6     | Port Mapping                           | 214   |

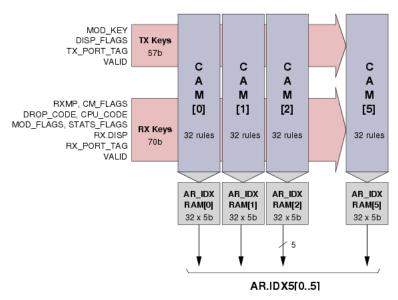

|      | 5.22.7     | Input Keys                             | 214   |

|      | 5.22.8     | Flags Mapping                          | 215   |

|      | 5.22.9     | Index Mapping                          | 216   |

|      | 5.22.10    | Length Correction and Binning          | 217   |

|      | 5.22.11    | Counter Bank Control                   | 218   |

|      | 5.22.12    | Counter Index Generation               | 218   |

|      | 5.22.13    | Bank Index Muxing                      | 220   |

|      | 5.22.13.1  | <del>-</del>                           |       |

|      | 5.22.13.2  | Per-Index Channel Sources              | 221   |

|      | 5.22.14    | Atomicity                              |       |

|      | 5.22.15    | Clearing Counters                      |       |

| 6.0  |            | t Port Logic (EPL)                     |       |

| 6.1  |            |                                        |       |

| 6.2  |            | ing                                    |       |

|      | 6.2.1      | Port Numbering                         |       |

|      |            |                                        |       |

|      | 6.2.2      | Port Mapping Using the Channel                                  | 227 |

|------|------------|-----------------------------------------------------------------|-----|

|      | 6.2.3      | Default Lane Reversal and Polarity Inversion Inside the Package | 228 |

|      | 6.2.4      | EPL Port Pairing                                                | 230 |

| 6.3  | Mode of 0  | Operation                                                       | 231 |

| 6.4  | Reference  | e Clock                                                         | 233 |

| 6.5  | SerDes C   | haracteristics                                                  | 234 |

|      | 6.5.1      | DFE Tuning and Emphasis                                         | 234 |

|      | 6.5.2      | Pattern Generator/Comparator                                    | 234 |

|      | 6.5.3      | Loopbacks                                                       | 235 |

|      | 6.5.4      | Eye Measurement                                                 | 235 |

| 6.6  | Recovere   | d Clocks                                                        | 235 |

| 6.7  | Auto-Neg   | otiation                                                        | 236 |

|      | 6.7.1      | Clause 73                                                       | 236 |

|      | 6.7.2      | Clause 37                                                       | 239 |

|      | 6.7.3      | SGMII                                                           | 241 |

| 6.8  | Physical ( | Coding Sub-layer (PCS)                                          | 243 |

|      | 6.8.1      | 40GBASE-R4                                                      | 243 |

|      | 6.8.2      | 20GBASE-R2                                                      | 244 |

|      | 6.8.3      | 10GBASE-R                                                       | 244 |

|      | 6.8.4      | 10GBASE-X                                                       | 244 |

|      | 6.8.5      | 1000BASE-X Frame Format                                         | 245 |

|      | 6.8.6      | Link Status                                                     | 245 |

|      | 6.8.7      | FSIG                                                            | 245 |

|      | 6.8.8      | IFGs                                                            | 246 |

|      | 6.8.9      | Changing PCS Mode                                               | 247 |

| 6.9  | MAC        |                                                                 | 247 |

|      | 6.9.1      | Preamble and CRC Optional Processing                            | 248 |

|      | 6.9.2      | Packet Generation                                               | 249 |

|      | 6.9.3      | Reception Errors                                                | 250 |

|      | 6.9.4      | Counters                                                        | 251 |

|      | 6.9.5      | Time Stamping for IEEE1588                                      | 252 |

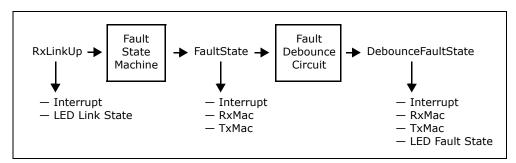

| 6.10 | Status an  | d Interrupts                                                    | 253 |

| 6.11 | Link State | e and Fault Conditions                                          | 253 |

| 7.0  | PCIe In    | iterface                                                        | 257 |

| 7.1  |            |                                                                 |     |

| 7.2  |            |                                                                 |     |

| 7.3  |            | SerDes                                                          |     |

| 7.4  | Reference  |                                                                 | 259 |

| 7.5  | In-Band I  | Reset and Link Down Events                                      |     |

| 7.6  |            | S                                                               |     |

| 7.7  | •          | nagement                                                        |     |

| 7.8  |            | pping                                                           |     |

| 7.9  |            | -bit Addressing                                                 |     |

| 7.10 |            |                                                                 |     |

| ,,_, | 7.10.1     | PCIe Configuration Space                                        |     |

|      | 7.10.2     | PCIe Control Registers                                          |     |

|      | 7.10.2.1   |                                                                 |     |

|      | 7.10.2.2   | 3                                                               |     |

|      | 7.10.2.3   | 3                                                               |     |

|      | 7.10.2.4   | •                                                               |     |

|      |            |                                                                 |     |

#### Contents-FM5000/FM6000 Datasheet

| 7.11 | Packet DM            | A Engine                      | 266 |

|------|----------------------|-------------------------------|-----|

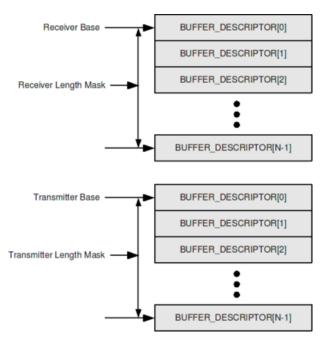

|      | 7.11.1               | Buffer Descriptors            | 267 |

|      | 7.11.1.1             | Status                        | 268 |

|      | 7.11.1.2             | Buffer Length                 | 268 |

|      | 7.11.1.3             | Buffer Address                | 268 |

|      | 7.11.1.4             | F64 Tag                       |     |

|      | 7.11.2               | Packet Processing Overview    |     |

|      | 7.11.3               | Fabric Congestion Management  | 272 |

|      | 7.11.3.1             | PAUSE Detection               | 272 |

|      | 7.11.3.2             | PAUSE Reaction                | 272 |

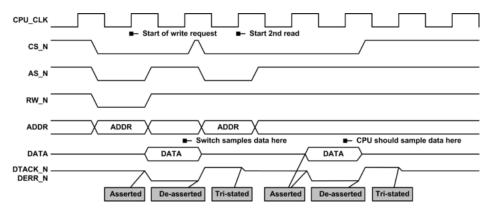

| 8.0  | External             | Bus Interface (EBI)           | 273 |

| 8.1  |                      |                               |     |

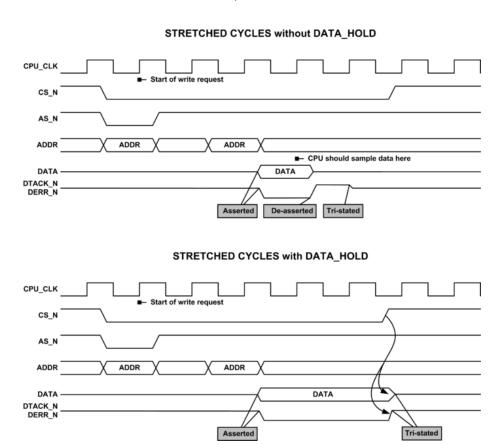

| 8.2  |                      | ]                             |     |

| 0.2  | -                    | Using DATA_HOLD               |     |

| 8.3  |                      | cesses                        |     |

| 8.4  |                      | Big Endian Support            |     |

| 8.5  |                      | e Transfer                    |     |

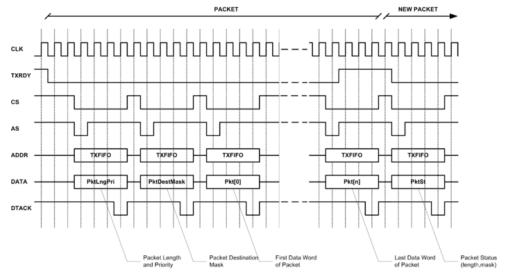

| 0.5  |                      | Packet Transmission via EBI   |     |

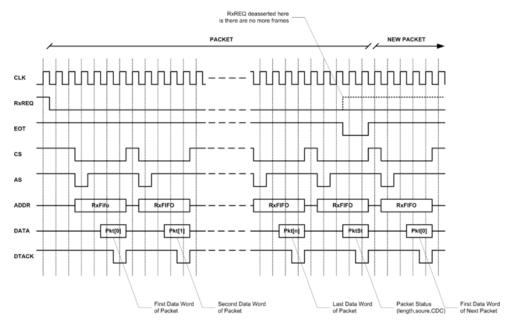

|      |                      | Packet Reception via EBI      |     |

|      |                      | Packet Transfer               |     |

|      | 8.5.3.1              | Little Endian Packet Transfer |     |

|      | 8.5.3.2              | Big Endian Packet Transfer    |     |

| 8.6  |                      | nsfer DMA Timing              |     |

|      |                      | als                           |     |

| 9.0  | •                    |                               |     |

| 9.1  |                      |                               |     |

| 9.2  | •                    |                               |     |

| 9.3  |                      | ate Monitor                   |     |

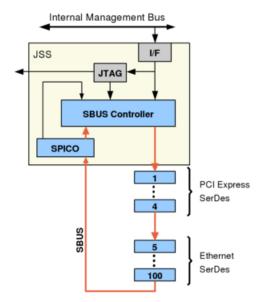

| 9.4  |                      | nagement                      |     |

|      |                      | SPICO Micro-controller        |     |

|      |                      | SerDes Registers              |     |

|      |                      | Device Address to Serdes Map  |     |

| 9.5  |                      | ller                          |     |

| 9.6  |                      | troller                       |     |

| 9.7  |                      | rpose IO (GPIO) Controller    |     |

| 9.8  |                      | nce                           |     |

|      |                      | Overview                      |     |

|      | 9.8.2                | Boot                          |     |

|      |                      | Management                    |     |

| 9.9  |                      | oller                         |     |

| 9.10 |                      | face                          |     |

|      | 9.10.1               | Tap Controller                | 311 |

| 10.0 | Electrica            | I Specification               | 313 |

| 10.1 | Absolute M           | laximum Ratings               | 313 |

| 10.2 | Recommer             | nded Operating Conditions     | 313 |

|      | 10.2.1               | Voltage Scaling               | 314 |

|      | 10.2.2               | Maximum Peak Current          | 314 |

|      | 10.2.3               | Maximum Sustained Power       | 315 |

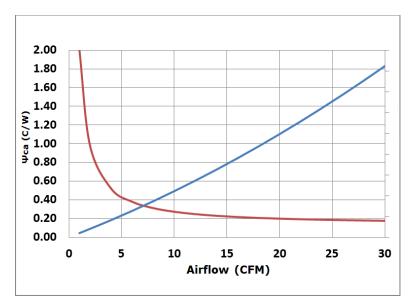

| 10.3 | Thermal Cl           | haracteristics                | 317 |

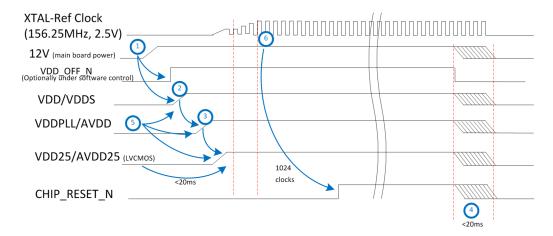

| 10.4 | Power Sup            | ply Sequencing                | 317 |

| 10.5 | REFCLK Specification |                               |     |

#### FM5000/FM6000 Datasheet—Contents

| 10.6  | DC Characteristics of LVCMOS PADs             | 319 |

|-------|-----------------------------------------------|-----|

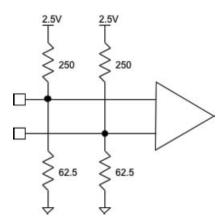

| 10.7  | Ethernet Output Specifications                | 320 |

| 10.8  | Ethernet Input Specifications                 | 320 |

| 10.9  | PCIe Output Specifications                    | 321 |

| 10.10 | PCIe Input Specifications                     | 321 |

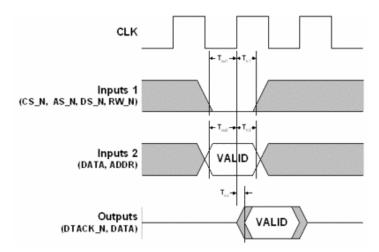

| 10.11 | EBI Interface, General Timing Requirements    | 322 |

| 10.12 | JTAG Interface                                | 322 |

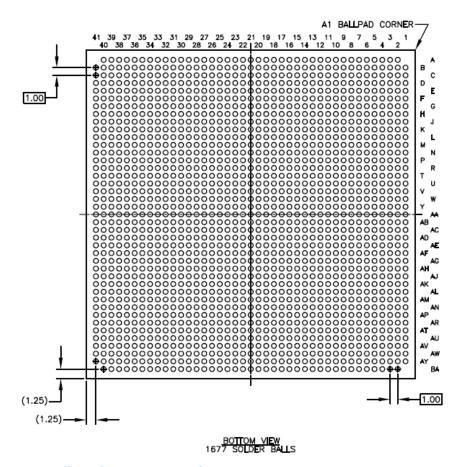

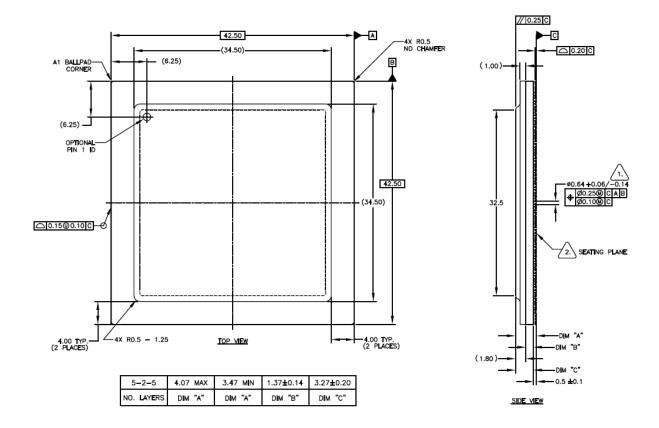

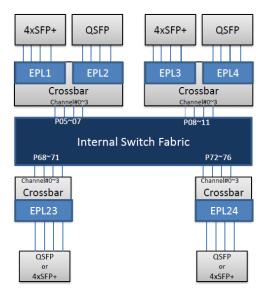

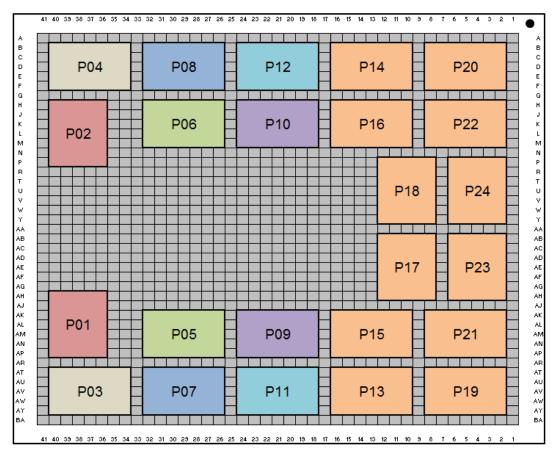

| 11.0  | Mechanical Specification                      | 323 |

| 11.1  | 1677-Ball Package Dimensions                  | 323 |

|       | 1677-Ball Package                             |     |

| 11.3  | Pin List Ordered by Location                  | 326 |

| 11.4  | Pin List Ordered by Name                      | 337 |

| 11.5  | EPL Blocks                                    | 349 |

|       | 11.5.1 FM5224 10 GbE EPL Location Flexibility | 349 |

## 1.0 Introduction

The Intel<sup>®</sup> Ethernet and Switch series consists of the Intel<sup>®</sup> Ethernet Switch FM2000 series L2 switch chip platform, the Intel<sup>®</sup> Ethernet Switch FM4000 series multi-layer switch chip platform and the high-performance Intel<sup>®</sup> Ethernet Switch FM5000/FM6000 Series (FM5000/FM6000) multi-layer switch chip platform. This document provides the following information:

- Functional descriptions

- Frame processing pipeline

- Hardware design

- Pin interface

- Electrical specifications

- · Package mechanical

- Thermal information

**Note:** For software details, see the Intel<sup>®</sup> Ethernet and Switch Family Software API.

## 1.1 Part Numbering

The FM5000/FM6000 provides a range of part numbers as listed in Table 1-1. Each part number is configured with a maximum core bandwidth that puts a limit on the sum of the maximum port bandwidth plus the maximum management bandwidth. The management bandwidth is the portion of the core bandwidth that can be used by Ethernet management ports and/or the CPU interface, and is limited to less than 20 GbE. The ports can be allocated in any manner as long as the maximum port bandwidth is not exceeded.

**Table 1-1** Part Numbering

| Part Number | Max Port<br>Bandwidth | Max SGMII or 1<br>GbE Serdes Ports | Max XAUI Ports | Max 10 GbE<br>Serial Ports | Max 40 GbE Ports |

|-------------|-----------------------|------------------------------------|----------------|----------------------------|------------------|

| FM5224      | 240G                  | 72                                 | 2              | 8                          | 2                |

| FM6324      | 240G                  | 72                                 | 24             | 24                         | 6                |

| FM6348      | 480G                  | 72                                 | 24             | 48                         | 12               |

| FM6364      | 640G                  | 72                                 | 24             | 64                         | 16               |

| FM6724      | 240G                  | 72                                 | 24             | 24                         | 6                |

| FM6764      | 640G                  | 72                                 | 24             | 64                         | 16               |

This document pertains to all variants of the FM5000/FM6000 series, although most references are specific to the 64-port 10 GbE version of the device. All devices are manufactured in a Flip-Chip Ball Grid Array (FCBGA), 1677-ball package.

# 1.2 Definitions

#### **Table 1-2 Definition of Terms**

| Term          | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| {A,B}         | Denotes a bit concatenation of variable A or B where A is most significant bit field and B is least significant bit field.                                                                                                                                                                                                                                                                                                                                                                                                                 |

|               | <b>Note:</b> {0,A} means that 0s are added to the left (most significant bits) to pad to the desired size while {A,0} means padded to the right.                                                                                                                                                                                                                                                                                                                                                                                           |

| Bit Numbering | Bit 0 is the least significant bit throughout the architecture (even if Ethernet standards and specifications suggest otherwise).                                                                                                                                                                                                                                                                                                                                                                                                          |

| Byte          | 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Double Word   | 64 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| EBI           | External Bus Interface — Intel's term for a legacy address/data external bus interface to processor.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F32/F64/F96   | Intel-proprietary inter-switch link tag, which is used to pass relevant management and control information from one Intel Ethernet and Switch Family device to another in a network. Not supported in the FM2000 series.                                                                                                                                                                                                                                                                                                                   |

| FlexPipe™     | The name for the FM5000/FM6000 series high-performance flexible frame processing pipeline that operates at over one billion packets-per-second with less than 400 ns cut-through latency. Microcode can be used to provide flexible pipeline configurations.                                                                                                                                                                                                                                                                               |

| FM2000        | The first generation of the Intel® Ethernet and Switch Family.  The FM2000 is a Layer 2 (L2) 10 GbE switch chip platform that forms the basis for many L2 switch product variants, including the FM2224, FM2212, FM2208, FM2112, FM2104, and FM2103.                                                                                                                                                                                                                                                                                       |

| FM4000        | The second generation of the Intel <sup>®</sup> Ethernet and Switch Family.  The FM4000 is an enhanced multi-layer 10 GbE switch chip platform that forms the basis for new switch product variants, all of which are pin-compatible with their original FM2000 series counterparts. The FM4xxx devices are full-featured L3 routing devices, and contain other enhancements, such as ACL's, congestion management, increased frame memory and more. The FM3xxx devices are similar to the FM4xxx, except that L3 routing is not included. |

| FM5000/FM6000 | The third generation of the Intel® Ethernet and Switch Family.  The FM5000/FM6000 enhances functionality and bandwidth while providing package options that are pin compatible with the FM4000 series. The FM5000/FM6000 L2/L3/L4 devices provide advanced CEE/ DCB features for the Data Center.                                                                                                                                                                                                                                          |

| GloRT         | Intel-proprietary Global Resource Tag, which is used to pass global identification information from one device to another in a network. GloRT is the proper pronunciation, although other uses might appear in the document and have the same meaning. For example, glort, GloRT or GLORT.                                                                                                                                                                                                                                                 |

| Half Word     | 16 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Logging       | Logging refers to a copy of the frame sent to a local CPU for monitoring purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Mirroring     | Mirroring refers to a copy of the frame sent to another port for monitoring purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

#### **Table 1-2 Definition of Terms (Continued)**

| Term                  | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Packet or Frame       | <b>Packet</b> — On a typical computer network, data is transmitted in the form of structured and modest-sized packets. Instead of transmitting arbitrary-length strings of data, structured packets Packet or Frame allow error checking and other relevant processing to occur on smaller easier-to-retransmit data. Packetized data also helps to alleviate traffic jams on the network when multiple nodes are contending for a shared network resource.                                                                                       |

|                       | <b>Frame</b> — While a packet is a small block of data, a Frame is the definition of how packets of data are defined and transported on a specific network. When sending data over a network, both sides of the connection must agree on a common frame format (e.g., when a frame starts, when a frame ends, padding, etc.)                                                                                                                                                                                                                      |

|                       | Combining terms, an Ethernet packet is sent onto an Ethernet interface using an Ethernet frame format.                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                       | This document uses both terms interchangeably.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PCIe Express* (PCIe*) | PCIe Interface to a processor. Compliant to PCIe Gen 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RapidArray            | The name for Intel's single output queued shared memory architecture that is used in the FM2000, FM4000 and FM5000/FM6000 series 10 GbE switch chip platforms.                                                                                                                                                                                                                                                                                                                                                                                    |

| Register Type         | Registers are split into fields of the following types:  RO: Read-Only (This register cannot be programmed by software. Typically reports a status.)  RW: Read-Write (Reading returns the value written.)  CW Clear-on-Write (Writing to the register clears the register.)  CW1: Clear-on-Write-1 (Writing 1b to any bit clears that bit.)  CR: Clear-on-Read (Reading the register clears the register.)  RV: Reserved (For upward compatibility. Always write as 0b, ignore on read.)  WO: Write-Only (The value written cannot be read back.) |

| Segment               | A portion of a packet corresponding to one of the common architecturally-significant storage and processing chunks that has been defined in the architecture. For FM5000/FM6000 devices, a segment is 160 bytes.                                                                                                                                                                                                                                                                                                                                  |

| Trapping              | Trapping refers to special frames that are captured by the switch and redirected to a local CPU for processing.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Word                  | 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| X[0N]                 | Denotes an array with indexes that go from 0 through N, inclusively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| X[N:0] or X[0:N]      | Denotes a bit range within a variable. The bit range [0:N] indicates that bit 0 is the most significant, while bit range [N:0] indicates that the bit 0 is the least significant.                                                                                                                                                                                                                                                                                                                                                                 |

331496-002

NOTE: This page intentionally left blank.

## 2.0 Architecture Overview

## 2.1 Overview

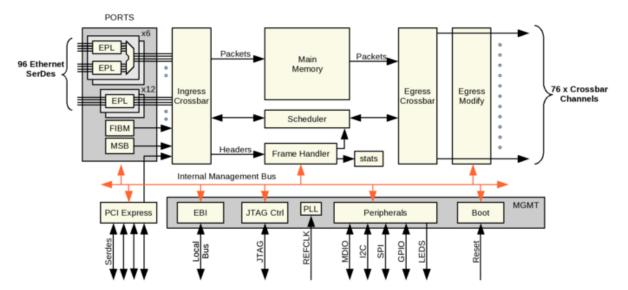

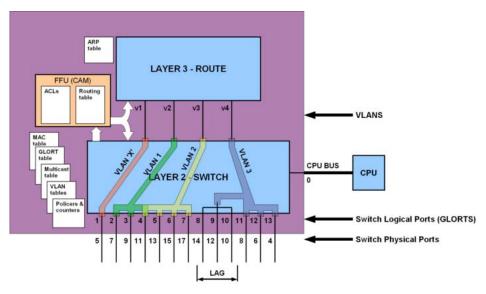

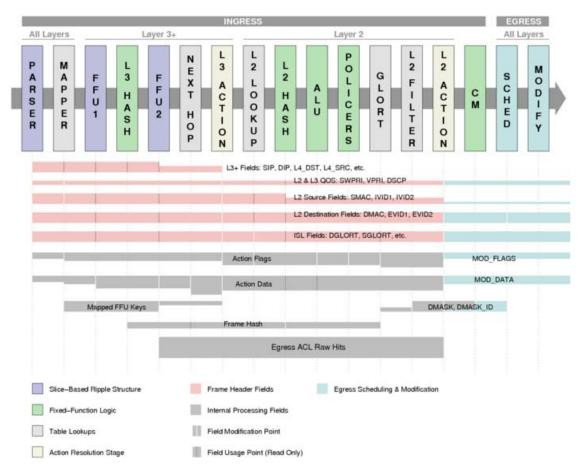

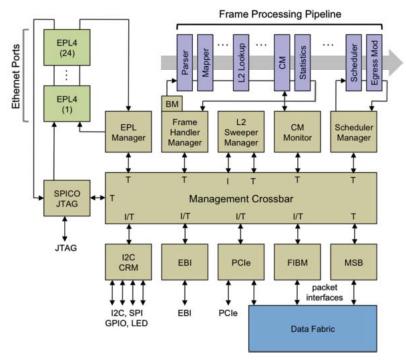

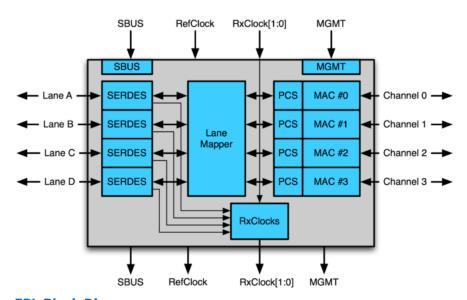

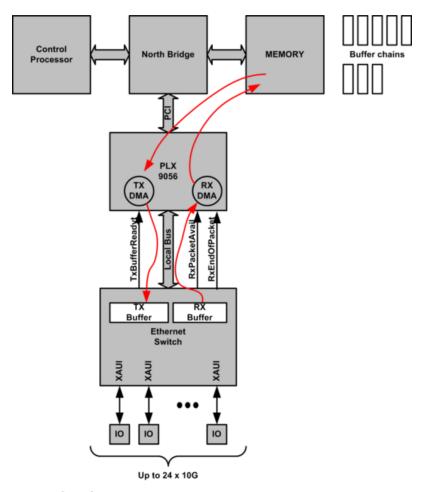

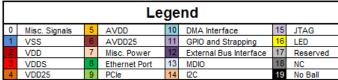

The FM5000/FM6000 main components are shown in Figure 2-1.

Figure 2-1 FM5000/FM6000 Block Diagram

At the switch ingress, the Ethernet Port Logic (EPL) parses incoming packets to extract the packet payload, which gets forwarded to the shared packet memory through a receive crossbar. In the reverse direction, the scheduler forwards packets from the shared packet memory through the transmit crossbar, to the egress modifier. The egress modifier might modify the packet before forwarding it to the EPL along with recomputing the CRC. All packet headers are processed by the frame handler.

#### 2.1.1 EPL

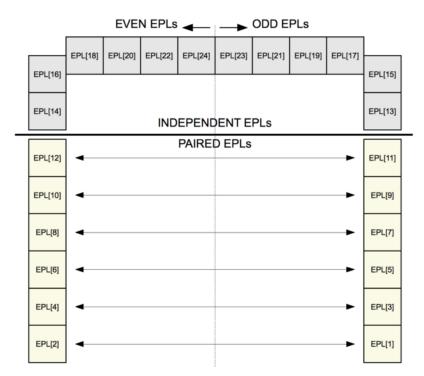

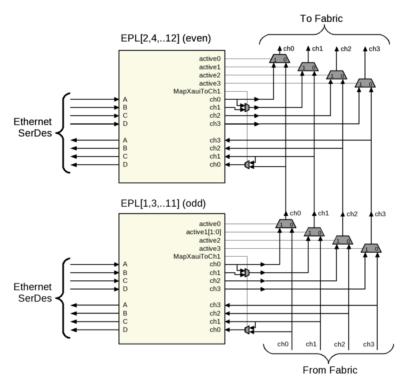

EPL is an interface between the Ethernet SerDes and the internal data structures. It implements PCS, reconciliation layer, and the MAC layer. The EPL also implements PCS-type management, such as fault handling, auto-negotiation, etc. Various SerDes-to-channel mapping combinations are offered to enable support for 1GBASE-X, SGMII, XAUI, 10 GbE serial and 40 GbE MLD. There are 24 EPLs in the switch. Two arrangements are supported. The first 12 EPLs are arranged in pairs, in which each pair shares 40 GbE of bandwidth to the crossbar.

The next 12 EPLs are directly attached to the crossbar, in which each EPL has access to up to 40 GbE worth of bandwidth to the crossbar ( $4 \times 10$  GbE channels).

See Section 6.2 and Section 6.3 for more details concerning the 24 EPLs.

## 2.1.2 Ingress Crossbar

The role of the ingress crossbar is to receive a serial stream of data at 10 GbE and forward it to the main memory as segments. The segment size is 160 bytes. The first 112 bytes of the first segment are passed to the frame handler for packet processing, switching and/or routing decisions.

The ingress and egress crossbars support up to 76 full-duplex channels. Any channel can support a throughput of 10 GbE (four channels are combined together for 40 GbE support) but the total aggregate throughput is limited to 720 GbE.

## 2.1.3 Packet Memory

The main memory stores incoming packets from ingress EPLs and forwards them to egress EPLs upon request from the scheduler. The main memory size is 7.5 MB. Additional memory in other functional blocks brings the total packet and frame header memory to approximately 9.5 MB.

## 2.1.4 Frame Handler

The frame handler makes forwarding decisions based on the frame header received from the EPL. The forwarding information (port mask and modification data) is sent to the scheduler.

## 2.1.5 Scheduler

The scheduler manages free data segments, maintains receive and transmit queues and schedules packets for transmission. The free segments are forwarded as needed to the receive crossbar, which uses them to store incoming packets to the right location in the shared memory fabric. The scheduler keeps the list of the segments sent to each EPL/MSB/IPL and waits for the frame handler forwarding decision before placing the packet at the tail of the proper transmission queue.

The scheduler then applies advanced scheduling algorithms to decide which packet to forward to the EPL/MSB/IPL. It then sends a segment list to the transmit crossbar, which uses those segments to retrieve the packet from memory and forward the payload to the egress modifier.

## 2.1.6 Egress Crossbar

The egress crossbar receives pointers from the scheduler, reads the packets from memory and forwards them to the egress modifier for packet modification.

## 2.1.7 Egress Modifier

The egress modifier executes the instructions received from the scheduler to modify the packets as data gets transmitted. Examples of egress modification includes new DMAC/SMAC/VLAN and VLAN translation as well as adding/removing an MPLS header.

#### 2.1.8 MSB

The MSB unit is an internal port to the switch fabric for EBI attached devices. The MSB receives frames from the EBI and forwards them to the switch or receives frames from the switch and forwards them to the EBI.

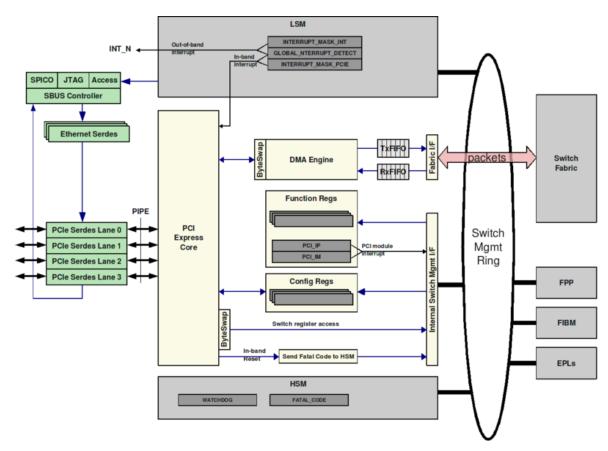

#### 2.1.9 PCIe

The PCIe unit (fixed at internal port 0) is the primary interface for controlling the switch. Also, the PCIe has direct access to the switch fabric enabling packets to flow between the fabric and the host processor through a built-in DMA engine.

## 2.1.10 Management

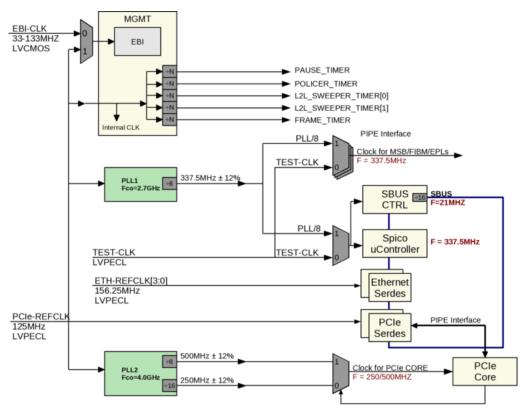

The management system includes many entities: legacy external address/Data Bus Interface (EBI), JTAG controller, peripherals, boot controller and PLL.

## 2.1.11 Global Resource Tag (GloRT) Definition

GloRT is a 16-bit number that can be used to identify a specific port, link aggregation group, multicast group, management frame or any other packet destination in a single or multi-stage fabric.

The source GloRT is generally used to identify the logical source port of the frame as it enters a multistage switch fabric. The destination GloRT is generally the logical destination port or group of ports to where the frame exits the multi-stage fabric. Each FM5000/FM6000 must be configured with the following set of GloRTs.

• **Per-port Source GloRT** — Each time a frame arrives without an Inter-Switch Link (ISL) tag, this source GloRT is associated with the frame. If the frame's source MAC address is learned, this GloRT value is stored in the MAC address table.

• **CPU GIORT** — Each time a frame is trapped, logged or mirrored to the CPU, the top eight bits of the destination GloRT are set to this value. The bottom eight bits are set to a trap code value, chosen by hardware to indicate the reason for sending the frame to the CPU.

In addition, other feature-specific GloRTs can also be created on-the-fly using API commands:

- · Rx mirror GloRT

- Tx mirror GloRT

- Multicast GloRT

- Link aggregation GloRT

- Load balancing group GloRT

The mapping from GloRT to a physical port involves a ternary CAM lookup. This enables the 16-bit GloRT space to be allocated in a fairly arbitrary manner. The only structure required by the mapping function consists of:

- A configurable bit range within link aggregation group GloRTs, used to identify individual physical port members.

- Fixed 8-bit CPU trap code field within the CPU GloRT.

# 2.1.12 Multi-chip and Intel® Tags

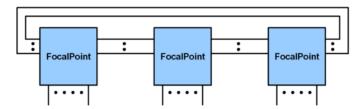

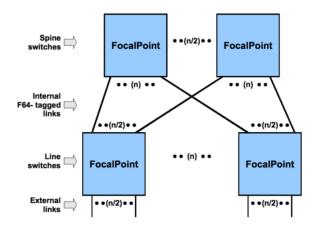

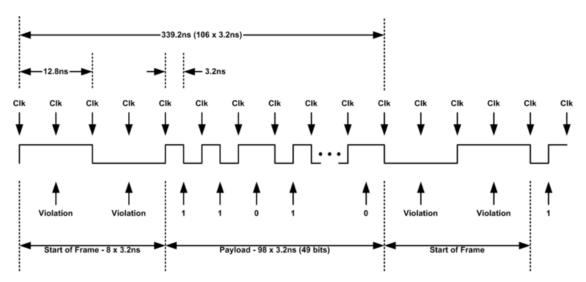

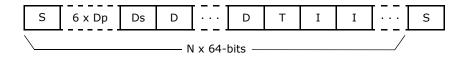

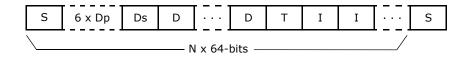

Multiple switches can be aggregated together to create a larger logical switch by connecting them through normal Ethernet ports, and by extending the Ethernet packet format to carry extra information. Intel defines three extra tag formats, F56, F64 and F96, for this purpose:

- The F56 tag is 7 bytes long and replaces the seven bytes of preamble between the SDF symbol and the first byte of the payload.

- This tag is available on 10 GbE and 40 GbE links only.

- The F64 tag is 7 bytes long and is inserted at byte 12 (right after SMAC).

- This tag replaces the VLAN tag.

- The F96 tag is 12 bytes long and is inserted at byte 12 (right after SMAC).

- This tag replaces the VLAN tag.

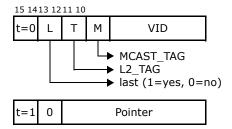

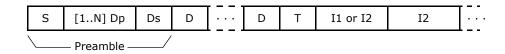

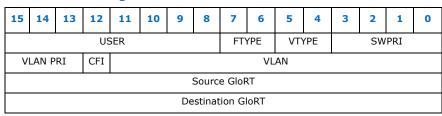

Table 2-1 shows the F56 tag (first byte is preamble SDF symbol).

#### Table 2-1 F56 Tag

| 15  | 14                | 13 | 12  | 11 | 10 | 9 | 8 | 7           | 6  | 5  | 4 | 3 | 2 | 1 | 0 |

|-----|-------------------|----|-----|----|----|---|---|-------------|----|----|---|---|---|---|---|

| SDF |                   |    |     |    |    |   |   | FTYPE SWPRI |    |    |   |   |   |   |   |

| V   | LAN P             | RI | CFI |    |    |   |   |             | VL | AN |   |   |   |   |   |

|     | Source GloRT      |    |     |    |    |   |   |             |    |    |   |   |   |   |   |

|     | Destination GloRT |    |     |    |    |   |   |             |    |    |   |   |   |   |   |

Table 2-2 shows the F64 and F96 tags.

#### Table 2-2 F64/F96 Tags

| 15          | 14               | 13 | 12  | 11 | 10 | 9    | 8      | 7      | 6   | 5  | 4 | 3 | 2 | 1 | 0 |

|-------------|------------------|----|-----|----|----|------|--------|--------|-----|----|---|---|---|---|---|

| FTYPE SWPRI |                  |    |     |    |    | USER |        |        |     |    |   |   |   |   |   |

| V           | LAN P            | RI | CFI |    |    |      |        |        | VL  | AN |   |   |   |   |   |

|             | Source GloRT     |    |     |    |    |      |        |        |     |    |   |   |   |   |   |

|             |                  |    |     |    |    | De   | stinat | ion Gl | oRT |    |   |   |   |   |   |

|             | EXTRA (F96 only) |    |     |    |    |      |        |        |     |    |   |   |   |   |   |

|             | EXTRA (F96 only) |    |     |    |    |      |        |        |     |    |   |   |   |   |   |

#### The FTYPE is:

0x0000 = Normal frame

0x1000 = Special delivery

331496-002

NOTE: This page intentionally left blank.

# 3.0 Pin Descriptions

The FM5000/FM6000 comes in several port bandwidth options. This section describes the largest port bandwidth configuration. The actual pin-list is presented in Table 11-1 and Table 11-2.

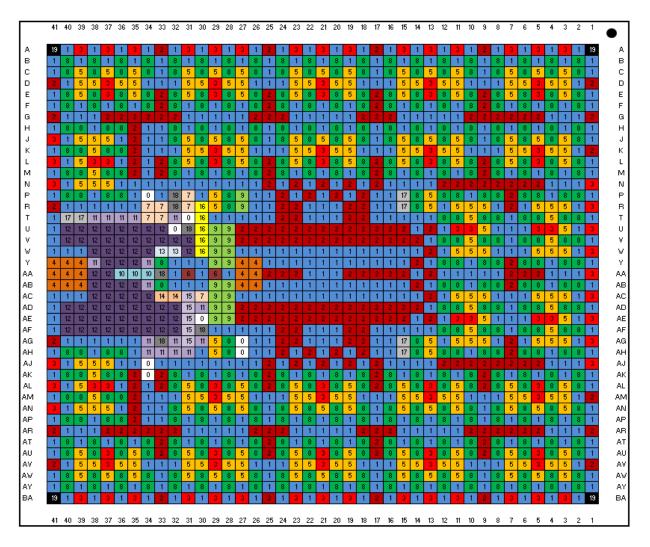

## 3.1 Pin Overview

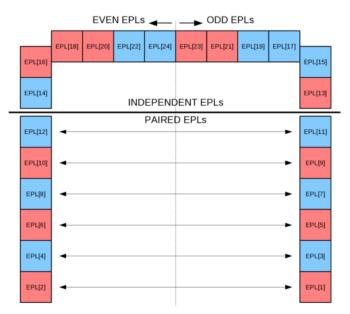

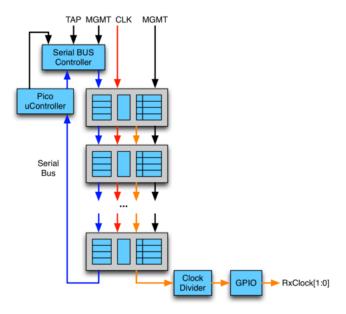

Figure 3-1 shows an overview of the pins used for the FM5000/FM6000. Some part variants are restricted to a reduced number of Ethernet ports due to core bandwidth limitations. See Section 11.0, "Mechanical Specification" for additional pin information.

Figure 3-1 FM5000/FM6000 Pin Overview

# 3.2 Signal Name Convention

The following signal name conventions are used:

- **Signal Mnemonic** The signal mnemonic is a generic name used as a prefix to identify the function of this pin.

- **Negative Logic** Signal with inverted logic (0=asserted, 1=deasserted) are designated by using the signal mnemonic following by \_N suffix.

- **Differential Pairs** Differential signals are designated by using the signal mnemonic followed by \_P for the positive pin and \_N for the negative pair.

- **Bus Designation** A signal that is part of a bus is designated by using the signal mnemonic followed by [n] to designate the pin number in that bus. The entire bus or part of a bus is designated using the [M...N] designation. As an example, DATA[31..0] bus represents 32 pins designated DATA[0], DATA[1], etc...

- **Set** A set of signals is referenced globally using name{M...N} or name{A,B,C,D}. The actual pin designation is formed by using the signal mnemonic and concatenating one of the values of the set. As an example, the pin set REFCLK{1..4}{A,B}{P,N} represents 16 pins designated REFCLK1AP, REFCLK1AN, REFCLK1BP, etc...

- **Direction** The following pin direction types are used:

- Input to the chip

- OUT: Output from the chip

- IN/OUT: Might operate as input or output

- OD: Open drain output

- OC: Open collector output

- Power: A pin used for power

- Ground: A pin used for ground

- Sense: A pin used for sensing (no input/output concept)

- **Standard** The following pin input/output buffer types are used:

- CML

- LVCMOS

- LVPECL

# 3.3 Detailed Pin Descriptions

The FM5000/FM6000 pins are listed in the following tables. GPIOs pins are latched when CHIP RESET N is de-asserted to provide default configurations.

# 3.3.1 Ethernet Port Pins

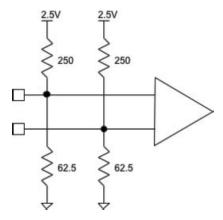

| Pin Name               | Direction | Туре   | Usage                                                                                                                                                                                                                         |

|------------------------|-----------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P{124}_R{A,B,C,D}{P,N} | IN        | CML    | SerDes receive ports.  There are four pairs per port. Each set {A,B,C,D} of four pairs can be mapped to LANEOLANE3. In CML or to LANE3LANEO by software. Unused pins can be left floating; they are internally terminated.    |

| P{124}_T{A,B,C,D}{P,N} | OUT       | CML    | SerDes transmit ports (i=[124]). There are four pairs per port. Each set {A,B,C,D} of four pairs can be mapped to LANE0.LANE3 or to LANE3LANE0 by software. Unused pins can be left floating; they are internally terminated. |

| ETH_RCK[14]{P,N)       | IN        | LVPECL | Ethernet reference clocks for SerDes; 156.25 MHz.                                                                                                                                                                             |

| ETH_CLKOUT_{A,B}       | OUT       | LVCMOS | Recovered clocks from SerDes.                                                                                                                                                                                                 |

## 3.3.2 PCIe Pins

| Pin Name           | Direction | Туре   | Usage                                     |

|--------------------|-----------|--------|-------------------------------------------|

| PX_R{A,B,C,D}{P,N} | IN        | CML    | PCIe receive lanes.                       |

| PX_T{A,B,C,D}{P,N} | OUT       | CML    | PCIe transmit lanes.                      |

| PX_RCK{P,N}        | IN        | LVPECL | PCIe reference clock.<br>Must be 125 MHz. |

# 3.3.3 Power Pins

| Pin Name   | Direction | Туре  | Usage                                                                                                                 |

|------------|-----------|-------|-----------------------------------------------------------------------------------------------------------------------|

| VDD        | Power     | N/A   | Variable core power supply that can be adjusted to support higher bandwidth.                                          |

| VDDS       | Power     | N/A   | Fixed core power supply.                                                                                              |

| VDD25      | Power     | N/A   | TTL I/O power supply.                                                                                                 |

| AVDD25     | Power     | N/A   | LVPECL reference clocks power supply.                                                                                 |

| AVDD       | Power     | N/A   | SerDes analog power supply.                                                                                           |

| VDDPLL     | Power     | N/A   | Analog power for frame handler PLL.                                                                                   |

| VFB1, VFB2 | Reserved  | N/A   | Must be tied to ground for normal operation.  Permanent damage can occur if this pin is tied to a positive potential. |

| VSS        | Ground    | N/A   | Ground.                                                                                                               |

| VDDK       | OUT       | Power | Kelvin sense pin for the VDD power plane on the die.<br>Leave open if not used.                                       |

| VSSK       | OUT       | Power | Kelvin sense pin for the VSS power plane on the die.<br>Leave open if not used.                                       |

| VDDSK      | OUT       | Power | Kelvin sense pin for the VDD power plane on the die.<br>Leave open if not used.                                       |

| VSSK2      | OUT       | Power | Kelvin sense pin for the VSS power plane on the die.<br>Leave open if not used.                                       |

# 3.3.4 External Bus Interface Pins

| Pin Name   | Direction  | Туре   | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------------|------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_EBI    | IN         | LVCMOS | Bus interface clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ADDR[23:2] | IN         | LVCMOS | Address inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| DATA[31:0] | IN         | LVCMOS | Data bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| PAR[3:0]   | IN/OUT     | LVCMOS | Data parity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| CS_N       | IN/OUT     | LVCMOS | Chip Select (Active low).  This pin is sampled when CHIP_RESET_N is de-asserted. If this pin is low, EBI is assumed to not be used and EBI_CLK is ignore and replaced internally with PCIE_REFCLK.                                                                                                                                                                                                                                                                                                            |

| AS_N       | IN         | LVCMOS | Address Strobe (Input, active low).                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| RW_N       | IN         | LVCMOS | Read/Write.  Defines the type of transaction (read or write) being requested.  Polarity of this signal depends on the RW_INV strapping pin. When RW_INV is pulled down to ground, read is active high while write is active low. Conversely, when RW_INV is pulled up to VDD25, read is active low while write is active high.                                                                                                                                                                                |

| DTACK_N    | OUT        | LVCMOS | Data Transfer Acknowledge. Indicates the completion of a data transfer. This signal is actively asserted for one cycle when data transfer is ready during read or latched during write and then actively de-asserted for 1 cycle, the cycle after, and finally tri-stated for all other cycles. Polarity of this signal is determined by DTACK_INV strapping pin. If DTACK_INV is pulled down to ground at reset, DTACK_N is active low. If DTACK_INV is pulled up to VDD25 at reset, DTACK_N is active high. |

| DERR_N     | OUT        | LVCMOS | Write Data Parity Errors. Only asserted (and valid) when DTACK_N asserted. Tri-stated otherwise.                                                                                                                                                                                                                                                                                                                                                                                                              |

| INTR_N     | Open drain | LVCMOS | Interrupt. This pin is active low and asserted each time an interrupt condition exists in the chip. The pin gets de-asserted once all interrupt sources have been cleared. Pull down current = 30 mA.                                                                                                                                                                                                                                                                                                         |

## 3.3.5 DMA Interface Pins

| Pin Name | Direction | Туре   | Usage                                                                                                                                 |

|----------|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------|

| TXRDY_N  | OUT       | LVCMOS | Transmit FIFO Ready. Asserted each time the switch can accept a new word of data for packet transmission from the CPU to the network. |

| RXRDY_N  | OUT       | LVCMOS | Receive Data Ready. Asserted each time the switch has data in its receive FIFO for the CPU.                                           |

| RXEOT_N  | OUT       | LVCMOS | End of frame indication. Asserted while reading the last data word of a packet to indicate this is the last work of the packet.       |

# **3.3.6 GPIOs and Strapping Pins**

| Pin Name                                                                    | Direction | Туре   | Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

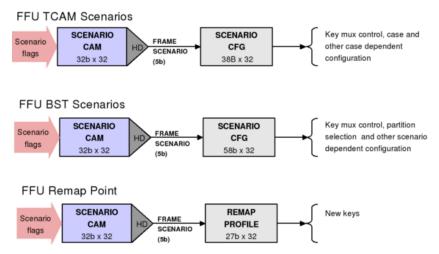

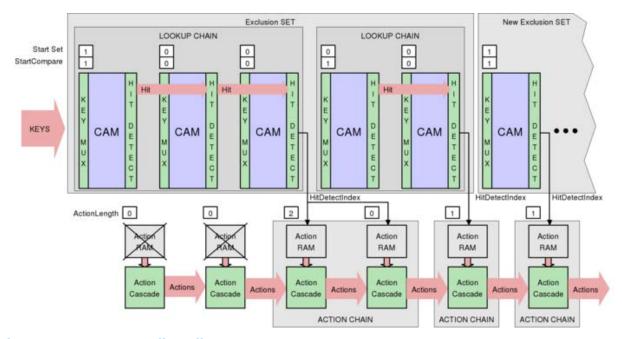

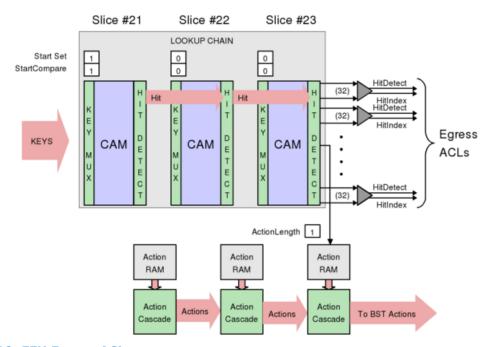

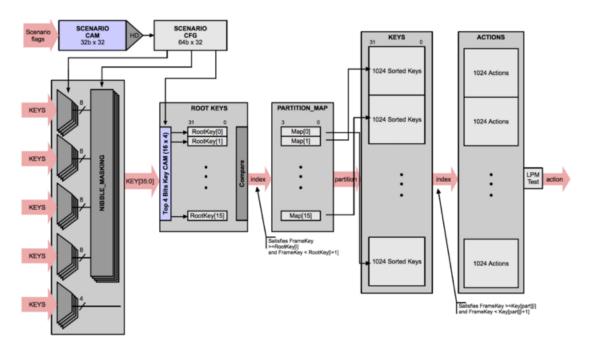

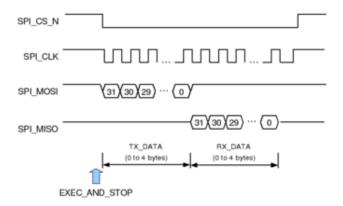

|-----------------------------------------------------------------------------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|