# **Intel® Ethernet Switch FM10000**

**Datasheet**

**Ethernet Networking Division (ND)**

# **Revision History**

| Revision | Date          | Comments                                                                                                                                                                                                      |

|----------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.1      | April 3, 2018 | <ul> <li>Updates include the following:</li> <li>Updated Section 7.4.1, "DFE Tuning &amp; Emphasis".</li> <li>Added Section 12.4.6, "FM10840/FM10420 Voltage Initial Conditions for Fusebox Read".</li> </ul> |

| 2.0      | May 12, 2016  | Initial release (Intel public).                                                                                                                                                                               |

## **Contents**

| 1.0 | Intro  | duction                                      | 13 |

|-----|--------|----------------------------------------------|----|

| 1.1 | Sco    | ppe                                          | 13 |

| 1.2 | Pro    | duct Applicability                           | 13 |

| 1.3 | Do     | cument Organization                          | 14 |

| 1.4 | De     | finitions                                    | 15 |

| 2.0 | Arch   | itecture Overview                            | 17 |

| 2.1 | Ov     | erview                                       | 17 |

| 2.2 | Ма     | nagement Overview                            | 19 |

| 2   | 2.2.1  | Access to 64-bit or 128-bit Registers        | 21 |

| 2   | 2.2.2  | Global Register Space                        | 21 |

| 2   | 2.2.3  | Inactive or Non-existent Registers           | 22 |

| 2.3 | Sw     | itch Aggregation and Frame Tagging           | 22 |

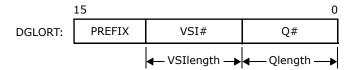

| 2   | 2.3.1  | GLORT                                        | 24 |

| 2   | 2.3.2  | USER Field                                   | 24 |

| 2   | 2.3.3  | FTYPE                                        | 24 |

| 2   | 2.3.4  | VID/VPRI                                     | 24 |

| 2   | 2.3.5  | SWPRI                                        | 25 |

| 2.4 | Fra    | me Sizes and Frame Rate                      | 25 |

| 3.0 | Pin D  | Descriptions                                 | 27 |

| 3.1 | Sig    | nal Name Convention                          | 28 |

| 3.2 | De     | tailed Pin Descriptions                      | 29 |

| 3   | 3.2.1  | Ethernet Port Pins                           | 29 |

| 3   | 3.2.2  | PCIe Pins                                    | 29 |

| 3   | 3.2.3  | General Purpose Input/Output Pins            | 30 |

| 3   | 3.2.4  | Serial Peripheral Interface                  | 30 |

| 3   | 3.2.5  | I <sup>2</sup> C Pins                        | 30 |

| 3   | 3.2.6  | MDIO Pins                                    | 31 |

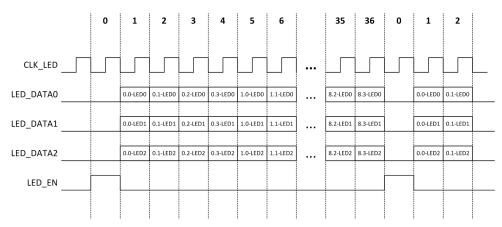

| 3   | 3.2.7  | LED Pins                                     | 31 |

| 3   | 3.2.8  | JTAG Pins                                    | 31 |

| 3   | 3.2.9  | External Bus Interface Pins                  | 32 |

| 3   | 3.2.10 | Miscellaneous Pins                           | 32 |

| 3   | 3.2.11 | IEEE1588 Interface Pins                      | 33 |

| 3   | 3.2.12 | Power Pins                                   | 33 |

| 3   | 3.2.13 | Reserved Pins                                | 34 |

| 3   | 3.2.14 | Sensing/Reference Pins                       | 34 |

| 4.0 | Rese   | t, Boot and Clocking                         | 35 |

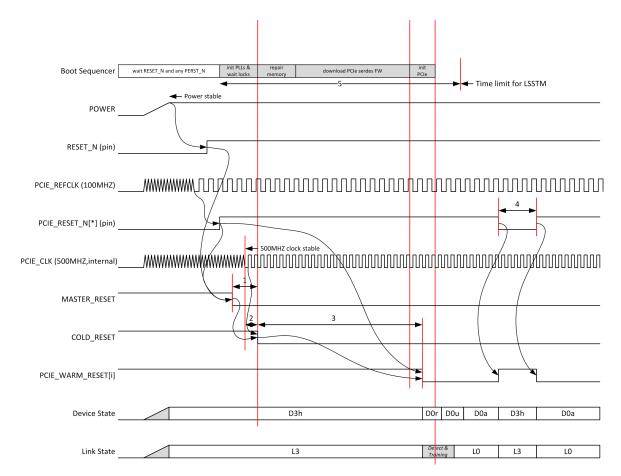

| 4.1 | Res    | set and Boot                                 | 35 |

| 4   | 1.1.1  | Types of Reset                               | 35 |

| 4   | 1.1.2  | Reset Distribution                           | 37 |

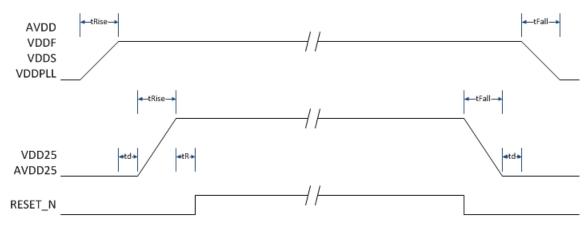

| 4   | 1.1.3  | Power Sequencing and Reset Sequence          | 39 |

| 4.2 | Bas    | se Clocking                                  | 47 |

| 4.3 |        | ended PCIe Clocking                          |    |

| 4   | 1.3.1  | Overview                                     |    |

| 4   | 1.3.2  | Clock Signals                                | 51 |

| 4   | 1.3.3  | Clock Monitor                                |    |

| 4   | 1.3.4  | XCLK Controller                              | 54 |

| Δ   | 135    | Clock Source Selection in Hot Plug-in System | 56 |

| 4   | 4.3.6  | Control and Diagnostics                   | 58   |

|-----|--------|-------------------------------------------|------|

| 5.0 | Ether  | net Switch                                | . 61 |

| 5.1 | L Ove  | rview                                     | 61   |

| 5.2 | 2 Qua  | d Port Channels                           | 62   |

| 5.3 | 3 Ingr | ess Crossbar                              | 62   |

| 5.4 | l Seg  | ment Scheduler                            | 63   |

| į   | 5.4.1  | Scheduler Lists and Physical Port Mapping | 63   |

| į   | 5.4.2  | Managing Segment Free List                | 65   |

| į   | 5.4.3  | Scheduler Initialization                  | 65   |

| 5.5 | 5 Rece | eive Queues and Transmit Queues           | 68   |

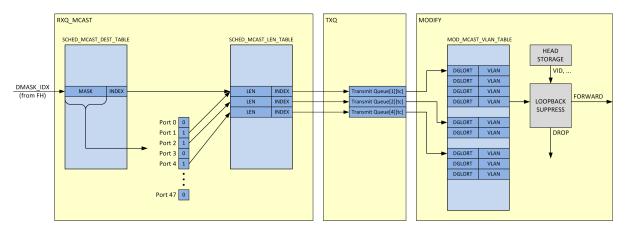

| į   | 5.5.1  | Queuing                                   | 68   |

| į   | 5.5.2  | Frame Replication on Same Port            | 69   |

| į   | 5.5.3  | MODIFY Loopback Suppress                  | 70   |

| Į   | 5.5.4  | Managing MCAST Tables                     |      |

| į   | 5.5.5  | Multicasting Registers                    | 71   |

| į   | 5.5.6  | Replication to VFs                        | 71   |

| į   | 5.5.7  | Loopback Suppression from PCIe Ports      |      |

| į   | 5.5.8  | Cut-through and Store-and-Forward Modes   |      |

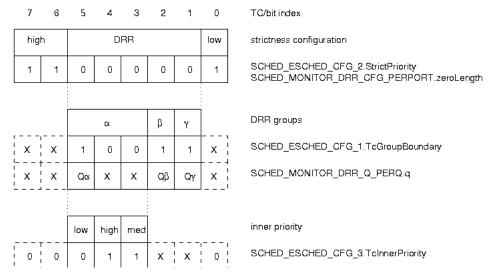

| 5.6 | 5 Fran | ne Scheduling                             | 74   |

| į   | 5.6.1  | Overview                                  | 74   |

| į   | 5.6.2  | Register Set                              |      |

| į   | 5.6.3  | Detailed Scheduling Algorithm             |      |

|     | 5.6.4  | Algorithm Notes                           |      |

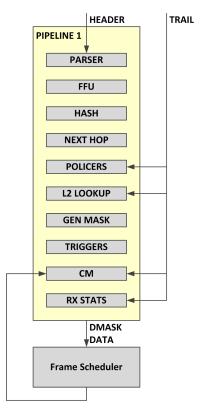

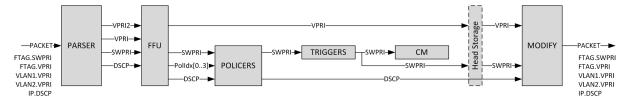

| 5.7 |        | ne Processing Pipeline                    |      |

| į   | 5.7.1  | Overview                                  |      |

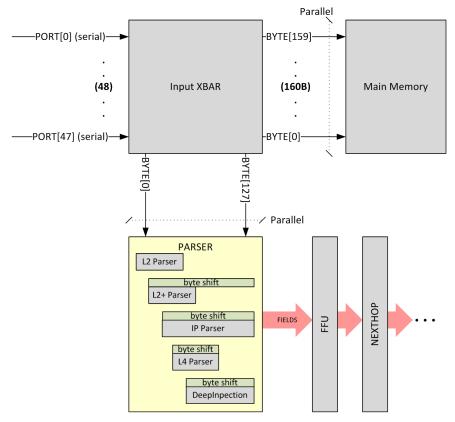

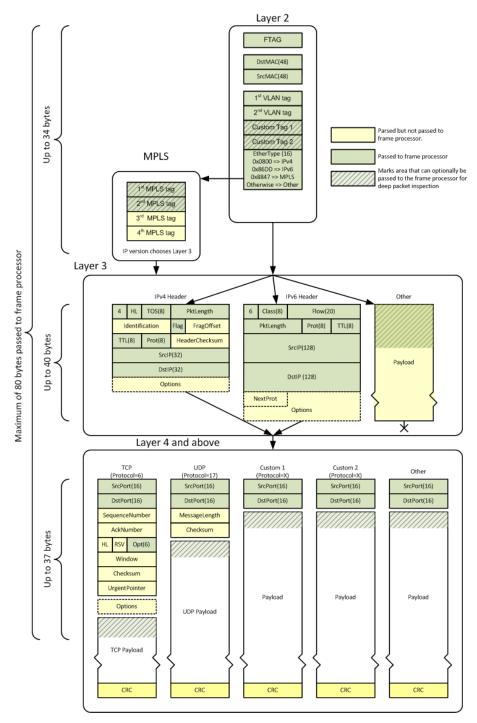

| į   | 5.7.2  | Parser                                    |      |

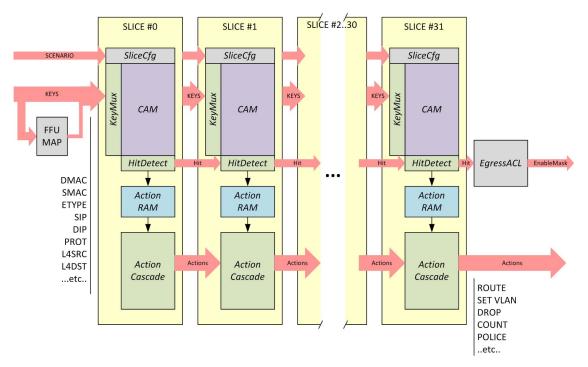

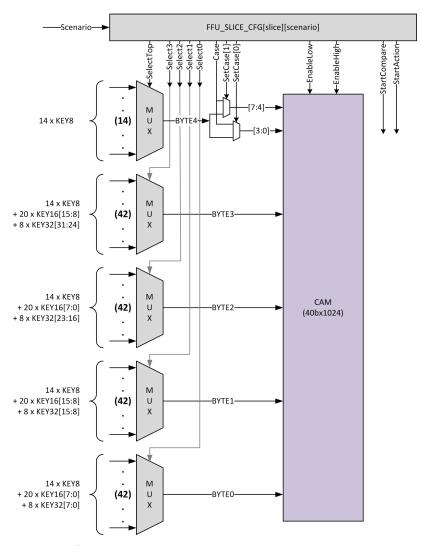

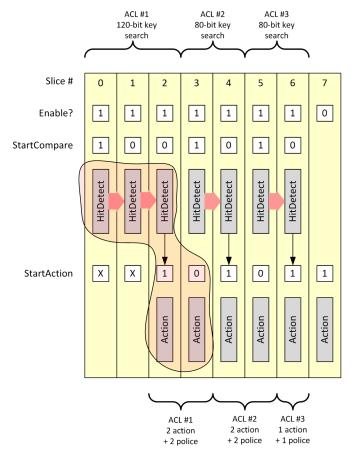

|     | 5.7.3  | Filtering and Forwarding Unit             |      |

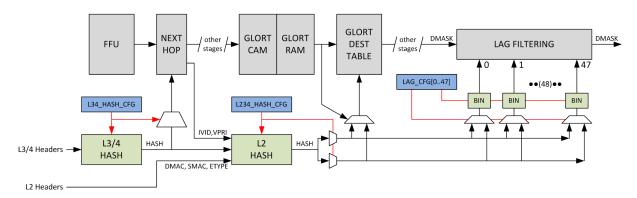

|     | 5.7.4  | Frame Hashing                             |      |

|     | 5.7.5  | Next Hop                                  |      |

|     | 5.7.6  | Policers                                  |      |

|     | 5.7.7  | Layer 2 Lookup                            |      |

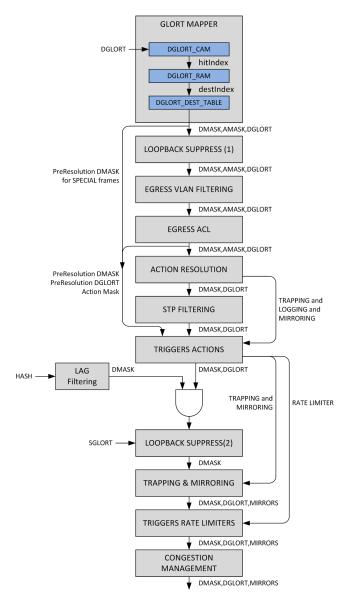

|     | 5.7.8  | Destination Mask Generation               |      |

|     | 5.7.9  | Triggers                                  |      |

| -   | 5.7.10 | Congestion Management                     |      |

|     | 5.7.11 | Statistics and Monitoring                 |      |

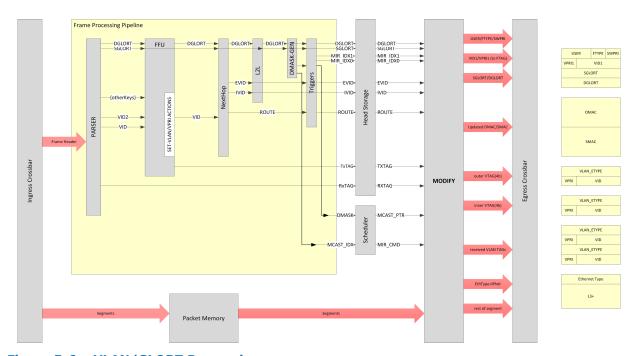

| 5.8 | _      | ess Modifications                         |      |

| -   | 5.8.1  | Overview                                  |      |

|     |        | FTAG Generation or Modification           |      |

|     | 5.8.3  | Special Packets                           |      |

| -   | 5.8.4  | L2 Modification                           |      |

|     | 5.8.5  | L3 Modification                           |      |

|     | 5.8.6  | Truncation                                |      |

|     | 5.8.7  | Pause Generation                          |      |

|     | 5.8.8  | Frame Sizes and Statistics                |      |

| 6.0 |        | Host Interface                            |      |

| 6.1 |        | t Interface Overview                      |      |

| 6.2 |        | E Lane Reversal Support                   |      |

| 6.3 |        | Point Overview                            |      |

| 6.4 |        | er Up and Fundamental Reset Handling      |      |

| (   | 6.4.1  | Data Path Reset                           | 211  |

# Intel® Ethernet Switch FM10000 Datasheet Contents

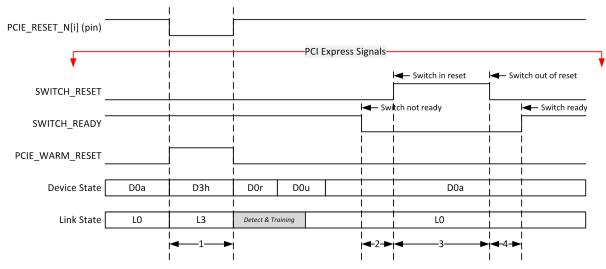

| 6.5 | 5 PEP   | Reset Sequences                                          | 212 |

|-----|---------|----------------------------------------------------------|-----|

|     | 6.5.1   | WARM and PCIE Reset                                      |     |

|     | 6.5.2   | Physical Function FLR (PFLR) and D3hot to D0 Transitions |     |

|     | 6.5.3   | Data Path Reset                                          | 213 |

|     | 6.5.4   | Transition to D3hot                                      | 214 |

|     | 6.5.5   | Virtual Function FLR (VFLR)                              | 214 |

| 6.6 | 5 PCI   | Express Error Events and Error Reporting                 |     |

|     | 6.6.1   | General Description                                      | 215 |

|     | 6.6.2   | Error Events                                             | 215 |

| 6.7 | 7 Inte  | rnal Memory Read Errors                                  | 217 |

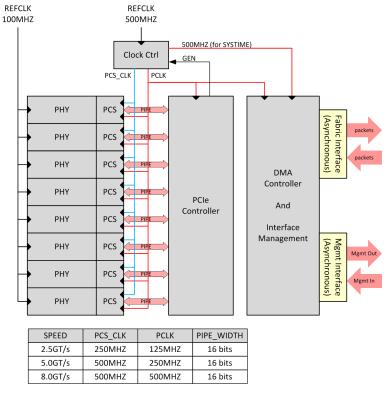

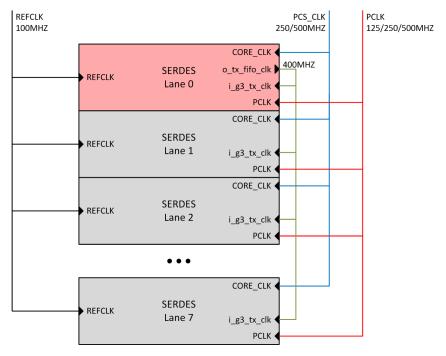

| 6.8 | 3 Clo   | king                                                     | 218 |

| 6.9 | 9 Ser   | Des Management                                           | 220 |

| 6.1 | 10 32-  | bit/64-bit Addressing                                    | 221 |

| 6.1 | 11 Mer  | nory Map                                                 | 221 |

|     | 6.11.1  | RX Queue Mapping                                         | 224 |

|     | 6.11.2  | TX Queue Mapping                                         | 225 |

|     | 6.11.3  | Virtual Function Queue Configuration                     | 226 |

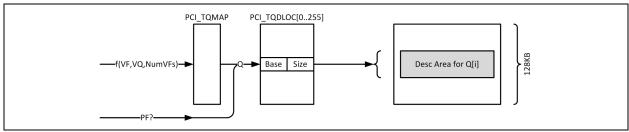

|     | 6.11.4  | TX Descriptors Mapping                                   | 226 |

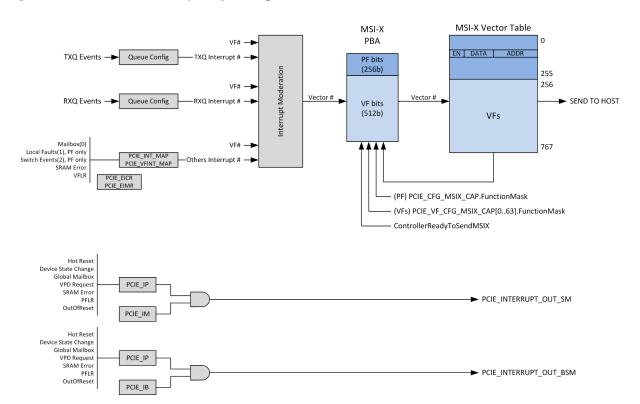

| 6.1 | 12 Inte | errupts and Faults                                       | 228 |

|     | 6.12.1  | Interrupt Sources                                        | 228 |

|     | 6.12.2  | Interrupt Mapping                                        | 229 |

|     | 6.12.3  | Faults                                                   | 231 |

|     | 6.12.4  | Timeout Interrupt                                        | 231 |

|     | 6.12.5  | Interrupt Moderators                                     | 232 |

| 6.1 | 13 Sta  | tistics                                                  | 235 |

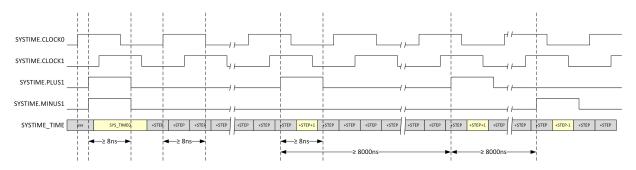

| 6.1 | 14 Tim  | e Reference                                              | 236 |

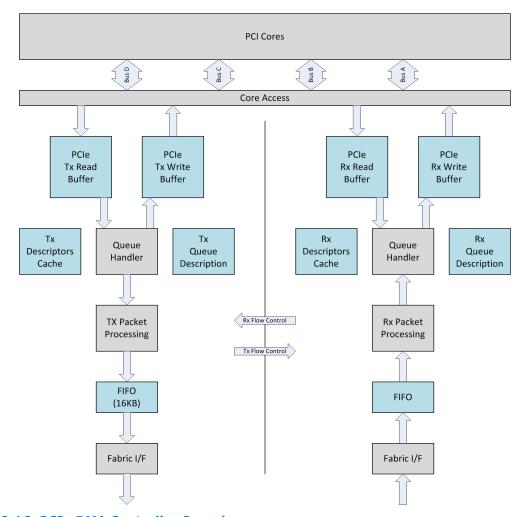

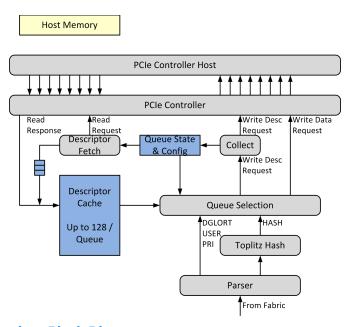

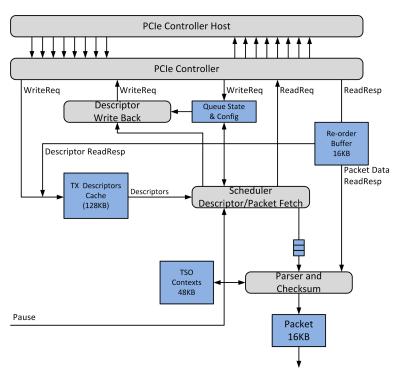

| 6.1 | 15 DM   | A Controller Overview                                    | 238 |

|     | 6.15.1  | Overview                                                 | 238 |

|     | 6.15.2  | Data Flow                                                |     |

|     | 6.15.3  | Queue Disable Operation                                  | 243 |

|     | 6.15.4  | Performance                                              |     |

|     | 6.15.5  | Packet Format                                            |     |

|     | 6.15.6  | Switch Fabric Congestion                                 | 250 |

|     | 6.15.7  | Host Congestion                                          |     |

|     | 6.15.8  | TLP Processing Hints                                     |     |

|     | 6.15.9  | Host Response Time Measurements                          |     |

|     | 6.15.10 | Packet Loopback                                          | 252 |

| 6.1 | 16 Init | alization After Reset                                    | 252 |

| 6.1 | 17 VPC  | Handling                                                 | 257 |

| 6.1 | 18 Pac  | ket Reception                                            | 258 |

|     | 6.18.1  | Overview                                                 | 258 |

|     | 6.18.2  | Parsing                                                  | 259 |

|     | 6.18.3  | Queue Assignment                                         | 259 |

|     | 6.18.4  | Receive Side Scaling                                     | 261 |

|     | 6.18.5  | VLAN Membership Checking                                 | 264 |

|     | 6.18.6  | Loopback Suppress                                        | 264 |

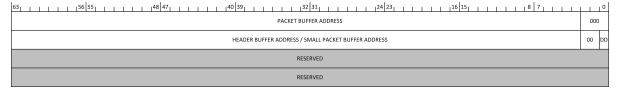

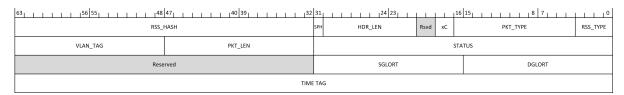

|     | 6.18.7  | Receive Descriptors                                      | 264 |

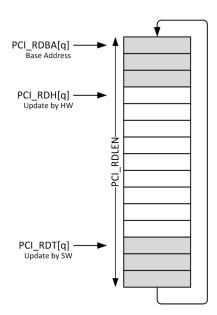

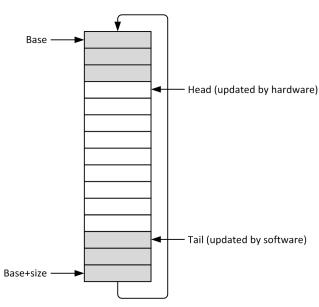

|     | 6.18.8  | Receive Descriptor Queue                                 | 269 |

|     | 6.18.9  | Receiver Header or Small Packet Processing               | 271 |

|     | 6.18.10 | Receiver TCP/UDP Checksum Offload                        | 272 |

| 6.18   |       | Receiver Performance                         |     |

|--------|-------|----------------------------------------------|-----|

| 6.19   | Pack  | et Transmission                              | 274 |

| 6.19   | 9.1   | Overview                                     | 274 |

| 6.19   | 9.2   | Pull Model                                   | 275 |

| 6.19   | 9.3   | Push Model                                   | 276 |

| 6.19   | 9.4   | Transmit Scheduler                           | 276 |

| 6.19   | 9.5   | Packet Padding and Transmitter Throttling    | 277 |

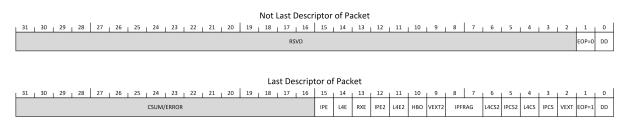

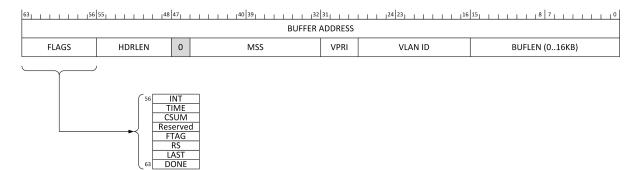

| 6.19   |       | Transmit Descriptors                         |     |

| 6.19   |       | Generating FTAG                              |     |

| 6.19   |       | Transmitter Descriptor Queue Structure       |     |

| 6.19   |       | Transmit TCP Segmentation & Checksum Offload |     |

| 6.19   |       | Transmit Checksum Offloading                 |     |

| 6.20   |       | alization                                    |     |

|        |       |                                              |     |

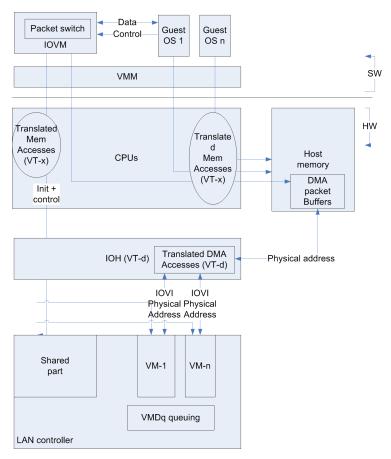

| 6.20   |       | Overview                                     |     |

| 6.20   |       | Direct Assignment Model                      |     |

| 6.20   |       | System Overview                              |     |

| 6.20   |       | PCI-SIG SR-IOV Support                       |     |

| 6.20   |       | Packet Switching                             |     |

| 6.20   |       | Security Features                            |     |

| 7.0 Et | therr | net Port Logic (EPL)                         | 299 |

| 7.1    | Over  | view                                         | 299 |

| 7.2    | Mode  | e of Operation                               | 301 |

| 7.3    | Refe  | rence Clock                                  | 302 |

| 7.4    |       | es Characteristics                           |     |

| 7.4.   |       | DFE Tuning & Emphasis                        |     |

| 7.4.   |       | Pattern Generator/Comparator                 |     |

| 7.4.   |       | Loopbacks                                    |     |

| 7.4.   |       | Eye Measurement                              |     |

| 7.5    |       | vered Clocks                                 |     |

| 7.6    |       | -negotiation                                 |     |

| 7.6.   |       | Clause 73                                    |     |

|        |       |                                              |     |

| 7.6.   |       | Clause 37                                    |     |

| 7.6.   |       | SGMII                                        |     |

| 7.7    |       | ical Coding Sub-layer (PCS)                  |     |

| 7.7.   |       | 100GBase-R4                                  |     |

| 7.7.   |       | 40GBase-R4                                   |     |

| 7.7.   |       | 10GBase-R                                    |     |

| 7.7.   |       | 1000Base-X Frame Format                      | 312 |

| 7.7.   | 5     | Link Status                                  | 313 |

| 7.7.   | 6     | FSIG                                         | 313 |

| 7.7.   | 7     | IFGs                                         | 313 |

| 7.7.   | 8     | Changing PCS Mode                            | 314 |

| 7.8    | MAC   |                                              | 315 |

| 7.8.   | 1     | Preamble and CRC Optional Processing         | 316 |

| 7.8.   | 2     | Packet Generation                            | 316 |

| 7.8.   | 3     | Reception Errors                             | 318 |

| 7.8.   |       | Counters                                     |     |

| 7.8.   |       | Energy Efficient Ethernet                    |     |

| 7.8.   |       | Time Stamping for IEEE1588                   |     |

| 7.8.   |       | Segment Rate Throttle                        |     |

|        |       |                                              |     |

# ${\it Intel}^{\it @} \ {\it Ethernet Switch FM10000 Datasheet} \\ {\it Contents}$

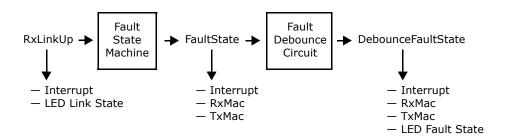

|   | 7.9   | Status and Interrupts                             | 323 |

|---|-------|---------------------------------------------------|-----|

|   | 7.10  | Link State and Fault Conditions                   | 323 |

| 8 | .0 Tu | unneling Engine                                   | 325 |

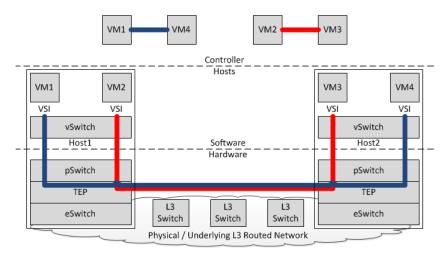

|   | 8.1   | Overlay Networks Overview                         | 325 |

|   | 8.1.  | 1 Host to Network                                 | 327 |

|   | 8.1.  | 2 Network to Host                                 | 328 |

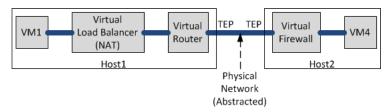

|   | 8.1.  | 3 Virtual Network Functions                       | 329 |

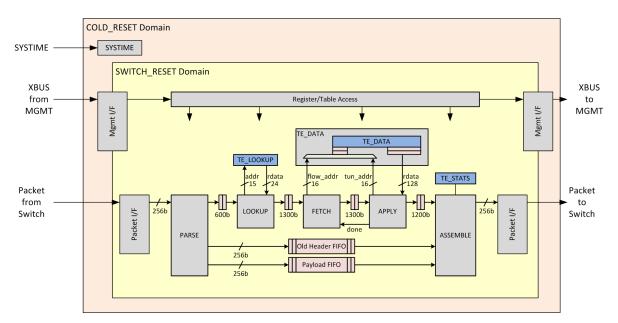

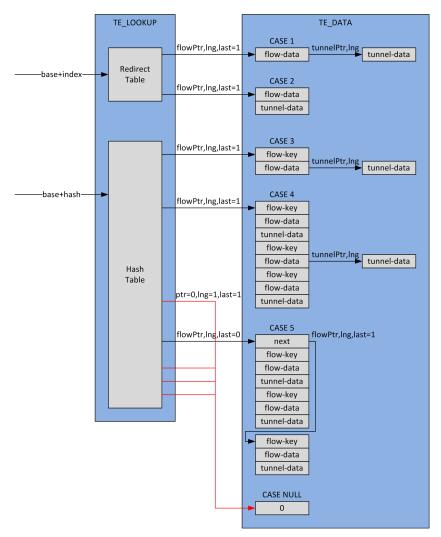

|   | 8.2   | Tunneling Engine Architecture Overview            | 331 |

|   | 8.3   | Packet Disposition                                | 333 |

|   | 8.4   | Packet Format                                     | 334 |

|   | 8.5   | GENEVE Packet Format                              | 337 |

|   | 8.6   | VXLAN-GPE/NSH Packet Format Support               | 338 |

|   | 8.7   | Registers                                         | 341 |

|   | 8.8   | DGLORT/SGLORT Decoding                            | 342 |

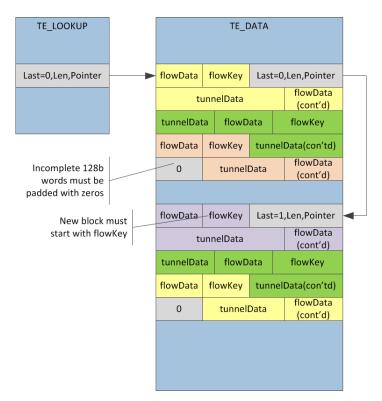

|   | 8.9   | Flow Data, Tunnel Data, and Counters              | 343 |

|   | 8.10  | Encapsulation/NAT                                 | 347 |

|   | 8.10  | 0.1 Data Structures                               | 347 |

|   | 8.10  | 0.2 Switch Roles for Encapsulation/NAT            | 350 |

|   | 8.10  | •                                                 |     |

|   | 8.10  |                                                   |     |

|   | 8.11  | Decapsulation/DeNAT                               |     |

|   | 8.11  | •                                                 |     |

|   | 8.11  | 1.2 Packet Modifications                          | 355 |

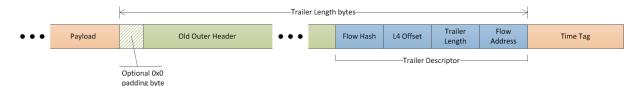

|   | 8.11  | 1.3 Trailer for Saved Outer Header                | 356 |

|   | 8.11  |                                                   |     |

|   | 8.12  | NAT/DeNAT Only                                    |     |

|   | 8.13  | Time Tagging                                      |     |

|   | 8.14  | Aging                                             |     |

|   | 8.15  | Updating Registers                                |     |

|   | 8.15  |                                                   |     |

|   | 8.15  |                                                   |     |

|   | 8.15  |                                                   |     |

|   | 8.15  | -                                                 |     |

|   | 8.16  | Hash Computation                                  |     |

|   | 8.16  | ·                                                 |     |

|   | 8.16  | ·                                                 |     |

| 9 |       | eripherals                                        |     |

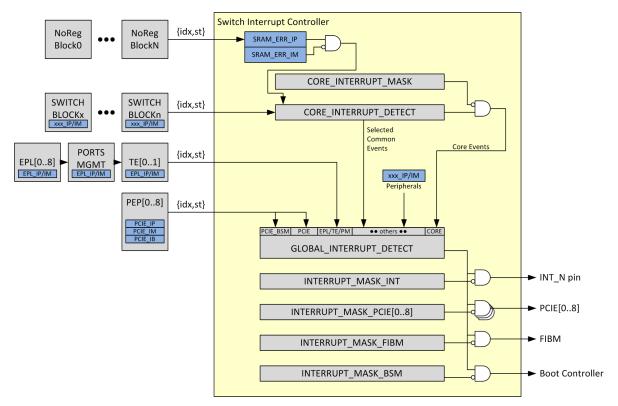

| _ | 9.1   | Interrupt Controller                              |     |

|   | 9.1.  | ·                                                 |     |

|   | 9.1.  | , , , , , , , , , , , , , , , , , , , ,           |     |

|   | 9.1.  | •                                                 |     |

|   | 9.1.  |                                                   |     |

|   | 9.1.  | ·                                                 |     |

|   | 9.1   | Counter Rate Monitor                              |     |

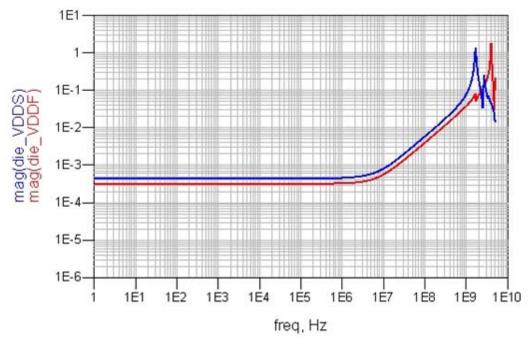

|   | 9.2   | SerDes Management and Temperature/Voltage Sensing |     |

|   | 9.3.1 |                                                   |     |

|   | 9.3.  |                                                   |     |

|   | 9.3.  | -                                                 |     |

|   | 9.3.  | •                                                 |     |

|   | 9.3.4 |                                                   |     |

|   | 9.5.  | 2 FOTE SELDES THRIGHTSULLING.                     | 200 |

| 9.3.6                | Temperature and Voltage Sensing            | 380 |

|----------------------|--------------------------------------------|-----|

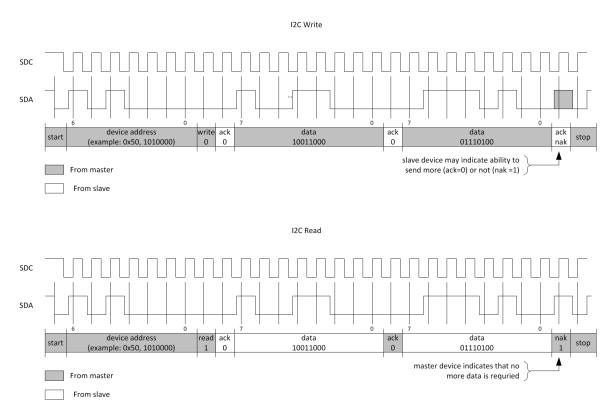

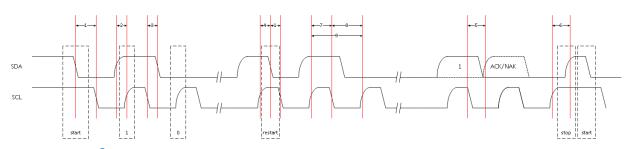

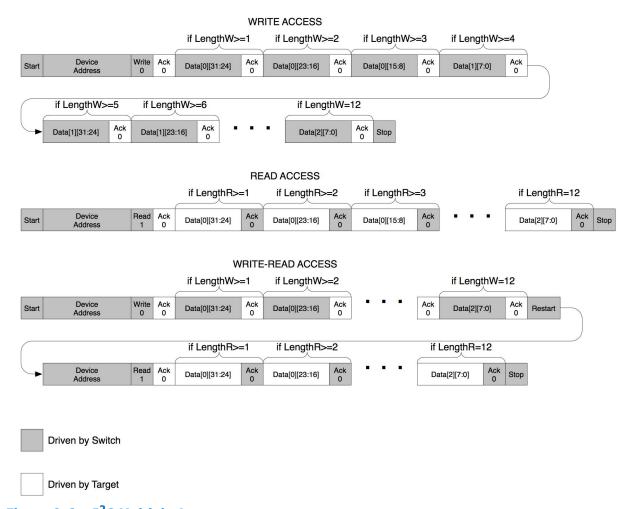

| 9.4 I <sup>2</sup> C | Controller                                 | 381 |

| 9.4.1                | Slave Mode                                 | 384 |

| 9.4.2                | Master Mode                                | 386 |

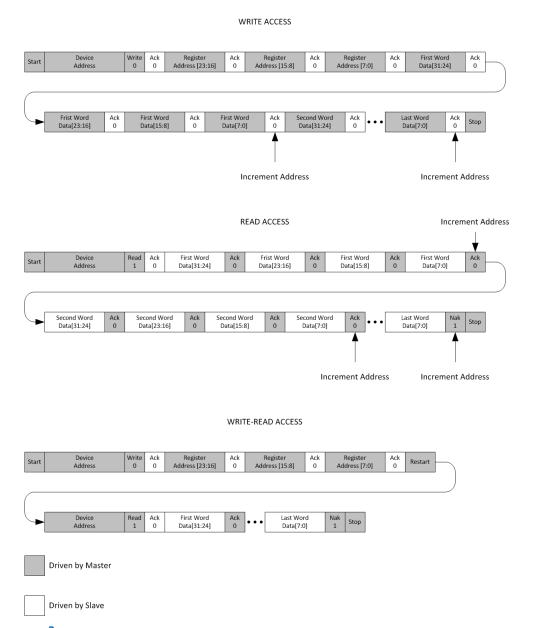

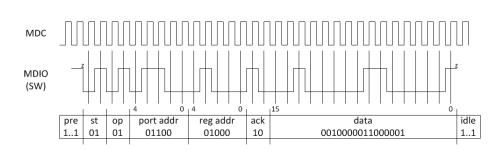

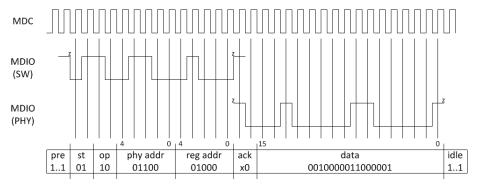

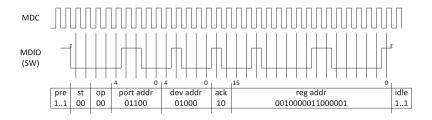

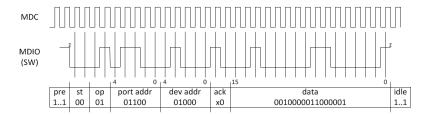

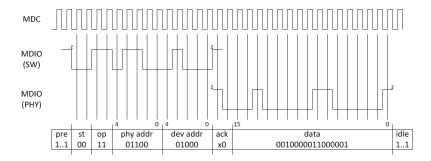

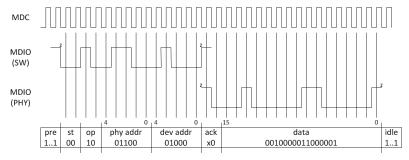

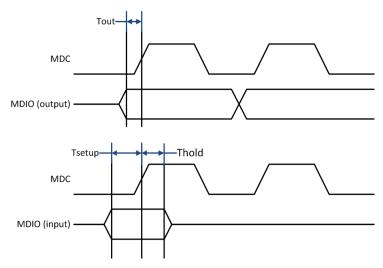

| 9.5 MDI              | O Controller                               | 388 |

| 9.6 GPI              | O Controller                               | 391 |

| 9.7 SPI              | Interface                                  | 391 |

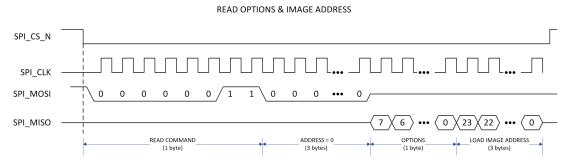

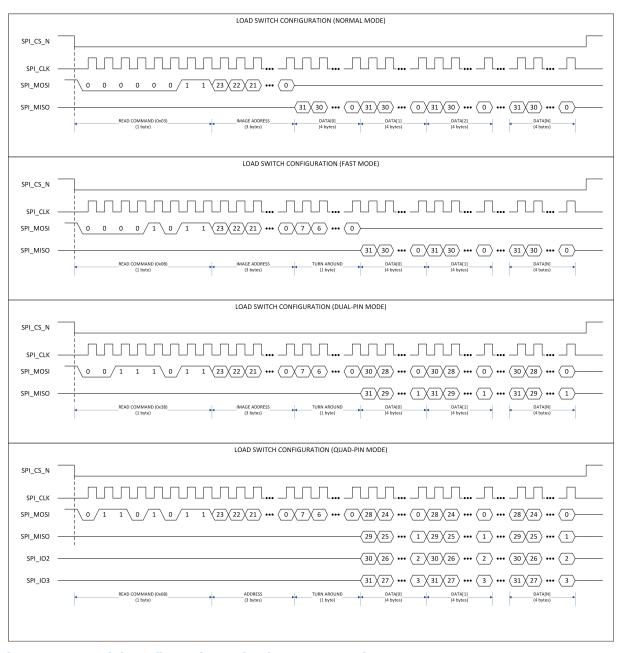

| 9.7.1                | Overview                                   | 391 |

| 9.7.2                | Requirements                               | 392 |

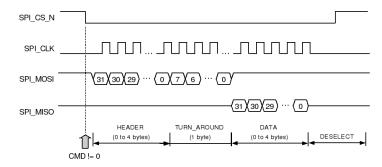

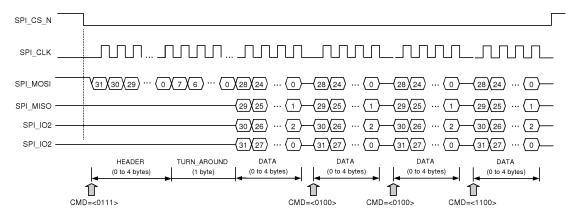

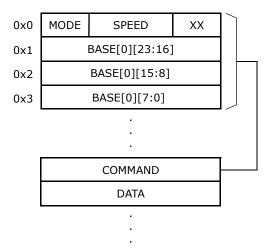

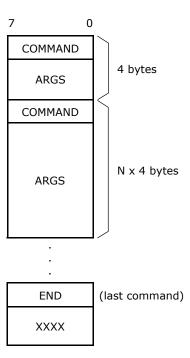

| 9.7.3                | Protocol                                   | 392 |

| 9.7.4                | Management                                 | 395 |

| 9.7.5                | Boot State Machine                         | 397 |

|                      | Controller                                 |     |

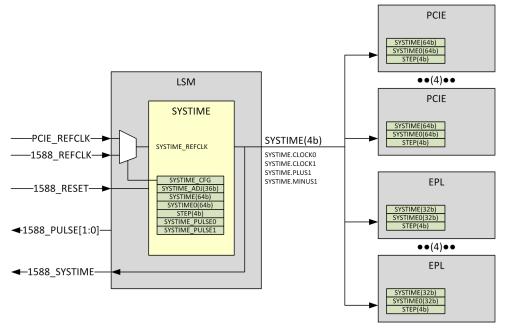

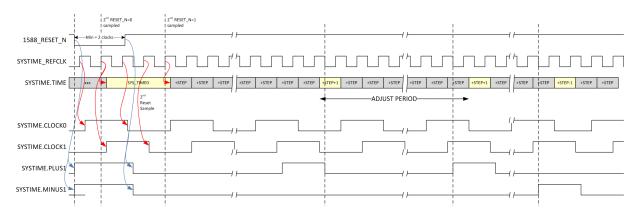

| 9.9 Syst             | em Time and IEEE 1588                      |     |

| 9.9.1                | Initialization of System Time              |     |

| 9.10 In-E            | Band Management                            |     |

| 9.10.1               | Overview                                   |     |

| 9.10.2               | FIBM Frame Format                          | 408 |

| 9.10.3               | Interrupts and RESET                       | 413 |

| 10.0 Relial          | pility, Diagnostics and Testability        | 417 |

| 10.1 Relia           | ability                                    | 417 |

| 10.1.1               | Overview                                   | 417 |

| 10.2 Diag            | gnostics                                   | 418 |

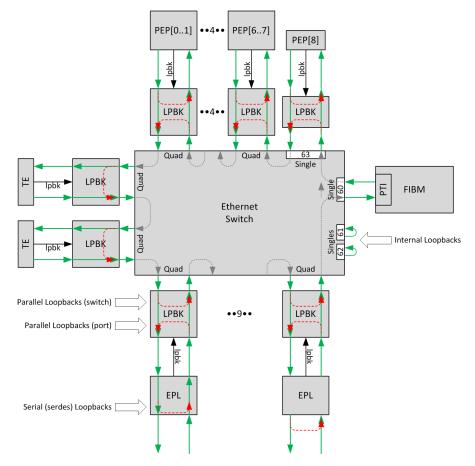

| 10.2.1               | Packet Loopbacks and Packet Test Interface | 418 |

| 10.3 Test            | : Interfaces                               | 421 |

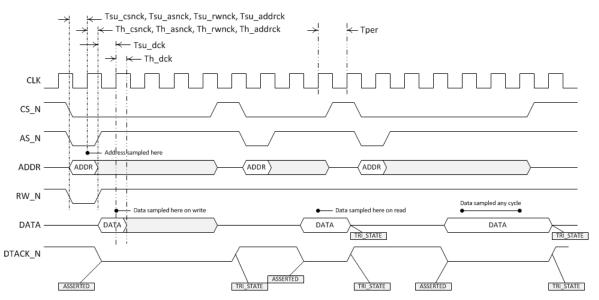

| 10.3.1               | External Bus Interface (EBI)               | 421 |

| 10.3.2               | Scan Interface                             | 423 |

| 10.3.3               | JTAG Interface                             | 423 |

| 11.0 Regis           | ter Definitions                            | 425 |

| 11.1 Defi            | nitions                                    | 425 |

| 11.1.1               | Terminology                                | 425 |

| 11.2 Reg             | ister Set Summary                          | 426 |

| 11.3 EPL             | Registers Description                      | 427 |

| 11.3.1               | EPL Map                                    | 427 |

| 11.3.2               | EPL Enumerated Data Types                  | 432 |

| 11.3.3               | EPL Registers                              | 438 |

| 11.4 PAR             | SER Registers Description                  | 499 |

| 11.4.1               | PARSER Map                                 | 499 |

| 11.4.2               | PARSER Registers                           |     |

| 11.5 FFU             | Registers Description                      | 505 |

| 11.5.1               | FFU Map                                    | 505 |

| 11.5.2               | FFU Enumerated Data Types                  | 505 |

| 11.5.3               | FFU Structures                             | 506 |

| 11.5.4               | FFU Registers                              | 508 |

| 11.6 FFU             | _MAP Registers Description                 | 512 |

| 11.6.1               | FFU_MAP Map                                | 512 |

| 11.6.2               | FFU_MAP Registers                          | 512 |

| 11.7 EAC             | L Registers Description                    | 516 |

| 11.7.1               | EACL Map                                   | 516 |

| 11.7.2               | EACL Registers                             | 516 |

# Intel® Ethernet Switch FM10000 Datasheet Contents

| 11.8  | ARP          | Registers Description            | 518 |

|-------|--------------|----------------------------------|-----|

| 11.8  | 3.1          | ARP Map                          | 518 |

| 11.8  | 3.2          | ARP Structures                   | 518 |

| 11.8  | 3.3          | ARP Registers                    | 519 |

| 11.9  | POLI         | ICER_APPLY Registers Description | 520 |

| 11.9  | 9.1          | POLICER APPLY Map                | 520 |

| 11.9  | 9.2          | POLICER_APPLY Registers          | 520 |

| 11.10 | POLI         | CER_USAGE Registers Description  |     |

|       |              | POLICER_USAGE Map                |     |

|       |              | POLICER_USAGE Structures         |     |

|       |              | POLICER_USAGE Registers          |     |

|       |              | OOKUP Registers Description      |     |

|       |              | L2LOOKUP Map                     |     |

|       |              | L2LOOKUP Registers               |     |

|       |              | OKUP_TCN Registers Description   |     |

|       |              | L2LOOKUP_TCN Map                 |     |

|       |              | L2LOOKUP_TCN Registers           |     |

|       |              | DLER Registers Description       |     |

|       |              |                                  |     |

|       |              | HANDLER Map                      |     |

|       |              | HANDLER Registers                |     |

|       |              | DLER_TAIL Registers Description  |     |

|       |              | HANDLER_TAIL Map                 |     |

|       |              | HANDLER_TAIL Registers           |     |

|       |              | RT Registers Description         |     |

|       |              | GLORT Map                        |     |

|       |              | GLORT Registers                  |     |

|       |              | Registers Description            |     |

|       |              | LAG Map                          |     |

|       |              | LAG Registers                    |     |

|       |              | G_APPLY Registers Description    |     |

|       |              | TRIG_APPLY Map                   |     |

|       |              | TRIG_APPLY Enumerated Data Types |     |

|       |              | TRIG_APPLY Registers             |     |

| 11.18 | TRIG         | G_USAGE Registers Description    | 564 |

| 11.1  | 18.1         | TRIG_USAGE Map                   | 564 |

| 11.1  | 18.2         | TRIG_USAGE Registers             | 564 |

| 11.19 | CM_          | APPLY Registers Description      | 565 |

| 11.1  | 19.1         | CM_APPLY Map                     | 565 |

| 11.1  | 19.2         | CM_APPLY Registers               | 565 |

|       |              | USAGE Registers Description      |     |

|       |              | CM_USAGE Map                     |     |

| 11.2  |              | CM_USAGE Registers               |     |

|       |              | Pagisters Description            |     |

|       | 21.1         | MOD Map                          |     |

|       | 21.2         | MOD Enumerated Data Types        |     |

|       |              | MOD Registers                    |     |

|       |              | STATS Registers Description      |     |

|       |              | RX_STATS Map                     |     |

|       |              | RX STATS Enumerated Data Types   |     |

|       |              |                                  |     |

| 11.2  | <b>44.</b> 3 | RX_STATS Registers               | 593 |

|            | ED Registers Description                                    |     |

|------------|-------------------------------------------------------------|-----|

|            | SCHED Map                                                   |     |

|            | SCHED Registers                                             |     |

|            | 1 Registers Description                                     |     |

| 11.24.1    | FIBM Map                                                    | 608 |

|            | FIBM Registers                                              |     |

| 11.25 MGN  | 1T Registers Description                                    | 619 |

| 11.25.1    | MGMT Map                                                    | 619 |

|            | MGMT Registers                                              |     |

| 11.26 POR  | TS_MGMT Registers Description                               | 659 |

| 11.26.1    | PORTS_MGMT Map                                              | 659 |

| 11.26.2    | PORTS_MGMT Registers                                        | 659 |

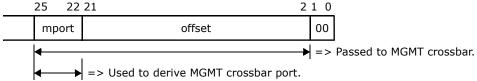

| 11.27 PCIE | PF Registers Description                                    | 667 |

| 11.27.1    | PCIE_PF Map                                                 | 667 |

| 11.27.2    | PCIE_PF Registers                                           | 670 |

| 11.28 PCIE | _VF Registers Description                                   | 717 |

| 11.28.1    | PCIE_VF Map                                                 | 717 |

| 11.28.2    | PCIE_VF Registers                                           | 718 |

| 11.29 PCIE | E_CFG Registers Description                                 | 735 |

|            | PCIE_CFG Map                                                |     |

| 11.29.2    | PCIE_CFG Registers                                          | 737 |

| 11.30 PCIE | E_CFG_VF Registers Description                              | 775 |

| 11.30.1    | PCIE_CFG_VF Map                                             | 775 |

| 11.30.2    | PCIE_CFG_VF Registers                                       | 776 |

|            | legisters Description                                       |     |

| 11.31.1    | TE Map                                                      | 798 |

|            | TE Enumerated Data Types                                    |     |

|            | TE Structures                                               |     |

|            | TE Registers                                                |     |

|            | ical Specification                                          |     |

|            | olute Maximum Ratings                                       |     |

|            | Jude Huximum Rudings                                        |     |

|            | h-Up                                                        |     |

|            | ommended Operating Conditions                               |     |

| 12.4.1     | Scaled Voltages                                             |     |

| 12.4.2     | Non-Scaled Voltages                                         |     |

| 12.4.3     | Ground Returns                                              |     |

|            | Environmental                                               |     |

| 12.4.5     | Voltage Scaling and Voltage Tolerances                      |     |

| 12.4.5     | FM10840/FM10420 Voltage Initial Conditions for Fusebox Read |     |

| 12.4.7     |                                                             |     |

| 12.4.7     | Voltage Tolerances Non-Scaled Voltages                      |     |

| 12.4.6     | Power On Reset Values                                       |     |

|            |                                                             |     |

|            | er Supply Sequencing                                        |     |

| •          | Power and Power Supply Currents                             |     |

| 12.6.1     | Supply Type Definitions                                     |     |

| 12.6.2     | High Current Supply Values                                  |     |

| 12.6.3     | Low Current Supply Values                                   |     |

| 12.6.4     | Idle Power                                                  |     |

| 12.6.5     | Maximum Current and Dynamic Current Considerations          | 824 |

# Intel® Ethernet Switch FM10000 Datasheet Contents

| 12.6.6    | Power Versus SKU and Table of Expected Powers             | 826 |

|-----------|-----------------------------------------------------------|-----|

| 12.6.7    | Thermal Design Power                                      | 826 |

| 12.6.8    | Package Power Delivery Network                            | 826 |

| 12.7 Pac  | kage Thermal Characteristics                              | 827 |

| 12.8 IO   | Pads                                                      | 828 |

| 12.8.1    | LVCMOS Pads                                               | 828 |

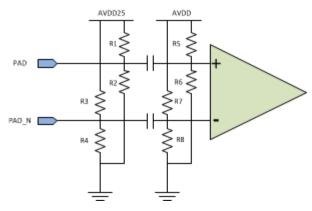

| 12.8.2    | LVPECL Pads                                               | 831 |

| 12.8.3    | Clock Observation Pads                                    | 832 |

| 12.8.4    | Thermal Monitoring Diode                                  |     |

| 12.8.5    | Thermal Monitoring Diode Characteristics                  | 833 |

| 12.9 Eth  | ernet Specifications                                      | 834 |

| 12.9.1    | Reference to Electrical Specifications of Supported Modes | 834 |

| 12.10 EPL | . RefCLK Specification                                    | 835 |

| 12.11 PCI | Express (PCIe)                                            | 835 |

| 12.11.1   | PCIe Output Specification                                 | 835 |

|           | PCIe Input Specification                                  |     |

| 12.11.3   | PCIe RefCLK Specification                                 | 835 |

| 12.12 JTA | G Interface                                               | 835 |

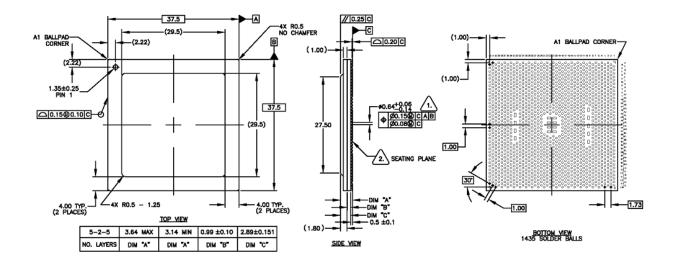

| 13.0 Mech | anical Specification                                      | 837 |

| 13.1 Des  | scription                                                 | 837 |

| 13.2 Env  | rironmental                                               | 837 |

| 13.3 Med  | chanical Drawings                                         | 838 |

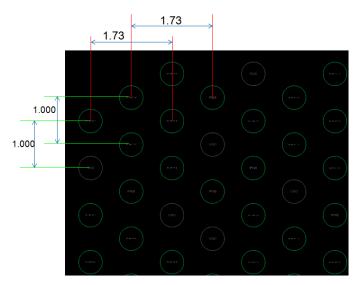

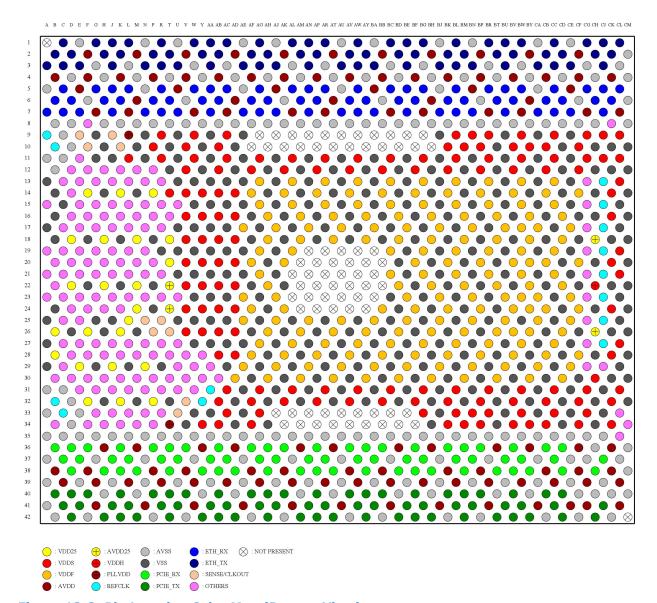

| 13.4 Pin  | Location Color Map                                        | 839 |

| 13.5 Pin  | Lists                                                     | 840 |

| 13.5.1    | Pin List Ordered by Location                              | 840 |

| 13.5.2    | Pin List Ordered by Name                                  | 850 |

| 13.5.3    | Disabled Pins on Reduced-Functionality SKUs               | 860 |

| 13.5.4    | Pin Mapping to PEP Ports per SKU                          | 864 |

NOTE: This page intentionally left blank.

## 1.0 Introduction

### 1.1 Scope

This specification defines the FM10000 architecture as well as registers definition and electrical, mechanical and thermal specifications for the product.

## 1.2 Product Applicability

The FM10000 is available in two SKUs, listed in Table 1-1.

Table 1-1 FM10000 Product SKUs

| Product | Max Ethernet Port Usage |     |     |     |       | PCIe<br>Data | Max Bandwidth (Gb/s) |                   |     |                  | Switch<br>Frequency |

|---------|-------------------------|-----|-----|-----|-------|--------------|----------------------|-------------------|-----|------------------|---------------------|

|         | 100G                    | 40G | 25G | 10G | SGMII | Ports        | Ethernet             | PCIe <sup>1</sup> | TE  | Max <sup>2</sup> | (MHz)               |

| FM10840 | 4                       | 9   | 24  | 36  | 36    | 8x4, 4x8     | 400                  | 200               | 200 | 600              | 980                 |

| FM10420 | 2                       | 2   | 8   | 8   | 8     | 4x4, 2x8     | 200                  | 100               | 200 | 400              | 600 <sup>3</sup>    |

| Product | EPL Port<br>Location             | PEP Port Location                                                         | PEP BW<br>Selection                      | Estimated WC <sup>4</sup><br>Power (W) | Use Cases                              |

|---------|----------------------------------|---------------------------------------------------------------------------|------------------------------------------|----------------------------------------|----------------------------------------|

| FM10840 | Port[035], up to 400G bandwidth. | PCIe x8: PEPs [08] are all available PCIe x4: PEPs [08] are all available | PCIe x8:<br>50/25/10/<br>2.5 per<br>port | 44.8                                   | High-performance compute fabric.       |

| FM10420 | Port[035], up to 200G bandwidth. | PCIe X8:<br>PEP [0,2]<br>PCIe X4:<br>PEP [0,1,2,3], or PEP [0,2,4,6]      | PCIe x4:<br>25/10/2.5<br>per port        | 28.3                                   | High Performance<br>10/40/100 GbE NIC. |

<sup>1.</sup> Unused PCIe bandwidth can be used for Ethernet.

333497-002

<sup>2.</sup> The total bandwidth allowed is the sum of Ethernet, PCIe, and Tunneling. The total may not exceed the Maximum for the SKU in question.

<sup>3.</sup> The default switch frequency of FM10420 at is set to 600 MHz in case 100 GbE ports are used. 600 MHz is the minimum frequency to support 100 GbE at baseline (Total Bandwidth x 1.5 + 25 MHz) requirement. The switch frequency can still be reduced to 500, 400, 300MHz if 100 GbE is not used; see PLL\_FABRIC\_LOCK. FeatureCode in Section 11.26.2.5.

<sup>4.</sup> WC = Worse Case refers to Max condition and can vary based on application (see Section 12.6.2).

The information about SKUs and default options are available from following register locations:

```

• DEVICE_CFG.FeatureCode

```

```

00b = FULL — All PEPs available (0..8)

01b = HALF — PEPs 0,1,2,3,4,6,8 can be used. Hosts 0,1,2,3 can operate in either mode.

Hosts 4 and 6 can only be used in 4-lane mode.

10b = BASIC — Only one PEP interface available (0 or 8)

11b = Reserved

```

• DEVICE CFG.Eth100GDisabled

0b = Disabled 1b = Enabled

• PLL\_FABRIC\_LOCK.FeatureCode

```

0000b = No speed restrictions

0001b = Support 600,500,400,300 MHz

0010b = Support 500,400,300 MHz

0011b = Support 400,300 MHz

0100b = Support 300 MHz

All other values are reserved.

```

• FUSE\_DATA\_0[15:11] SKU number

```

00000b = FM10840

00001b = FM10420

```

### 1.3 Document Organization

This document is organized as follows:

- Section 1.0, "Introduction"

- Section 2.0, "Architecture Overview"

- Section 3.0, "Pin Descriptions"

- Section 4.0, "Reset, Boot and Clocking"

- Section 5.0, "Ethernet Switch"

- Section 6.0, "PCIe Host Interface"

- Section 7.0, "Ethernet Port Logic (EPL)"

- Section 8.0, "Tunneling Engine"

- Section 9.0, "Peripherals"

- Section 10.0, "Reliability, Diagnostics and Testability"

- Section 11.0, "Register Definitions"

- Section 12.0, "Electrical Specification"

- Section 13.0, "Mechanical Specification"

## 1.4 Definitions

#### **Table 1-2** Terminology Definitions

| Term          | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| {A,B}         | Denotes a bit concatenation of variable A or B where A is most significant bit field and B is least significant bit field.  Note: {0,A} means that 0s are added to the left (most significant bits) to pad to the desired size while {A,0} means padded to the right.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Bit Numbering | Bit 0 is the least significant bit throughout the architecture (even if Ethernet standards and specifications suggest otherwise).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| Byte          | 8 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| Double Word   | 64 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| EBI           | External Bus Interface — Intel's term for a legacy address/data external bus interface to processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| F32/F64/F96   | Intel-proprietary inter-switch link tag, which is used to pass relevant management and control information from one Intel Ethernet and Switch Family device to another in a network. Not supported in the FM2000 series.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| FM2000        | The first generation of the Intel <sup>®</sup> Ethernet and Switch Family.  The FM2000 is a Layer 2 (L2) 10 GbE switch chip platform that forms the basis for many L2 switch product variants, including the FM2224, FM2212, FM2208, FM2112, FM2104, and FM2103.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| FM4000        | The second generation of the Intel <sup>®</sup> Ethernet and Switch Family.  The FM4000 is an enhanced multi-layer 10 GbE switch chip platform that forms the basis for new switch product variants, all of which are pin-compatible with their original FM2000 series counterparts. The FM4xxx devices are full-featured L3 routing devices, and contain other enhancements, such as ACLs, congestion management, increased frame memory and more. The FM3xxx devices are similar to the FM4xxx, except that L3 routing is not included.                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| FM5000/FM6000 | The third generation of the Intel <sup>®</sup> Ethernet and Switch Family.  The FM5000/FM6000 enhances functionality and bandwidth while providing package options that are pin compatible with the FM4000 series. The FM5000/FM6000 L2/L3/L4 devices provide advanced CEE/DCB features for the Data Center.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| FM10000       | The fourth generation of the Intel <sup>®</sup> Ethernet and Switch Family.  The Intel <sup>®</sup> FM10000 family combines integrated Ethernet controllers with an advanced Ethernet switch architecture to provide a multi-host Ethernet controller for low latency rack scale server platforms and high-performance communications infrastructure applications. The FM10000 series supports enhanced features critical for today's need for high performance environments: low latency, scalability, L3 routing, Priority Flow Control, Enhanced Transmission Selection, as well as support for VXLAN, NVGRE, EVB, NSH and software defined networking. The FM10000 series supports up to 36 10 GbE ports and the ability to group four ports as 40 GbE or 100 GbE links. Four integrated Ethernet controllers can be used as standard 50 Gb/s host interfaces, while providing low latency interfaces into the integrated Ethernet switch. |  |  |  |  |

| GENEVE        | IETF Geneve (GENEVE) is one of the three supported tunnels in the FM10000 (along with NVGRE and VXLAN). GENEVE is also known as NGE.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| GloRT         | Intel-proprietary Global Resource Tag, which is used to pass global identification information from one device to another in a network. GloRT is the proper pronunciation, although other uses might appear in the document and have the same meaning. For example, glort, GloRT or GLORT.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

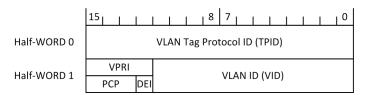

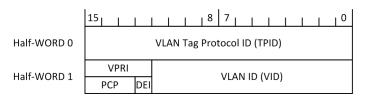

| Half Word     | 16 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| Logging       | Logging refers to a copy of the frame sent to a local CPU for monitoring purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| Mirroring     | Mirroring refers to a copy of the frame sent to another port for monitoring purposes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

333497-002

#### **Table 1-2** Terminology Definitions [Continued]

| Term                 | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Packet or Frame      | Packet — On a typical computer network, data is transmitted in the form of structured and modest-sized packets. Instead of transmitting arbitrary-length strings of data, structured packets Packet or Frame allow error checking and other relevant processing to occur on smaller easier-to-retransmit data. Packetized data also helps to alleviate traffic jams on the network when multiple nodes are contending for a shared network resource.  Frame — While a packet is a small block of data, a Frame is the definition of how packets of data are defined and transported on a specific network. When sending data over a network, both sides of the connection must agree on a common frame format (e.g., when a frame starts, when a frame ends, padding, etc.)  Combining terms, an Ethernet packet is sent onto an Ethernet interface using an Ethernet frame format.  This document uses both terms interchangeably. |  |  |  |  |

| PCI Express* (PCIe*) | PCIe Interface to a processor. Compliant to PCIe Gen3/2/1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |

| Register Type        | Registers are split into fields of the following types:  RW Read/Write  SRW Read/Write (Service reset)  RO Read-Only (This register cannot be programmed by software. Typically reports a status.)  CW Clear-on-Write (Any value written clears the register.)  CW1 Clear-on-Write-1 (Writing 1b to any bit clears that bit. Writing 0b has no effect.)  SW1 Set-on-Write-1 (Writing 1b to any bit sets that bit. Writing 0b has no effect.)  CR Clear-on-Read (Reading the register clears the register.)  RV Reserved (For upward compatibility. Always write as zero, ignore on read.)  WO Write-Only (The value written cannot be read back.)                                                                                                                                                                                                                                                                                   |  |  |  |  |

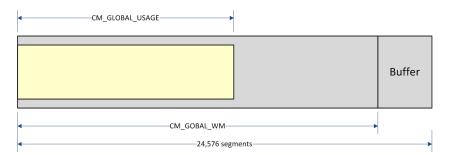

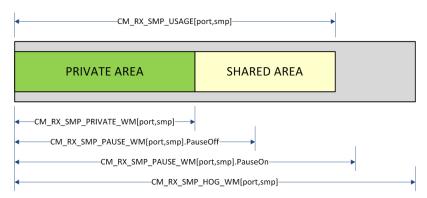

| Segment              | A portion of a packet corresponding to one of the common architecturally-significant storage and processing chunks that has been defined in the architecture. For FM10000, a segment in 192 bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| Trapping             | Trapping refers to special frames that are captured by the switch and redirected to a local CPU for processing.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| Word                 | 32 bits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| X[0N]                | Denotes an array with indexes that go from 0 through N, inclusively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| X[N:0] or X[0:N]     | Denotes a bit range within a variable. The bit range [0:N] indicates that bit 0 is the most significant, while bit range [N:0] indicates that the bit 0 is the least significant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

## 2.0 Architecture Overview

#### 2.1 Overview

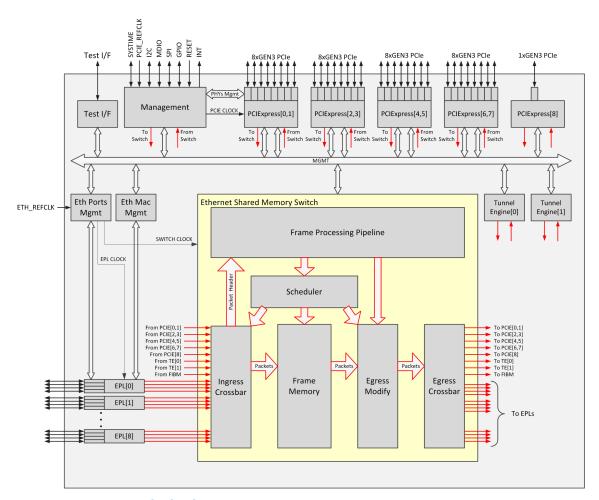

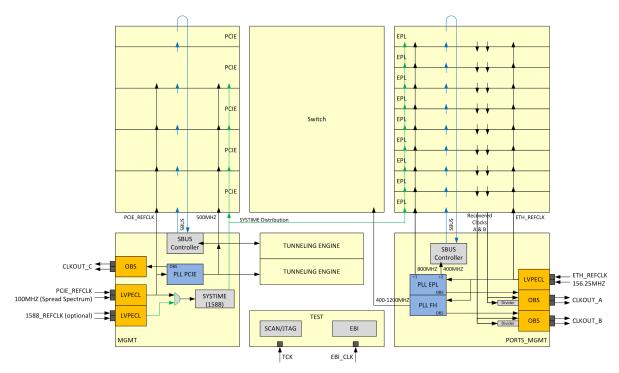

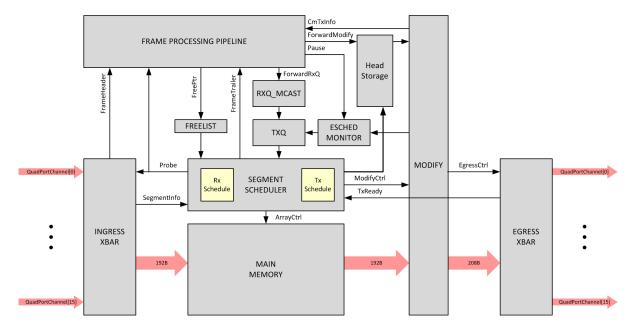

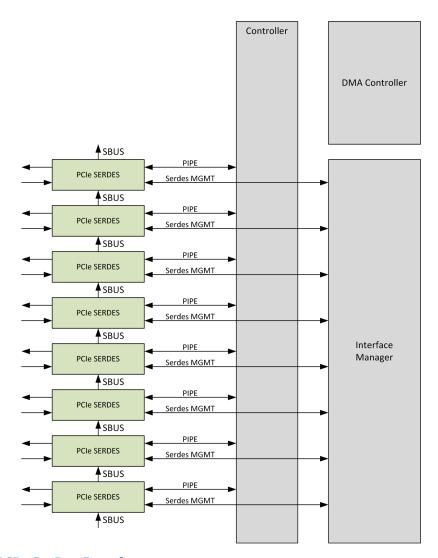

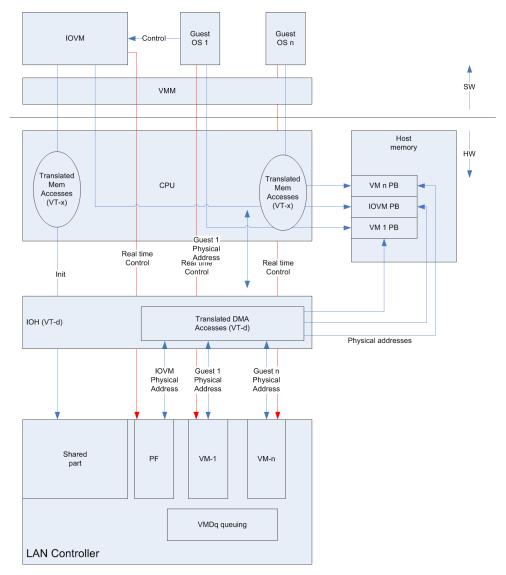

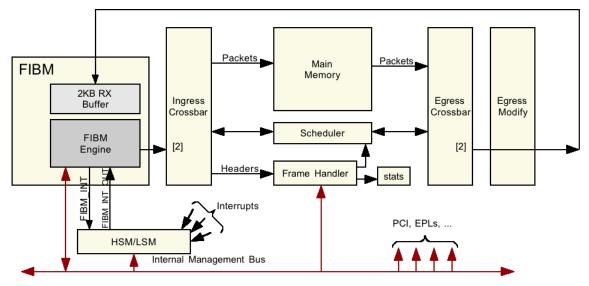

The FM10000 is a 48-port (36 Ethernet, 9 PCIe, 2 Tunneling Engines and one FBIM) Ethernet switch based on a shared memory fabric architecture supporting Ethernet ports and PCI Express (PCIe) host interfaces. Figure 2-1 shows the main elements of the device.

Figure 2-1 FM10000 Block Diagram

333497-002 17

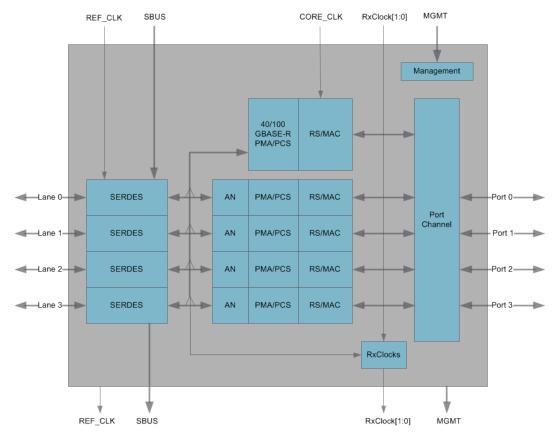

The Ethernet Port Logic (EPL) are the actual Ethernet interfaces. The FM10000 supports nine EPLs which have 4 SerDes each for a total of 36 external ports. Each SerDes is capable of supporting rates from 1.25 GbE to 25.78125 GbE and could be used to support either four independent ports each running at their own speed (1 GbE, 2.5 GbE, 10 GbE or 25 GbE) or a combination of four SerDes in one logical port (40 GbE, 100 GbE). The EPL contains the PCS and MAC layers to serialize or deserialize data frames.

The Ports Mgmt is a block acting as a bridge to manage the SerDes on the Ethernet ports. This block also includes the PLLs to generate the clocks for EPL and the Ethernet Shared Memory Switch and clock observations outputs.

The Ethernet Shared Memory Switch is the core component of the device and is responsible to switch frames between ports; all ports are equivalent from a switch perspective, external (Ethernet) or internals (PCIe, FIBM). The fabric includes the following components:

- · Ingress crossbar

- · Main memory

- Egress modification

- · Egress crossbar

- Scheduler

- · Frame processing pipeline

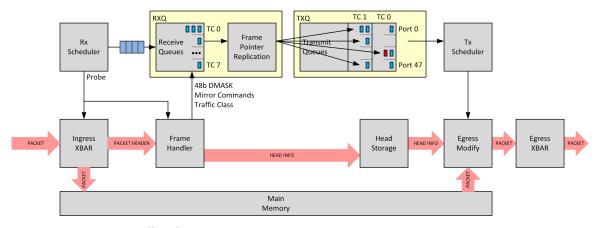

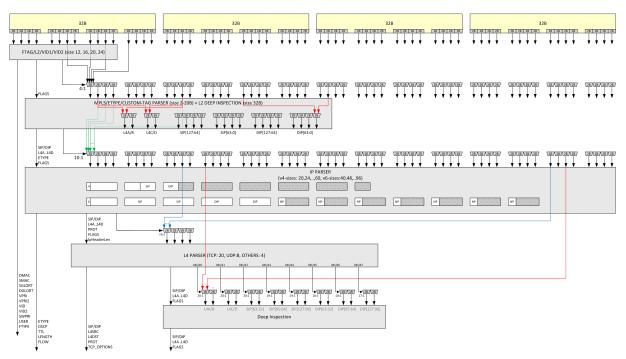

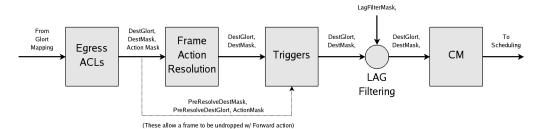

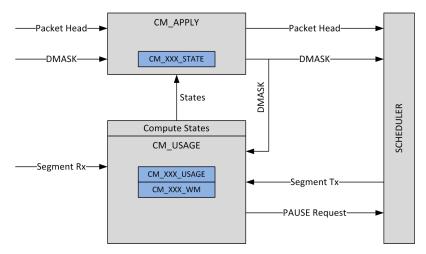

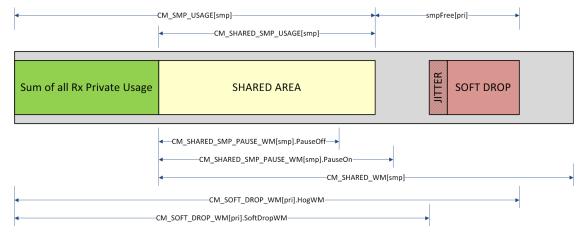

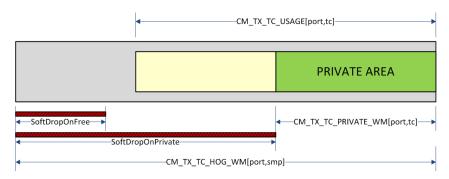

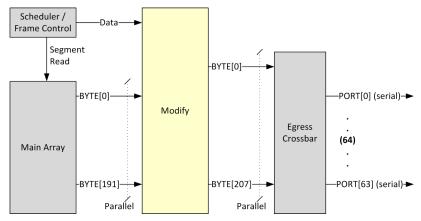

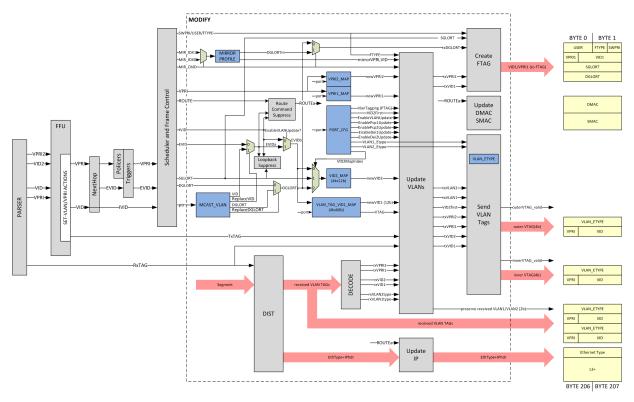

Data frames incoming into the switch are fragmented into segments of up to 192 bytes which are stored in memory by the ingress crossbar. The scheduler responsibilities are to manage the segment pool, send commands to the ingress and egress crossbars to get segments into memory or out of memory, reports arrival of segments or frame processing pipeline and schedule frames transmission according to priorities and shaping profiles programmed. The scheduler also instructs the ingress crossbar to send the first segment of the frame to the frame processing pipeline for a switching decision.

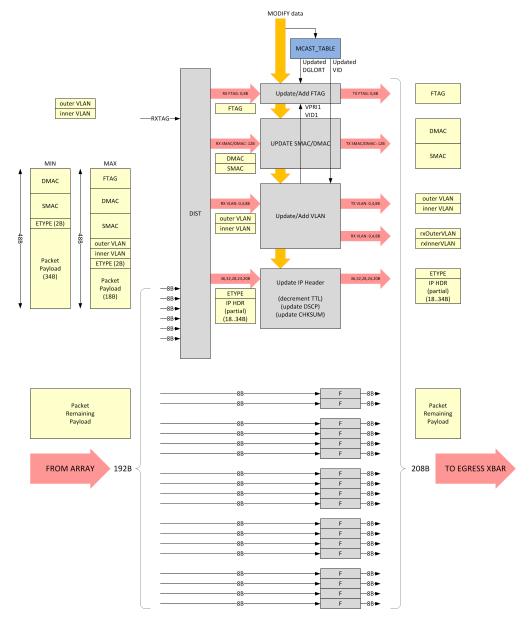

The frame processing pipeline responsibilities are to parse the frame headers and do necessary table lookups to determine the set of ports the frame is sent to. The forwarding decision is forwarded to the scheduler, and new data generated for this new frame is forwarded to the MODIFY unit. The frame processing pipeline also keeps track of segments consumed on ingress or freed on egress for accounting purposes.

The MODIFY unit is instructed by the scheduler of segment transmission, and applies the necessary transforms on the first segment of the frame using information stored for that frame which was supplied earlier by the frame processing pipeline. Modifications could include, for example, modifying a VLAN tag or routing the frame.

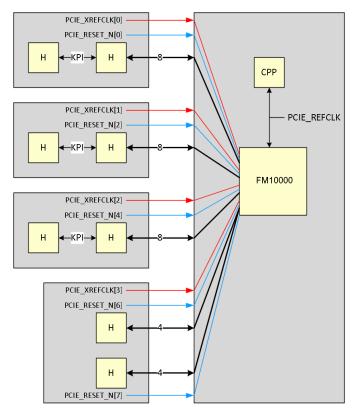

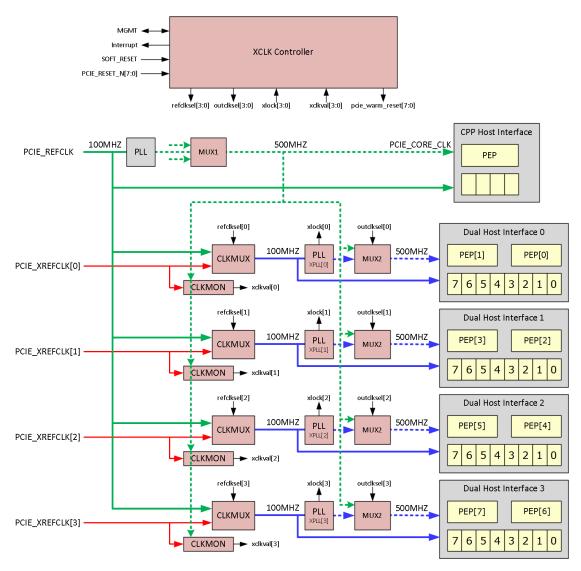

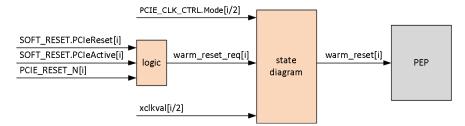

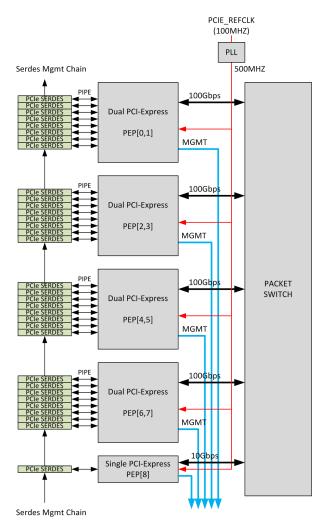

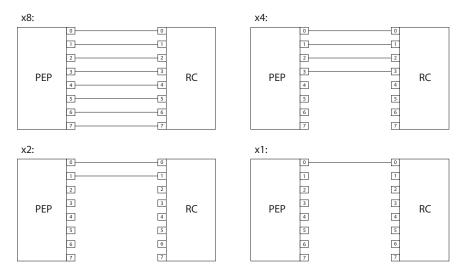

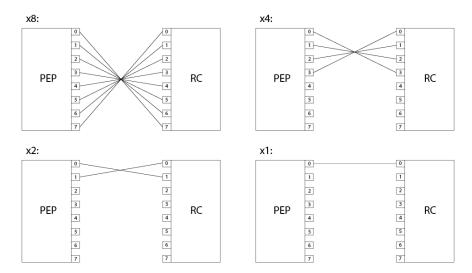

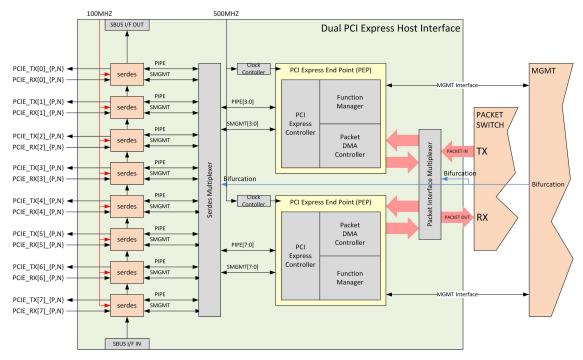

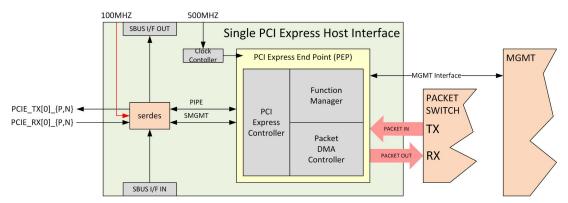

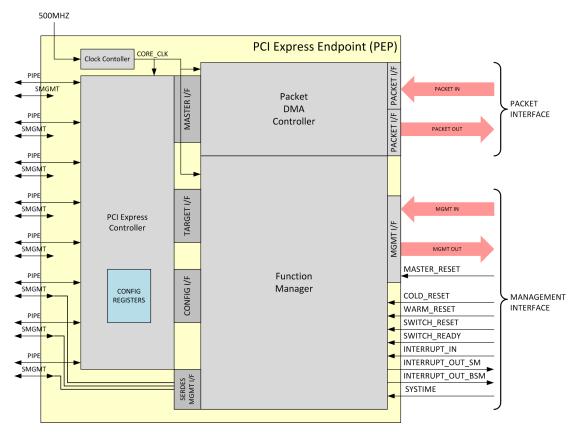

The PCIe Host Interfaces are the network interfaces between hosts and the switch. They include the necessary DMA engines to efficiently transfer frames from host to switch or from switch to host. The FM10000 supports five Host Interfaces. The first four contain two PCIe End Points (PEPs) and could operate either in 2x4 lane mode (both PEPs active) or in 1x8 lane mode (one PEP active, one PEP down). The last interface contains one PCIe End Point and only one lane.

The FM10000 could be controlled through various management interfaces:

- PCIe End Points (PEP)

- FTAG In-Band Management (FIBM)

- Low-speed Management (LSM)

- Test Interface

The primary management interfaces are the PCIe End Points (PEPs), which can be used to manage the switch and also can be used to transmit frames from the attached hosts to the fabric or to receive frames from the fabric. From a fabric perspective, the PEP are not different than an Ethernet port and thus frames from/to PCIe are switched the same way as any other frame. Each of the PCIe host interface supports 8 lanes and is v3.0 compliant (a.k.a. GEN3).

A secondary management interface is the in-band-management which is a unit designed to interpret and respond to specialized formatted Ethernet frames to read or write internal registers in the switch remotely. This management interface is connected to the fabric allowing receiving and sending FIBM frames from any port.

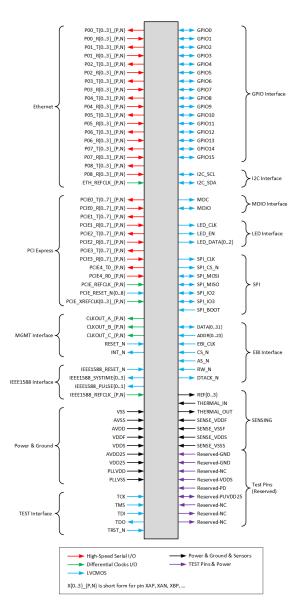

Finally, the FM10000 also supports a set of slower speed interfaces grouped into two blocks; low-speed management and test interface. The test interface includes a 33 MHz address/data bus and a scan infrastructure used by production. The low-speed management block includes an I<sup>2</sup>C interface, a JTAG interface, an internal monitoring interface, SPI interface, an MDIO interface, a LED interface and a GPIO interface. The low-speed management is also responsible to handle reference clocks, generate internal high speed clocks and implement reset control, watchdogs and boot.

## 2.2 Management Overview

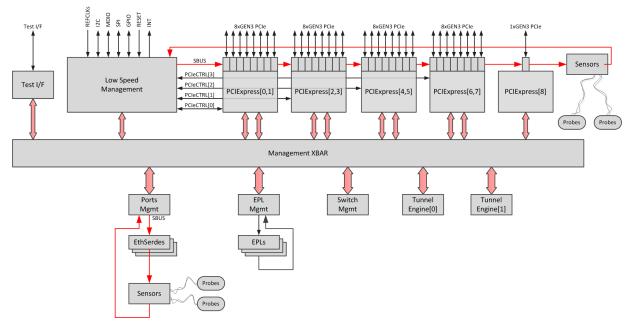

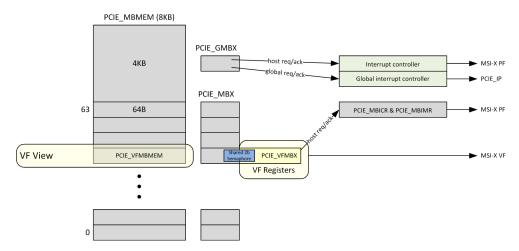

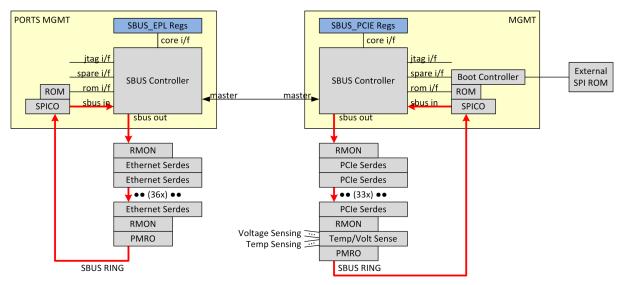

The management infrastructure is shown in Figure 2-2.

Figure 2-2 Management Overview Block Diagram

333497-002

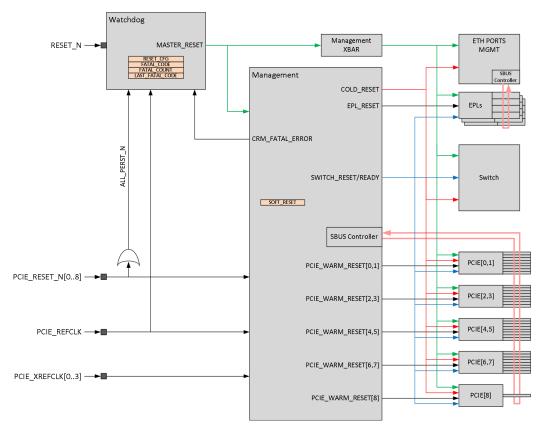

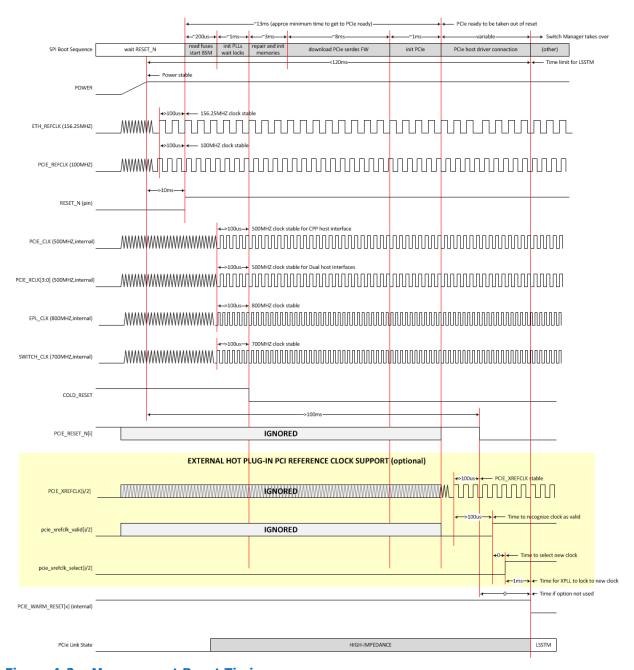

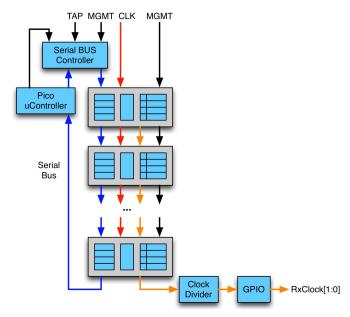

The Low-Speed-Management (LSM) is the first unit to come out of reset and is responsible for booting the device. The LSM normally retrieves a configuration from a serial FLASH memory to setup the device initially. This configuration could be minimal or exhaustive depending of the desired mode of operation. As a example, a minimum configuration could be to configure the internal PLLS to provide necessary clocks to the system, configure a set of PCIe SerDes and take one PCIe interface out of reset, thus allowing a host connected on PCIe to take over. The details on LSM are covered in the Low-Speed Management chapter. The LSM also extends itself to provide a serial bus (SBUS) interface that daisy chains all PCIe SerDes and also access to sensors which are attached to probes inside the chip. The LSM include also the FIBM which provides an Ethernet frame-based method to manage the device.

The Test Interface (TEST) is also immediately available after reset and provides an interface for testing purpose. The Test Interface is not intended to be used in normal applications.

The PCIe interfaces are the usual interfaces to manage the device.

All these management interfaces (9xPCIe, 1xLSM, 1xTEST) could initiate read/write requests to any register in the switch. The central management crossbar is the unit that arbitrates the access from each initiator to each target. There are 14 targets:

- LSM/FIBM

- EPLs/Ports Management

- 9 x PCIe

- 2 x Tunnel Engines

- Switch

The Switch, Tunnels, and EPLs and Ports management interfaces are targets only and are used to access registers and tables in the switch and tunnel engines, registers in EPLs and registers in Ports management as well as Ethernet SerDes (Ethernet SerDes accessible via an SBUS).

The switch, EPLs, tunnels could receive transactions from any master and up to the 11 possible masters. The master interfaces however have more limited capabilities as targets; the TEST is never a target, the LSM supports only up to 3 requests at any time and the PCIe supports up to 8.

The transactions on the crossbar are simple:

- Read request

- · Write request

- Read response

The ordering of read/write requests, and of read responses, between a master and a target is always maintained. All transactions on the crossbar are in 32-bit data words; no byte or half-word accesses are supported.

### 2.2.1 Access to 64-bit or 128-bit Registers

Some registers in the system are larger than 32 bits (either 64 or 128 bits), and the read/write of those registers is done atomically. It is expected that a given initiator writes or reads all the words of the register in increasing address order (from least to most significant 32-bit word), without interleaving other management access. If the host follows that pattern, the mechanism below guarantees that the hardware register access is atomic.

To ensure atomic access during write accesses, each target keeps a scratch register per initiator, to store all but the most significant word written from that initiator for registers larger than 32 bits. The target performs the actual atomic write at the designated register address when the most significant word of the register is written, using the scratch register for that initiator to provide the lower significant words. The write address of the most significant word is used to determine the address of the overall atomic write.

Similarly, on read, the target keeps local scratch read registers per initiator, holding address and data of larger-than-32-bit register. When the initiator first reads any word of a register, the target reads the register atomically, stores its address and data into this scratch register and returns the content of the word addressed to the initiator. Successive word reads on the same register returns the content of the scratch register as long as it is not the first word of the register. Reads of the least significant word or reads on a different register cause the scratch register content to be refreshed by the target redoing an atomic read.

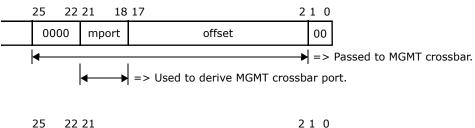

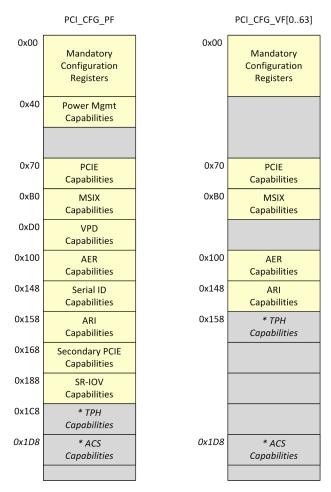

#### 2.2.2 Global Register Space

The global register space is defined as follows (in 32-bit words):

```

2.3

00000000_xxxxxxxxx_xxxxxxxx 64KW => LSM/FIBM

00000001_xxxxxxxx_xxxxxxx \

> 13*64KW => Do not access

00001101 xxxxxxx xxxxxxx /

(TEST is at 0x0DXXXX)

00001110 0xxxxxxxxxxxx 32KW => EPLs

00001110 1xxxxxxx xxxxxxx 32KW => PORTS MGMT

00001111 xxxxxxxx xxxxxxx 64KW => Do not access

|0000port|

+---> The four bits [19:16] is the management crossbar port if

top four bits are zero.

1MW => GLOBAL PCI EXPRESS[0]

1MW => GLOBAL PCT EXPRESS[1

1MW => GLOBAL PCI EXPRESS[3]

1MW => GLOBAL PCI EXPRESS[4]

1MW => GLOBAL PCI EXPRESS

1MW => GLOBAL PCI EXPRESS[6]

1MW => GLOBAL PCI EXPRESS[7]

1MW => GLOBAL PCI EXPRESS[8]

0110xxxx xxxxxxx xxxxxxx

1MW => TUNNEL ENGINE[0]

+---> The top four bits is the management crossbar port

except for 0,12,13,14,15.

11xxxxxx xxxxxxxx xxxxxxxx 4MW => Ethernet Shared Memory Switch

+---> Mapped to crossbar port #15.

```

333497-002 21

### 2.2.3 Inactive or Non-existent Registers

Management read or write requests should not be made to the address ranges 0x010000-0x0DFFFF or 0x0F0000-0x0FFFFF, marked as "Do not access" in the table above. Also, when a PCIe host interface is disabled, as indicated by the DEVICE\_CFG.PCIeEnable[i] configuration bit, management read or write requests must not be made to any address in its address space, shown as the GLOBAL PCI EXPRESS[i] space in the definition presented in Section 2.2.2. Violating either of these rules can lead to deadlock of the management infrastructure.

Aside from the above restrictions, a master can read at any address. The read request completes successfully, even if there are no registers or tables defined for this address. A read from the address space of a unit in reset always returns zero. The returned value for non-existing registers is undefined, but usually zero.

A master always writes to existing registers or tables. The behavior of the hardware is not defined if software attempts to write to an address for which no registers or tables exist. Writing to the address space of a unit in reset has no effect.

## 2.3 Switch Aggregation and Frame Tagging

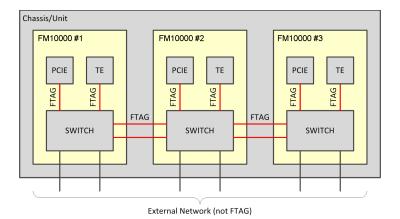

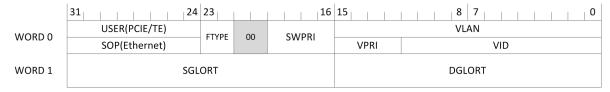

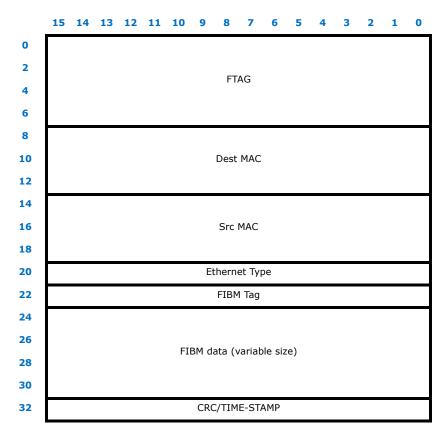

The FM10000 supports the addition of a Fabric Tag (FTAG) to carry special information from Switch to Switch, between Switch and PCIe Host Interface or between Switch and Tunneling Engines. This tag is essential for a set of switches to behave like one switch (switch aggregation). Figure 2-3 shows where FTAG is normally used.

Figure 2-3 FTAG Usage

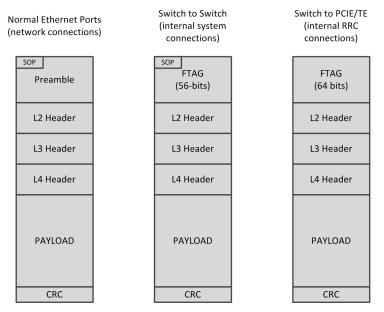

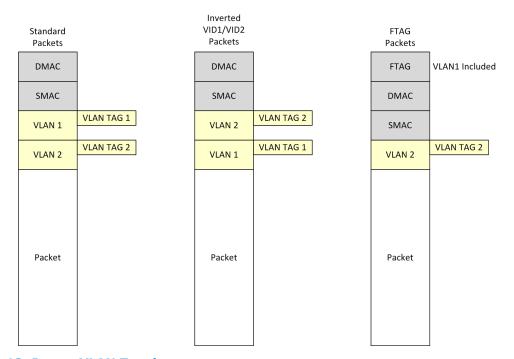

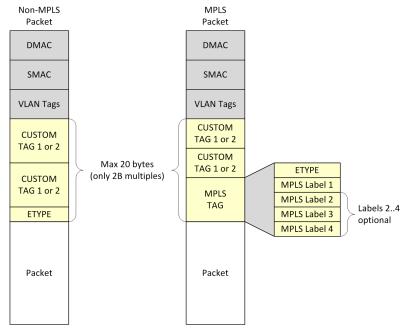

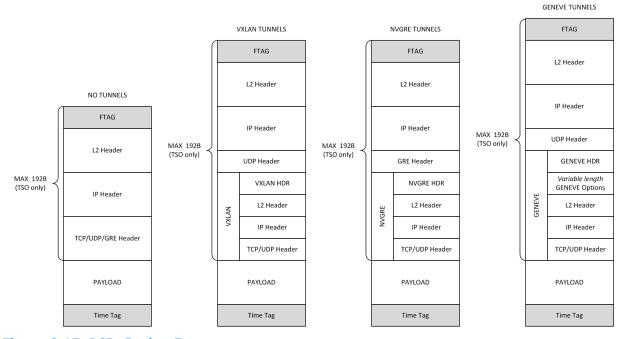

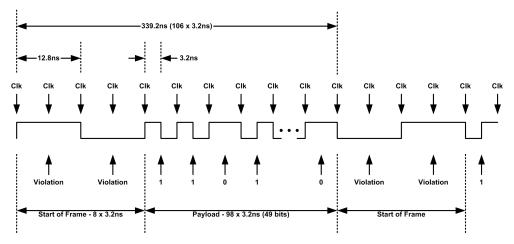

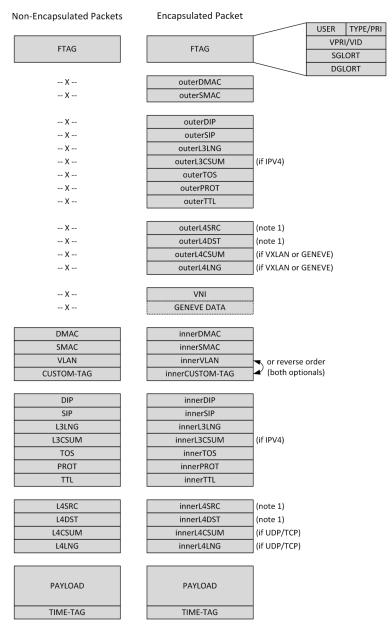

The FTAG is placed at the beginning of the frame. The Ethernet frame preamble is re-used to carry this tag for Ethernet ports avoiding using extra bandwidth. It is simply added at the beginning of the frame for PCIe Host Interfaces and Tunneling Engines. Figure 2-4 shows the different cases.

Figure 2-4 Frame Tagging

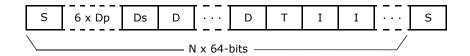

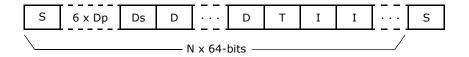

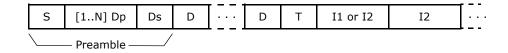

There are two formats for the FTAG. The first format is on Ethernet ports for Switch to Switch, the second format is used for frames between the PCI Express Host Interfaces or Tunneling Engines and the Switch function. The only difference is the USER field, which is not available on Ethernet ports.

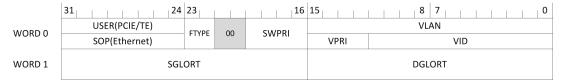

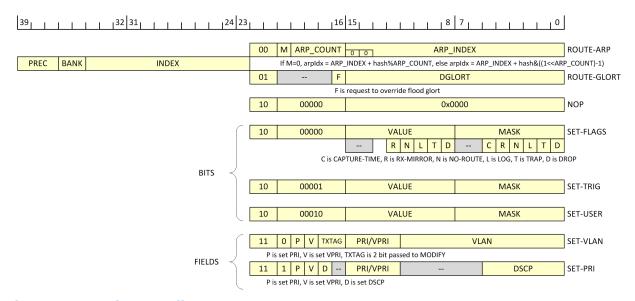

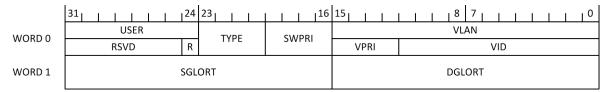

Figure 2-5 FTAG Format

The presence of FTAG on Ethernet port is configured on a per port basis, and are only set on secure links for switch to switch intercommunication. If enabled, all frames on this port gets an FTAG.

The FTAG contains the following fields:

- USER (8 bits) General purpose 8-bit field.

- FTYPE (2 bits) Frame type.

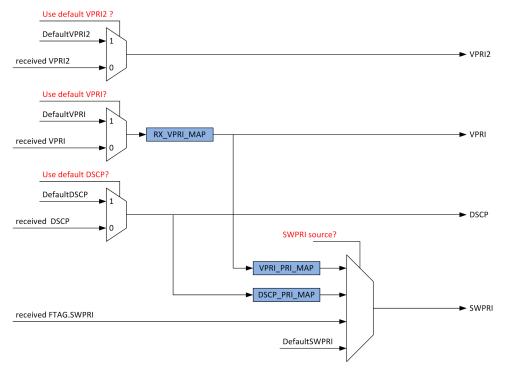

- SWPRI (4 bits) Assigned frame switch priority.