# Intel<sup>®</sup> Xeon<sup>®</sup> D-1500/D-1500 NS and Intel<sup>®</sup> Xeon<sup>®</sup> D-1600 NS Processor Families

**Specification Update**

May 2020

Reference Number: 332054-022US

Intel technologies features and benefits depend on system configuration and may require enabled hardware, software, or service activation. Learn more at intel.com, or from the OEM or retailer.

No computer system can be absolutely secure. Intel does not assume any liability for lost or stolen data or systems or any damages resulting from such losses.

You may not use or facilitate the use of this document in connection with any infringement or other legal analysis concerning Intel products described herein. You agree to grant Intel a non-exclusive, royalty-free license to any patent claim thereafter drafted which includes subject matter disclosed herein.

No license (express or implied, by estoppel or otherwise) to any intellectual property rights is granted by this document. The products described may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Intel disclaims all express and implied warranties, including without limitation, the implied warranties of merchantability, fitness for a particular purpose, and non-infringement, as well as any warranty arising from course of performance, course of dealing, or usage in trade.

Copies of documents which have an order number and are referenced in this document may be obtained by calling 1-800-548-4725 or by visiting www.intel.com/design/literature.htm.

Intel, the Intel logo, Intel Core, Pentium, and Xeon are trademarks of Intel Corporation in the U.S. and/or other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2020, Intel Corporation. All Rights Reserved.

# Contents

| Revision History                                           | 4  |

|------------------------------------------------------------|----|

| Preface                                                    | 5  |

| Identification Information                                 | 7  |

| Summary Tables of Changes                                  | 9  |

| Intel <sup>®</sup> Xeon <sup>®</sup> D-1500 Product Family | 10 |

| Integrated Core/Uncore Errata                              | 15 |

| LAN Specific Sightings                                     | 42 |

| Integrated PCH Sightings                                   | 45 |

| Documentation Changes                                      | 55 |

§

# (intel) Revision History

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Date          |  |  |  |  |  |  |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--|--|--|--|--|--|

| 022      | Added BDE121                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | May 2020      |  |  |  |  |  |  |

| 021      | Added Note 5 to documentation changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | March 2020    |  |  |  |  |  |  |

| 020      | Added PCH27. Updated PCH25<br>Updated wording for BDE21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |               |  |  |  |  |  |  |

| 019      | Added BDE118, BDE119 and BDE120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | August 2019   |  |  |  |  |  |  |

| 018      | Added BDE117 updated Table 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | May 2019      |  |  |  |  |  |  |

| 017      | Added BDE115 and BDE116.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | March 2019    |  |  |  |  |  |  |

| 016      | Corrected impacted steppings of BDE41.<br>Added BDE114.<br>Added SKU R2DH to table 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | February 2018 |  |  |  |  |  |  |

| 015      | Corrected workaround for BDE94 and BDE113.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | November 2017 |  |  |  |  |  |  |

| 014      | Added Intel <sup>®</sup> Xeon <sup>®</sup> D-1500 NS Processor Family.<br>Added Erratum BDE111 through BDE113.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | September 201 |  |  |  |  |  |  |

| 013      | Added Intel <sup>®</sup> Xeon <sup>®</sup> D-1500 NS Processor Family.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | July 2017     |  |  |  |  |  |  |

| 012      | Corrected Erratum BDE109.<br>Added Erratum BDE110.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | February 2017 |  |  |  |  |  |  |

| 011      | Deleted Errata BDE30 and BDE42 since they do not apply to this product.<br>Deleted erratum BDE64 as it was a duplicate of BDE55.<br>Fixed title of Erratum BDE94 in Table 2.<br>Corrected status of BDE49 in Table 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | February 2017 |  |  |  |  |  |  |

| 010      | Added Erratum:BDE109                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | January 2017  |  |  |  |  |  |  |

| 009      | Added Errata: BDE104, BDE105, BDE106, BDE107, BDE108                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | December 2016 |  |  |  |  |  |  |

| 008      | Added Erratum: BDE94, BDE95, BDE96, BDE97, BDE98, BDE99, BDE100, BDE101, BDE102, BDE103, PCH26<br>Modified Erratum: BDE71, PCH25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | November 2016 |  |  |  |  |  |  |

| 007      | Added Errata: BDE92, BDE93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | October 2016  |  |  |  |  |  |  |

| 006      | Added Errata: BDE72, BDE73, BDE74, BDE75, BDE76, BDE77, BDE78, BDE79, BDE80, BDE81, BDE82, BDE83, BDE84, BDE85, BDE86, BDE87, BDE88, BDE89, BDE90, BDE91, LAN5, LAN6,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |  |  |  |  |  |  |

| 005      | Added Errata BDE71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | February 2016 |  |  |  |  |  |  |

| 004      | Added Errata BDE66, BDE67, BDE68, BDE69, BDE70, PCH1, PCH2, PCH3, PCH4, PCH5, PCH6, PCH7, PCH8, PCH9, PCH10, PCH11, PCH12, PCH13, PCH14, PCH15, PCH16, PCH5, PCH16, PCH16, PCH16, PCH16, PCH17, |               |  |  |  |  |  |  |

| 003      | Added Errata BDE54, BDE55, BDE56, BDE57, BDE58, BDE59, BDE60, BDE61, BDE62, BDE63, BDE64, BDE65, LAN1, LAN2, LAN3, LAN4, Modified Errata: BDE58, BDE59                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | November 201  |  |  |  |  |  |  |

| 002      | Added Errata BDE60,BDE61, BDE62 and BDE63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | July 2015     |  |  |  |  |  |  |

| 001      | Initial Release                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | May 2015      |  |  |  |  |  |  |

# Preface

This document is an update to the specifications contained in the Affected Documents table below. This document is a compilation of device and documentation errata, specification clarifications and changes. It is intended for hardware system manufacturers and software developers of applications, operating systems, or tools.

Information types defined in Nomenclature are consolidated into the specification update and are no longer published in other documents.

This document may also contain information that was not previously published.

## **Affected Documents**

| Document Title                                                                                                     | Document<br>Number/Location |

|--------------------------------------------------------------------------------------------------------------------|-----------------------------|

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Datasheet Volume One                          | 332050                      |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Datasheet Volume Two                          | 332051                      |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Datasheet Volume Three                        | 332052                      |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Datasheet Volume Four                         | 332053                      |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Thermal Mechanical Specification Design Guide | 332055                      |

| Intel <sup>®</sup> Xeon <sup>®</sup> Processor D-1500 Product Family Boundary Scan Description Language (BSDL)     | 332056                      |

## Nomenclature

**Errata** are design defects or errors. These may cause the SoC's behavior to deviate from published specifications. Hardware and software designed to be used with any given stepping must assume that all errata documented for that stepping are present on all devices.

**Specification Changes** are modifications to the current published specifications. These changes will be incorporated in any new release of the specification.

**Specification Clarifications** describe a specification in greater detail or further highlight a specification's impact to a complex design situation. These clarifications will be incorporated in any new release of the specification.

**Documentation Changes** include typos, errors, or omissions from the current published specifications. These will be incorporated in any new release of the specification.

**Note:** Errata remain in the specification update throughout the product's lifecycle, or until a particular stepping is no longer commercially available. Under these circumstances, errata removed from the specification update are archived and available upon request. Specification changes, specification clarifications and documentation changes are removed from the specification update when the appropriate changes are made to the appropriate product specification or user documentation (datasheets, manuals, and so forth).

# **Identification Information**

# **Component Identification via Programming Interface**

The Intel  $^{\ensuremath{\mathbb{R}}}$  Xeon  $^{\ensuremath{\mathbb{R}}}$  D-1500 Processor stepping can be identified by the following register contents:

| Reserved | Extended<br>Family <sup>1</sup> | Extended<br>Model <sup>2</sup> | Reserved | Processor<br>Type <sup>3</sup> | Family<br>Code <sup>4</sup> | Model<br>Number <sup>5</sup> | Stepping<br>ID <sup>7</sup> |

|----------|---------------------------------|--------------------------------|----------|--------------------------------|-----------------------------|------------------------------|-----------------------------|

| 31:28    | 27:20                           | 19:16                          | 15:14    | 13:12                          | 11:8                        | 7:4                          | 3:0                         |

|          | 0000000b                        | 0101b                          |          | 00b                            | 0110b                       | 0110b                        | V1=0010b                    |

|          | 0000000b                        | 0101b                          |          | 00b                            | 0110b                       | 0110b                        | V2=0011b                    |

|          | 0000000b                        | 0101b                          |          | 00b                            | 0110b                       | 0110b                        | Y0=0100b                    |

|          | 0000000b                        | 0101b                          |          | 00b                            | 0110b                       | 0110b                        | A1 <sup>6</sup> =0101b      |

#### Notes:

- The Extended Family, Bits [27:20] are used in conjunction with the Family Code, specified in Bits [11:8], to indicate whether the processor belongs to the Intel386<sup>™</sup>, Intel486<sup>™</sup>, Pentium<sup>®</sup>, Pentium 4, or Intel<sup>®</sup> Core<sup>™</sup> processor family.

- The Extended Model, Bits [19:16] in conjunction with the Model Number, specified in Bits [7:4], are used to identify the model of the processor within the processor's family.

The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register

- 3. The Family Code corresponds to Bits [11:8] of the EDX register after RESET, Bits [11:8] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the generation field of the Device ID register accessible through Boundary Scan.

- 4. The Model Number corresponds to Bits [7:4] of the EDX register after RESET, Bits [7:4] of the EAX register after the CPUID instruction is executed with a 1 in the EAX register, and the model field of the Device ID register accessible through Boundary Scan.

- The Stepping ID in Bits [3:0] indicates the revision number of that model. See Table 1 for the processor stepping ID number in the CPUID information.

- 6. This is a D-1500N Family stepping.

When EAX is initialized to a value of '1', the CPUID instruction returns the *Extended Family, Extended Model, Processor Type, Family Code, Model Number and Stepping ID* value in the EAX register. Note that the EDX processor signature value after reset is equivalent to the processor signature output value in the EAX register.

Cache and TLB descriptor parameters are provided in the EAX, EBX, ECX and EDX registers after the CPUID instruction is executed with a 2 in the EAX register.

|                       |         |             |                      | CAPID4 (Chop) |   |   |                          | CAPID1 (Sub-stepping) | CAPID0 (Segment) |   |   |   |   |   |

|-----------------------|---------|-------------|----------------------|---------------|---|---|--------------------------|-----------------------|------------------|---|---|---|---|---|

| Core<br>Chop Stepping | Package | GPUID       | B:1, D:30F:3, Off:94 |               |   |   | B:1, D:30<br>F:3, Off:88 | B:1, D:30F:3, Off:84  |                  |   |   |   |   |   |

|                       |         |             |                      | Bit           | 8 | 1 | 6                        | 20                    | 5                | 4 | 3 | 2 | 1 | 0 |

|                       | VO      | Microserver | 0x50662              |               | 1 | 0 | 0                        | 0                     | 1                | 0 | 0 | 0 | 0 | 0 |

| LCC                   | V1      | Microserver | 0x50662              | 1             | 1 | 0 | 0                        | 1                     | 1                | 0 | 0 | 0 | 0 | 0 |

|                       | V2      | Microserver | 0x50663              |               | 1 | 0 | 0                        | 0                     | 1                | 0 | 0 | 0 | 0 | 0 |

| HCC                   | YO      | Microserver | 0x50664              |               | 1 | 0 | 1                        | 0                     | 1                | 0 | 0 | 0 | 0 | 0 |

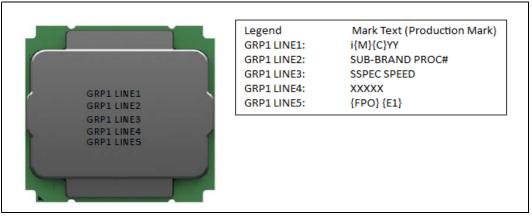

# **Component Marking Information**

# Figure 1. Intel<sup>®</sup> Xeon<sup>®</sup> D-1500 Processor Families Top-Side Markings (Example)

For the Intel® Xeon® D-1500 / D-1500 NS / D-1600 NS Processor Families SKUs, see https://ark.intel.com/content/www/us/en/ark/products/series/87041/intel-xeon-dprocessor.html

# **Summary Tables of Changes**

The following tables indicate the errata, specification changes, specification clarifications, or documentation changes which apply to the  $Intel^{(R)}$  Xeon<sup>(R)</sup> D-1500 Processor. Intel may fix some of the errata in a future stepping of the component, and account for the other outstanding issues through documentation or specification changes as noted. These tables uses the following notations:

## **Codes Used in Summary Tables**

## Stepping

|        | X:              | Errata exists in the stepping indicated. Specification Change or Clarification that applies to this stepping. |

|--------|-----------------|---------------------------------------------------------------------------------------------------------------|

|        | (No mark)       |                                                                                                               |

|        | or (Blank box): | This erratum is fixed in listed stepping or specification change does not apply to listed stepping.           |

| Page   |                 |                                                                                                               |

|        | (Page):         | Page location of item in this document.                                                                       |

| Status |                 |                                                                                                               |

|        | Doc:            | Document change or update will be implemented.                                                                |

|        | Plan Fix:       | This erratum may be fixed in a future stepping of the product.                                                |

|        | Fixed:          | This erratum has been previously fixed.                                                                       |

|        | No Fix:         | There are no plans to fix this erratum.                                                                       |

| Row    |                 |                                                                                                               |

Change bar to left of table row indicates this erratum is either new or modified from the previous version of the document.

# (intel<sup>®</sup>) Intel<sup>®</sup> Xeon<sup>®</sup> D-1500 Product Family

| Number | Steppings |    |       |   | Chattar | 500.000                                                                                                                        |

|--------|-----------|----|-------|---|---------|--------------------------------------------------------------------------------------------------------------------------------|

| Number | V1        | V2 | Y0 A1 |   | Status  | ERRATA                                                                                                                         |

| BDE1   | Х         | Х  | х     | Х | No Fix  | $Intel^{\textcircled{M}}$ Quick Data Technology DMA Incorrectly Indicates Support For RAID5 And RAID6                          |

| BDE2   | Х         | Х  | х     | Х | No Fix  | Intel <sup>®</sup> QuickData Technology End Point Does Not Implement Link Capabilities, Link Control, or Link Status Registers |

| BDE3   | Х         | Х  | Х     | Х | No Fix  | PCIe* Header of a Malformed TLP is Logged Incorrectly                                                                          |

| BDE4   | Х         | Х  | Х     | Х | No Fix  | A Malformed TLP May Block ECRC Error Logging                                                                                   |

| BDE5   | Х         | Х  |       |   | Fixed   | Integrated COM Port Interrupt Signaling Not Compatible With The 8259 Implementation                                            |

| BDE6   | Х         | Х  | Х     | Х | No Fix  | Intel <sup>®</sup> QuickData Technology DMA Devices Do Not Support Uncorrectable and<br>Correctable Error Detect Mask CSRs     |

| BDE7   | Х         | Х  | Х     | х | No Fix  | Attempting to Enter ADR May Lead to Unpredictable System<br>Behavior                                                           |

| BDE8   | Х         | Х  | Х     |   | No Fix  | Exiting From PC3 or PC6 With DDR4-2133 May Lead to<br>Unpredictable System Behavior                                            |

| BDE9   | Х         |    |       |   | Fixed   | The System May Shut Down Unexpectedly During a Warm Reset                                                                      |

| BDE10  | Х         | Х  | Х     | Х | No Fix  | CAT May Not Behave as Expected                                                                                                 |

| BDE11  | Х         | Х  | Х     | Х | No Fix  | Intel <sup>®</sup> QuickData Technology DMA Devices Do Not Support Uncorrectable and<br>Correctable Error Detect Mask CSRs     |

| BDE12  | Х         | Х  | Х     | Х | No Fix  | EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a Translation Change                                       |

| BDE13  | Х         | Х  | Х     | Х | No Fix  | MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB Error                                            |

| BDE14  | Х         | Х  | Х     | Х | No Fix  | LER MSRs May Be Unreliable                                                                                                     |

| BDE15  | Х         | Х  | Х     | Х | No Fix  | MONITOR or CLFLUSH on the Local XAPIC's Address Space Results in<br>Hang                                                       |

| BDE16  | Х         | Х  | Х     | х | No Fix  | #GP on Segment Selector Descriptor that Straddles Canonical<br>Boundary May Not Provide Correct Exception Error Code           |

| BDE17  | Х         | Х  | Х     | х | No Fix  | FREEZE_WHILE_SMM Does Not Prevent Event From Pending<br>PEBS During SMM                                                        |

| BDE18  | Х         | Х  | Х     | х | No Fix  | Advanced Programmable Interrupt Controller (APIC) Error "Received<br>Illegal Vector" May be Lost                               |

| BDE19  | Х         | Х  | Х     | х | No Fix  | Performance Monitor Precise Instruction Retired Event May Present Wrong Indications                                            |

| BDE20  | Х         | Х  | Х     | Х | No Fix  | CR0.CD Is Ignored in VMX Operation                                                                                             |

| BDE21  | Х         | Х  | Х     | Х | No Fix  | Instruction Fetch May Cause Machine Check if Page Size Was<br>Changed Without Invalidation                                     |

| BDE22  | Х         | Х  | Х     | Х | No Fix  | Execution of VAESIMC or VAESKEYGENASSIST With An Illegal Value for VEX.vvvv May Produce a #NM Exception                        |

| BDE23  | Х         | Х  | х     | Х | No Fix  | Interrupt From Local APIC Timer May Not Be Detectable While Being Delivered                                                    |

| BDE24  | Х         | Х  | х     | Х | No Fix  | Pending x87 FPU Exceptions (#MF) May be Signaled Earlier Than Expected                                                         |

| BDE25  | Х         | Х  | Х     | х | No Fix  | DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/<br>POP SS is Followed by a Store or an MMX Instruction            |

#### Table 3. Integrated Core/Uncore Errata (Sheet 1 of 5)

|        |             | Step | pings  |        |        |                                                                                                                          |

|--------|-------------|------|--------|--------|--------|--------------------------------------------------------------------------------------------------------------------------|

| Number | V1 V2 Y0 A1 |      | Status | ERRATA |        |                                                                                                                          |

| BDE26  | Х           | Х    | Х      | Х      | No Fix | VEX.L is Not Ignored with VCVT*2SI Instructions                                                                          |

| BDE27  | Х           | Х    | Х      | Х      | No Fix | Processor May Livelock During On Demand Clock Modulation                                                                 |

| BDE28  | Х           | Х    | Х      | Х      | No Fix | Performance Monitor Events OTHER_ASSISTS.AVX_TO_SSE And OTHER_ASSISTS.SSE_TO_AVX May Over Count                          |

| BDE29  | Х           | Х    | Х      | Х      | No Fix | Performance Monitor Event DSB2MITE_SWITCHES.COUNT May Over Count                                                         |

| BDE30  |             |      |        |        |        | Erratum BDE30 Removed Due to Inapplicability                                                                             |

| BDE31  | Х           | Х    | Х      | Х      | No Fix | IA32_VMX_VMCS_ENUM MSR (48AH) Does Not Properly Report The Highest Index Value Used For VMCS Encoding                    |

| BDE32  | Х           | Х    | Х      | Х      | No Fix | Incorrect FROM_IP Value For an RTM Abort in BTM or BTS May be Observed                                                   |

| BDE33  | Х           | Х    | Х      | Х      | No Fix | Locked Load Performance Monitoring Events May Under Count                                                                |

| BDE34  | Х           | Х    | Х      | Х      | No Fix | Transactional Abort May Cause an Incorrect Branch Record                                                                 |

| BDE35  | Х           | Х    | Х      | Х      | No Fix | PMI May be Signaled More Than Once For Performance Monitor<br>Counter Overflow                                           |

| BDE36  | Х           | Х    | Х      | Х      | No Fix | Execution of FXSAVE or FXRSTOR With the VEX Prefix May Produce a #NM Exception                                           |

| BDE37  | Х           | Х    | Х      | Х      | No Fix | VM Exit May Set IA32_EFER.NXE When IA32_MISC_ENABLE Bit 34 is Set to 1                                                   |

| BDE38  | Х           | Х    | Х      | Х      | No Fix | A MOV to CR3 When EPT is Enabled May Lead to an Unexpected Page Fault or an Incorrect Page Translation                   |

| BDE39  | Х           | Х    | Х      | Х      | No Fix | Intel <sup>® Processor Trace Packet Generation May Stop Sooner Than Expected</sup>                                       |

| BDE40  | Х           | Х    | Х      | Х      | No Fix | PEBS Eventing IP Field May be Incorrect After Not-Taken Branch                                                           |

| BDE41  | Х           |      |        |        | Fixed  | Reading The Memory Destination of an Instruction That Begins an HLE Transaction May Return The Original Value            |

| BDE42  |             |      |        |        |        | Erratum removed due to inapplicability                                                                                   |

| BDE43  | Х           | Х    | Х      | Х      | No Fix | Performance Monitoring Event INSTR_RETIRED.ALL May Generate Redundant PEBS Records For an Overflow                       |

| BDE44  | Х           | Х    | Х      | Х      | No Fix | Intel <sup>®</sup> Processor Trace (Intel <sup>®</sup> PT) MODE.Exec, PIP, and CBR Packets Are Not Generated as Expected |

| BDE45  | Х           | Х    | Х      | Х      | No Fix | Performance Monitor Instructions Retired Event May Not Count Consistently                                                |

| BDE46  | Х           | Х    | Х      | Х      | No Fix | General-Purpose Performance Counters May be Inaccurate with Any Thread                                                   |

| BDE47  | Х           | Х    | Х      | Х      | No Fix | An Invalid LBR May Be Recorded Following a Transactional Abort                                                           |

| BDE48  | Х           | Х    | Х      | Х      | No Fix | Executing an RSM Instruction With Intel <sup>® Processor Trace (Intel® PT) Enabled Will Signal a #GP</sup>               |

| BDE49  | Х           |      |        |        | Fixed  | Intel <sup>® Processor Trace PIP May be Unexpectedly Generated</sup>                                                     |

| BDE50  | Х           | Х    | Х      | Х      | No Fix | Processor Core Ratio Changes While in Probe Mode May Result in a Hang                                                    |

| BDE51  | Х           | Х    | Х      | Х      | No Fix | Processor Does Not Check IRTE Reserved Bits                                                                              |

| BDE52  | Х           | Х    | Х      | Х      | No Fix | PCIe* TPH Request Capability Structure Incorrectly Advertises<br>Device Specific Mode as Supported                       |

| BDE53  | Х           | Х    |        |        | No Fix | Package C3 State or Deeper May Lead to a Reset                                                                           |

| BDE54  | Х           | Х    | Х      |        | No Fix | Using Intel <sup>®</sup> QuickData Technology With ADR May Result in Unpredictable System Behavior                       |

| BDE55  | Х           | Х    | Х      | Х      | No Fix | Intel® Advanced Vector Extensions (Intel® AVX) Workloads May Exceed ICCMAX                                               |

## Table 3. Integrated Core/Uncore Errata (Sheet 2 of 5)

| Number |             | Step | pings  |        | Status | EDDATA                                                                                                                             |  |

|--------|-------------|------|--------|--------|--------|------------------------------------------------------------------------------------------------------------------------------------|--|

| Number | V1 V2 Y0 A1 |      | Status | ERRATA |        |                                                                                                                                    |  |

| BDE56  | Х           | Х    | Х      |        | No Fix | PECI RdPkgConfig Returns Incorrect Maximum Number of Threads                                                                       |  |

| BDE57  | Х           |      |        |        | Fixed  | DRAM tCL Improperly Limited to 14                                                                                                  |  |

| BDE58  | Х           | Х    | Х      | Х      | No Fix | Disabling UFS May Cause a System Hang                                                                                              |  |

| BDE59  | Х           | Х    | Х      | Х      | No Fix | Writing MSR_ERROR_CONTROL May Cause a #GP                                                                                          |  |

| BDE60  | Х           | Х    | Х      | Х      | No Fix | Isoch and Non-Isoch Traffic Concurrently Accessing The Same Cache<br>Line May Result in System Instability                         |  |

| BDE61  | Х           |      |        |        | Fixed  | Intel <sup>®</sup> QuickPath Interconnect (Intel <sup>®</sup> QPI) Quiescence Flow And IODC Incorrectly<br>Advertised as Supported |  |

| BDE62  | Х           | Х    | х      | Х      | No Fix | Intel <sup>®</sup> QuickData Technology Version 3.3 Source Application Tag Mask May Behave Incorrectly                             |  |

| BDE63  | Х           | х    | х      | х      | No Fix | Enabling ACC in VMX Non-Root Operation May Cause System<br>Instability                                                             |  |

| BDE64  | Х           | Х    | Х      | Х      | No Fix | Deleted. Duplicate with BDE55.                                                                                                     |  |

| BDE65  | Х           | Х    | х      | х      | No Fix | PAGE_WALKER_LOADS Performance Monitoring Event May Count<br>Incorrectly                                                            |  |

| BDE66  | Х           | Х    | Х      | Х      | No Fix | A spurious Patrol Scrub Error May be Logged                                                                                        |  |

| BDE67  | Х           | Х    | Х      | Х      | No Fix | Incorrect NC-SI Flow Control Timing May Lead to BMC Packet Loss                                                                    |  |

| BDE68  | Х           | х    | х      | х      | No Fix | Concurrent 10 GbE Port Operation May Result in Packet Loss or Reduced Bandwidth                                                    |  |

| BDE69  | Х           |      |        |        | Fixed  | MDIO Interface Not Available in S5 State                                                                                           |  |

| BDE70  | Х           |      |        |        | Fixed  | The Ethernet Flow Director May Incorrectly Route Fragmented Packets                                                                |  |

| BDE71  |             |      | Х      | Х      | No Fix | The System May Hang When Executing a Complex Sequence of Locked Instructions                                                       |  |

| BDE72  | Х           | Х    | Х      | Х      | No Fix | PCS11 May be Inaccurate When HWPM is Disabled                                                                                      |  |

| BDE73  | Х           | Х    |        |        | Fixed  | A Second Power Loss Indication May Not Initiate a Memory ADR Flow                                                                  |  |

| BDE74  | Х           | Х    | Х      | Х      | No Fix | Unexpected Performance Loss When Turbo Disabled                                                                                    |  |

| BDE75  | Х           | Х    | х      |        | No Fix | Reset During PECI Transaction May Cause a Machine Check<br>Exception                                                               |  |

| BDE76  | Х           | Х    | х      | Х      | No Fix | Package C-state Transitions While Inband PECI Accesses Are in<br>Progress May Cause Performance Degradation                        |  |

| BDE77  | Х           | Х    | х      | х      | No Fix | Data Breakpoint Coincident With a Machine Check Exception May be<br>Lost                                                           |  |

| BDE78  | Х           | Х    | Х      | Х      | No Fix | Populating Both Memory Channels May Lead to Memory Errors                                                                          |  |

| BDE79  | Х           | Х    | х      | х      | No Fix | PECI May Not be Responsive After a Warm Reset Resulting From an IERR                                                               |  |

| BDE80  | Х           | Х    | Х      | Х      | No Fix | Memory Data Scrambling is Not Compatible with CAP Error Flow                                                                       |  |

| BDE81  |             | х    | Х      | Х      | No Fix | CAP Error May Cause System Hang                                                                                                    |  |