## PCI 10/100 Ethernet and V.90/V.92 Controller

### **REVISION HISTORY**

| Revision    | Date     | Change Description                                                           |

|-------------|----------|------------------------------------------------------------------------------|

| 440X-PG02-R | 06/02/09 | Updated:                                                                     |

|             |          | Table 101: "Transmit Watermark Register Bit Field Descriptions," on page 92. |

|             |          | Added:                                                                       |

|             |          | <ul> <li>"LED Control Select Tables" on page 80.</li> </ul>                  |

| 440X-PG01-R | 09/12/03 | Added changes for BCM4401 B0 revision silicon.                               |

| 440X-PG00-R | 08/23/02 | Initial Release.                                                             |

Broadcom Corporation 5300 California Avenue Irvine, CA 92617

© 2009 by Broadcom Corporation All rights reserved Printed in the U.S.A.

Broadcom<sup>®</sup>, the pulse logo, Connecting everything<sup>®</sup>, the Connecting everything logo, and Digi- $\Phi^{TM}$  are among the trademarks of Broadcom Corporation and/or its affiliates in the United States, certain other countries and/or the EU. Any other trademarks or trade names mentioned are the property of their respective owners.

## TABLE OF CONTENTS

| Section 1: Overview1                                                                   |

|----------------------------------------------------------------------------------------|

| BCM440X Description                                                                    |

| BCM440X Features                                                                       |

| 10/100 Ethernet MAC/PHY                                                                |

| Codec Modem Function (BCM4402 only)3                                                   |

| Device Initialization and Reset                                                        |

| Related Documents                                                                      |

| Section 2: Backplane                                                                   |

| Backplane, Cores, and Agents                                                           |

| Supported Operations                                                                   |

| Arbitration                                                                            |

| Interrupt Architecture                                                                 |

| Error Architecture                                                                     |

| Address Space Map                                                                      |

| Core Configuration Space Registers                                                     |

| Updating Buffered Registers                                                            |

| System Backplane Initiator OCP Slave Flag Control Register (SBIPSFLAG, offset 0xF08)   |

| System Backplane Target OCP Slave Flag Control Register (SBTPSFLAG, offset 0xF18) 10   |

| System Backplane Address Match 3 Register (SBADMATCH3, offset 0xF60) 10                |

| System Backplane Address Match 2 Register (SBADMATCH2, offset 0xF68)                   |

| System Backplane Address Match 1 Register (SBADMATCH1, offset 0xF70) 11                |

| System Backplane Initiator State Register (SBIMSTATE, offset 0xF90)                    |

| System Backplane Interrupt Vector Register (SBINTVEC, offset 0xF94)                    |

| System Backplane Target State Low Register (SBTMSTATELOW, offset 0xF98) 14             |

| System Backplane Target State High Register (SBTMSTATEHIGH, offset 0xF9C)              |

| System Backplane Bandwidth Allocation Table 0 Register (SBBWA0, offset 0xFA0) 16       |

| System Backplane Initiator Configuration Low Register (SBIMCONFIGLOW, offset 0xFA8) 17 |

| System Backplane Initiator Configuration High Register (SBIMCONFIGHIGH, offset 0xFAC)  |

| System Backplane Address Match 0 Register (SBADMATCH0, offset 0xFB0) 19                |

| System Backplane Target Configuration Low Register (SBTMCONFIGLOW, offset 0xFB8)20     |

| System Backplane Target Configuration High Register (SBTMCONFIGHIGH, offset 0xFBC)     |

| System Backplane Broadcast Configuration Register (SBBCONFIG, offset 0xFC0) 22         |

| System Backplane Broadcast State Register (SBBSTATE, offset 0xFC8)         | 23 |

|----------------------------------------------------------------------------|----|

| System Backplane Activate Configuration Register (SBACTCNFG, offset 0xFD8) | 24 |

| System Backplane Flag Status Register (SBFLAGST, offset 0xFE8)             | 24 |

| System Backplane Identification Low Register (SBIDLOW, offset 0xFF8)       | 25 |

| System Backplane Identification High Register (SBIDHIGH, offset 0xFFC)     | 26 |

| Section 3: DMA                                                             | 27 |

| Register Descriptions                                                      | 27 |

| Transmit Channel Control Register (XmtControl, offset 0x200)               | 28 |

| Transmit Descriptor Table Address Register (XmtAddr, offset 0x204)         | 29 |

| Transmit Descriptor Table Pointer Register (XmtPtr, offset 0x208)          | 30 |

| Transmit Channel Status Register (XmtStatus, offset 0x20C)                 | 31 |

| Receive Channel Control Register (RcvControl, offset 0x210)                | 33 |

| Receive Descriptor Table Address Register (RcvAddr, offset 0x214)          | 34 |

| Receive Descriptor Table Pointer Register (RcvPtr, offset 0x218)           | 35 |

| Receive Channel Status Register (RcvStatus, offset 0x21C)                  | 36 |

| Programmer's Model                                                         | 38 |

| Descriptor Structure                                                       | 38 |

| Descriptor Tables                                                          | 40 |

| Transmit Descriptors                                                       | 40 |

| Receive Descriptors                                                        | 40 |

| Descriptor Processor Channel Initialization                                | 41 |

| Descriptor Processor Channel Reset                                         | 41 |

| Host Bus Arbitration Between Receive and Transmit                          | 41 |

| Receive Frame Status Information                                           | 42 |

| Error Conditions                                                           | 43 |

| Descriptor Read Error                                                      | 43 |

| Data Transfer Error                                                        | 43 |

| Descriptor Protocol Error                                                  | 43 |

| Receive Descriptor Underflow                                               | 43 |

| Section 4: Codec Core (BCM4402 only)                                       | 44 |

| Codec Registers                                                            | 44 |

| Codec Device and Power Control Registers                                   | 44 |

| Device Control Register (DevControl, offset 0x00)                          | 45 |

| Built-In Self Test Register (BISTStatus, offset 0x0C)                      | 47 |

|                                                                            |    |

| Codec Interrupt Handling Registers                                |    |

|-------------------------------------------------------------------|----|

| Interrupt Status Register (IntStatus, offset 0x20)                |    |

| Interrupt Mask Register (IntMask, offset 0x24)                    | 50 |

| General Purpose Timer Register (GPTimer, offset 0x28)             | 51 |

| Codec Control and Status Registers                                |    |

| Codec Control Command Register (CodecCtlCommand, offset 0x38)     |    |

| Codec Control Status Register (CodecCtlStatus, offset 0x3C)       |    |

| Audio/IR Registers                                                |    |

| IRXmtClkDivideCount Register (IRXmtClkDivideCount, offset 0xD0)   | 55 |

| IRRcvClkDivideCount Register (IRRcvClkDivideCount, offset 0xD4)   | 55 |

| AudioSClkDivideCount Register (AudioSClkDivideCount, offset 0xD8) |    |

| AudioLRckDivideCount Register (AudioLRckDivideCount, offset 0xDC) |    |

| Audio Control Offset Register (AudioControl offset 0xE0)          |    |

| Offhook Watchdog Register (OffhookWatchdog, offset 0xE4)          |    |

| Codec Descriptor Processing Registers                             |    |

| Descriptor Processor                                              |    |

| Descriptor Buffer Alignment                                       |    |

| Descriptor Core Flags                                             |    |

| Receive Frame Data Header Size                                    |    |

| DMA-related Interrupts and Errors                                 |    |

| Interrupts                                                        |    |

| Section 5: Ethernet 10/100 Core                                   | 58 |

| Ethernet MAC Registers                                            |    |

| Ethernet Device and Power Control Registers                       | 61 |

| Device Control Register (DevControl, offset 0x00)                 |    |

| Built-In Self Test Register (BISTStatus, offset 0x0C)             |    |

| Wakeup Length Register (WakeupLength, offset 0x10)                |    |

| Ethernet Interrupt Handling Registers                             |    |

| Interrupt Status Register (IntStatus, offset 0x20)                |    |

| Interrupt Mask Register (IntMask, offset 0x24)                    | 71 |

| General Purpose Timer Register (GPTimer, offset 0x28)             | 73 |

|                                                                   |    |

| Ethernet Address and Data Registers                                                      | 74                 |

|------------------------------------------------------------------------------------------|--------------------|

| Ethernet Magic Packet™ Address Lower Register (ENetMPAddrLower, off<br>(BCM4401 B0 only) |                    |

| Ethernet Magic Packet Address Upper Register (ENetMPAddrUpper, offse (BCM4401 B0 only)   |                    |

| Ethernet Filter Table Address Register (ENetFtAddr, offset 0x90)                         |                    |

| Ethernet Filter Table Data Register (ENetFtData, offset 0x94)                            | 77                 |

| Ethernet Medium Access Control Registers                                                 |                    |

| Ethernet MAC Transmit Max Burst Length Register (EMACXmtMaxBurstLe                       | en, offset 0xA0)79 |

| Ethernet MAC Receive Max Burst Length Register (EMACRcvMaxBurstLe                        | n, offset 0xA4)79  |

| Ethernet MAC Control Register (EMACControl, offset 0xA8)                                 | 79                 |

| LED Control Select Tables                                                                | 80                 |

| Ethernet MAC Flow Control Register (EMACFlowControl, offset 0xAC)                        | 82                 |

| Receive Interrupt Control Registers                                                      | 83                 |

| Interrupt Receive Lazy Time-out Register (IntRecvLazy, offset 0x100)                     | 83                 |

| Ethernet Descriptor Processing Registers                                                 | 84                 |

| Ethernet MAC Registers                                                                   | 84                 |

| Receiver Configuration Register (RcvConfig, offset 0x400)                                | 85                 |

| Receive Maximum Length Register (RcvLength, offset 0x404)                                |                    |

| Transmit Maximum Length Register (XmtMaxLength, offset 0x408)                            |                    |

| MII Status/Control Register (MIIStatusControl, offset 0x410)                             |                    |

| MII Data Register (MIIData offset 0x414)                                                 |                    |

| Ethernet Interrupt Mask Register (EnetIntMask, offset 0x418)                             |                    |

| Ethernet Interrupt Status Register (EnetIntStatus, offset 0x41C)                         |                    |

| CAM Data Low Register (CAMDataL, offset 0x420)                                           |                    |

| CAM Data High Register (CAMDataH, offset 0x424)                                          |                    |

| CAM Control Register (CAMControl, offset 0x428)                                          |                    |

| Ethernet Control Register (EnetControl, offset 0x42C)                                    |                    |

| Transmit Control Register (XmtControl, offset 0x430)                                     | 91                 |

| Transmit Watermark Register (XmtWatermark, offset 0x434)                                 |                    |

| MIB Control Register (MIBControl, offset 0x438)                                          |                    |

| Management Information Block (MIB) Statistic Counters                                    | 94                 |

| Ethernet PHY Registers                                                                   |                    |

| MII Control Register (MIIControl, offset 0x00)                                           |                    |

| MII Status Register (MIIStatus, offset 0x01)                                             |                    |

| PHY Identifier High Register (PHYIDHigh, offset 0x02)                                 | 102     |

|---------------------------------------------------------------------------------------|---------|

| PHY Identifier Low Register (PHYIDLow, offset 0x03)                                   | 102     |

| Auto-Negotiation Advertisement Register (AutoNegAdvertise, offset 0x04)               | 103     |

| Auto-Negotiation Link Partner Ability Register (LinkPartnerAbility, offset 0x05)      | 104     |

| Auto-Negotiation Expansion Register (AutoNegExpansion, offset 0x06)                   | 105     |

| Auto-Negotiation Next Page Transmit Register (NextPage, offset 0x07)                  | 106     |

| Auto-Negotiation Link Partner Next Page Transmit Register (LPNextPage, offset 0x08)   | 107     |

| 100BASE-X Auxiliary Control Register (100BASE-XAuxControl, offset 0x10)               | 108     |

| 100BASE-X Auxiliary Status Register (100BASE-XAuxStatus, offset 0x11)                 | 110     |

| 100BASE-X Receive Error Counter (100BASE-XRcvErrorCtr, offset 0x12)                   | 112     |

| 100BASE-X False Carrier Sense Counter (100BASE-XCarrierSenseCtr, offset 0x13)         | 112     |

| 100BASE-X Disconnect Counter (100BASE-XDisconnectCtr, offset 0x14)                    | 113     |

| 100BASE-X Auxiliary Control/Status Register (AuxCtlStatus, offset 0x18)               | 114     |

| 100BASE-X Auxiliary Status Summary Register (AuxStatusSummary, offset 0x19)           | 116     |

| Interrupt Register (Interrupt, offset 0x1A)                                           | 118     |

| Auxiliary Mode 2 Register (AuxMode2, offset 0x1B)                                     | 119     |

| 10BASE-T Auxiliary Error and General Status Register (10BASE-TErrGenStatus, offset 0x | 1C) 121 |

| Auxiliary Mode Register (AuxMode, offset 0x1D)                                        | 123     |

| Auxiliary Multiple PHY Register (AuxMultiPHY, offset 0x1E)                            | 124     |

| MII Shadow Registers                                                                  | 126     |

| Auxiliary Mode 4 (Shadow) Register (AuxMode4, offset 0x1A)                            | 127     |

| Auxiliary Status 2 (Shadow) Register (AuxStatus2, offset 0x1B)                        | 128     |

| Auxiliary Status 3 (Shadow) Register (AuxStatus3, offset 0x1C)                        | 129     |

| Auxiliary Mode 3 (Shadow) Register (AuxMode3, offset 0x1D)                            | 130     |

| Auxiliary Status 4 (Shadow) Register (AuxStatus4, offset 0x1E)                        | 130     |

| Descriptor Processor                                                                  | 131     |

| Descriptor Core Flags                                                                 | 131     |

| Receive Frame Data Header Size                                                        | 131     |

| DMA-related Interrupts and Errors                                                     | 131     |

| Ethernet MAC Interface                                                                | 131     |

| Ethernet Packet Structure                                                             | 132     |

| MAC Operation                                                                         | 133     |

| Receiver                                                                              | 134     |

| Address Recognition                                                                   | 135     |

| Receive FIFO                                                                          | 135     |

| Flow Control                                    |     |

|-------------------------------------------------|-----|

| Receiver Control and Configuration              |     |

| Transmitter                                     | 136 |

| Preamble and SFD Generation                     |     |

| CRC Generation                                  | 136 |

| Auto Padding                                    | 137 |

| Carrier Deference and Interframe Spacing        | 137 |

| Collision Detection and Enforcement             |     |

| Collision Backoff and Retransmission            | 137 |

| Full/Half-Duplex Operation                      |     |

| Flow Control                                    |     |

| Transmit FIFO                                   |     |

| Loopback Support                                |     |

| Error Detection and Support                     |     |

| Watermark and Max Length Support                |     |

| Content Addressable Memory (CAM)                |     |

| Programming the CAM                             | 140 |

| Management Information Statistic Counters (MIB) | 140 |

| Counter Reset                                   |     |

| Counter Reads                                   | 140 |

| Counter Reset On Read                           | 141 |

| Full-Duplex Flow Control                        |     |

| Pause Frame Reception and Transmitter Pause     |     |

| Interrupts                                      |     |

| Ethernet Core Initialization                    | 145 |

| Network Wakeup Frame Detection                  |     |

| Wakeup Frame Patterns                           |     |

| AMD <sup>®</sup> Magic Packet Wakeup            | 147 |

| Section 6: PCI Core                             | 148 |

| Modes and Functions                             | 148 |

| Address Spaces                                  | 148 |

| System Backplane                                | 148 |

| PCI Bus                                         | 148 |

| Expansion ROM                                   |     |

06/02/09

| Interrupts                                                                              | 149 |  |

|-----------------------------------------------------------------------------------------|-----|--|

| Enumeration Space and Host Control Registers                                            |     |  |

| Core Control and Status Registers                                                       | 150 |  |

| Built-In Self Test Register (BISTStatus, offset 0x0C)                                   | 151 |  |

| Interrupt Control Registers                                                             | 152 |  |

| Interrupt Status Register (IntStatus, offset 0x20)                                      | 153 |  |

| Interrupt Mask Register (IntMask, offset 0x24)                                          | 154 |  |

| System Backplane to PCI Mailbox Register (SBtoPCIMailbox, offset 0x28)                  | 155 |  |

| Broadcast Registers                                                                     | 156 |  |

| Broadcast Address Register (BroadcastAddress, offset 0x50)                              | 156 |  |

| Broadcast Data Register (BroadcastData, offset 0x54)                                    | 156 |  |

| GPIO Registers                                                                          | 157 |  |

| General Purpose I/O Input Register (GPIOInput, offset 0x60)                             | 158 |  |

| General Purpose I/O Output Register (GPIOOutput, offset 0x64)                           | 158 |  |

| General Purpose I/O Output Enable Register (GPIOOutEn, offset 0x68)                     | 158 |  |

| General Purpose I/O Control Register (GPIOControl, offset 0x6C)                         | 158 |  |

| General Purpose I/O Input Register (GPIOInput, offset 0xB0) (BCM4401 B0 Only)           | 158 |  |

| General Purpose I/O Output Register (GPIOOutput, offset 0x0xB4) (BCM4401 B0 Only)       | 158 |  |

| General Purpose I/O Output Enable Register (GPIOOutEn, offset 0x0xB8) (BCM4401 B0 Only) | 158 |  |

| Address Translation Registers                                                           | 159 |  |

| System Backplane to PCI Translation 0 Register (SBtoPCITranslation0, offset 0x100)      | 160 |  |

| System Backplane to PCI Translation 1 Register (SBtoPCITranslation1, offset 0x104)      | 161 |  |

| SPROM Shadow Area (SPROMShadow, Offset 0x800 to 0x847)                                  | 162 |  |

| Configuration Space Registers                                                           | 163 |  |

| Standard Configuration Registers                                                        | 163 |  |

| Vendor ID Register (VendorID, offset 0x00)                                              | 164 |  |

| Device ID Register (DeviceID, offset 0x02)                                              | 164 |  |

| Command Register (Command, offset 0x04)                                                 | 165 |  |

| Status Register (Status, offset 0x06)                                                   | 167 |  |

| Revision ID Register (RevisionID, offset 0x08)                                          | 168 |  |

| Class Code Register (ClassCode, offset 0x09)                                            | 168 |  |

| Latency Timer Register (Latency, offset 0x0D)                                           | 168 |  |

| Configuration Header Type Register (HeaderType, offset 0x0E)                            | 168 |  |

| Base Address 0 Register (BAR0, offset 0x10)                                             | 169 |  |

| Base Address 1 Register (BAR1, offset 0x14)                                             | 170 |  |

|                                                                                         |     |  |

|   | PCI Subsystem Vendor ID Register (SubsystemVendorID, offset 0x2C)      | 171 |

|---|------------------------------------------------------------------------|-----|

|   | PCI Subsystem ID Register (SubsystemID, offset 0x2E)                   | 171 |

|   | Expansion ROM Bar Register (ExpansionROMBar, offset 0x30)              | 171 |

|   | Capability List Pointer Register (CapPtr, offset 0x34)                 | 171 |

|   | PCI Interrupt Line Register (IntLine, offset 0x3C)                     | 171 |

|   | PCI Interrupt Pin Register (IntPin, offset 0x3D)                       | 171 |

|   | PCI Minimum Grant Register (MinGnt, offset 0x3E)                       | 171 |

|   | PCI Maximum Latency Register (MaxLat, offset 0x3F)                     | 171 |

|   | Power Management Capability Definition Block                           |     |

|   | PCI Power Management Capability ID Register (CapID, offset 0x40)       | 172 |

|   | PCI Next Capability Pointer Register (CapNext, offset 0x41)            |     |

|   | PCI Power Management Capability Register (PMC, offset 0x42)            | 173 |

|   | PCI Power Management Control/Status Register (PMCSR, offset 0x44)      | 174 |

|   | PCI Power Management Data Register (PMData, offset 0x48)               |     |

|   | Device Specific Configuration Space Registers                          | 175 |

|   | PCI to Bar 0 Window Register (PCIBar0Window, offset 0x80)              | 176 |

|   | PCI to Bar 1 Window Register (PCIBar1Window, offset 0x84)              | 176 |

|   | SPROM Control Register (SPROMControl, Offset 0x88)                     |     |

|   | Bar 1 Burst Control Register (BAR1BurstControl, offset 0x8c)           | 178 |

|   | PCI Interrupt Status Register (PCIIntStatus, offset 0x90)              | 179 |

|   | PCI Interrupt Mask Register (PCIIntMask, offset 0x94)                  |     |

|   | PCI to System Backplane Mailbox Register (PCItoSBMailbox, offset 0x98) |     |

|   | Backplane Access Registers                                             |     |

|   | Backplane Address (BackplaneAddress, offset 0xa0)                      |     |

|   | Backplane Data Register (BackplaneData, offset 0xa4)                   |     |

|   | Unimplemented PCI Configuration Registers                              | 184 |

| S | Section 7: Programming Hints                                           | 185 |

| U |                                                                        |     |

|   | Reset                                                                  |     |

|   | Internal Clock Frequencies                                             |     |

|   | Calculating the CRC8 Checksum                                          |     |

|   | SPROM Layout                                                           |     |

## LIST OF FIGURES

| Figure 1: | BCM440X Block Diagram       | 1   |

|-----------|-----------------------------|-----|

| Figure 2: | BCM440X System Diagram      | 2   |

| Figure 3: | 802.3 Ethernet Frame Format | 132 |

| Figure 4: | Ethernet MAC                | 133 |

| Figure 5: | CAM Description             | 139 |

## LIST OF TABLES

| Table 1:  | Interrupt Cores                                                                   | 6    |

|-----------|-----------------------------------------------------------------------------------|------|

| Table 2:  | BCM440X Address Space                                                             | 7    |

| Table 3:  | Core Configuration Space Registers                                                | 8    |

| Table 4:  | System Backplane Initiator OCP Slave Flag Control Register Bit Field Descriptions | 9    |

| Table 5:  | System Backplane Target OCP Slave Flag Control Register Bit Field Descriptions    | . 10 |

| Table 6:  | sbFlag Values                                                                     | . 10 |

| Table 7:  | System Backplane Address Match Registers Bit Field Descriptions                   | . 11 |

| Table 8:  | System Backplane Initiator State Register Bit Field Descriptions                  | . 12 |

| Table 9:  | Arbitration Policy                                                                | . 12 |

| Table 10: | System Backplane Interrupt Vector Register Core Interrupts                        | . 13 |

| Table 11: | System Backplane Target State Low Register Bit Field Descriptions                 | . 14 |

| Table 12: | System Backplane Target State High Register Bit Field Descriptions                | . 15 |

| Table 13: | System Backplane Bandwidth Allocation Table 0 Register Bit Field Descriptions     | . 16 |

| Table 14: | System Backplane Initiator Configuration Low Register Bit Field Descriptions      | . 17 |

| Table 15: | SB Timeout Period                                                                 | . 17 |

| Table 16: | System Backplane Initiator Configuration High Register Bit Field Descriptions     | . 18 |

| Table 17: | System Backplane Address Match 0 Register Bit Field Descriptions                  | . 19 |

| Table 18: | System Backplane Target Configuration Low Register Bit Field Descriptions         | . 20 |

| Table 19: | System Backplane Target Configuration High Register Bit Field Descriptions        | . 21 |

| Table 20: | System Backplane Broadcast Configuration Register Bit Field Descriptions          | . 22 |

| Table 21: | System Backplane Broadcast State Register Bit Field Descriptions                  | . 23 |

| Table 22: | System Backplane Identification Low Register Bit Field Descriptions               | . 25 |

| Table 23: | System Backplane Identification High Register Bit Field Descriptions              | . 26 |

| Table 24: | OCP Cores                                                                         | . 26 |

| Table 25: | Transmit Channel Control Register Bit Field Descriptions                          | . 28 |

| Table 26: | Transmit Descriptor Table Address Register Bit Field Descriptions                 | . 29 |

| Table 27: | Transmit Descriptor Table Pointer Register Bit Field Descriptions                 | . 30 |

| Table 28: | Transmit Channel Status Register Bit Field Descriptions                           | . 31 |

| Table 29: | Transmit Channel Status                                                           | . 32 |

| Table 30: | Transmit Channel Errors                                                           | . 32 |

| Table 31: | Receive Channel Control Register Bit Field Descriptions                           | . 33 |

| Table 32: | Receive Descriptor Table Address Register Bit Field Descriptions                  | . 34 |

| Table 33: | Receive Descriptor Table Pointer Register Bit Field Descriptions                  | . 35 |

| Table 34: | Receive Channel Status Register Bit Field Descriptions                  | .36 |

|-----------|-------------------------------------------------------------------------|-----|

| Table 35: | Receive Channel State                                                   | .37 |

| Table 36: | Receive Channel Errors                                                  | .37 |

| Table 37: | Transmit and Receive Descriptor Table Entries                           | .38 |

| Table 38: | Receive Frame Status Fields                                             | .42 |

| Table 39: | IntStatus and IntMask Registers                                         | .43 |

| Table 40: | Codec Host Interface Register Address Spaces                            | .44 |

| Table 41: | Codec Host Interface Registers                                          | .44 |

| Table 42: | Device Control Register Bit Field Descriptions                          | .45 |

| Table 43: | Active Interfaces                                                       | .46 |

| Table 44: | Mode-Dependent Changes                                                  | .46 |

| Table 45: | Interrupt Status Register Bit Field Descriptions                        | .47 |

| Table 46: | RAM-to-Bit Mapping                                                      | .47 |

| Table 47: | Interrupt Status Register Bit Field Descriptions                        | .48 |

| Table 48: | Interrupt Mask Register Bit Field Descriptions                          | .50 |

| Table 49: | General Purpose Timer Register Bit Field Descriptions                   | .51 |

| Table 50: | Codec Control Command Register Bit Field Descriptions                   | .52 |

| Table 51: | Codec Control Status Register Bit Field Descriptions                    | .53 |

| Table 52: | IRXmtClkDivideCount Register Bit Field Descriptions                     | .55 |

| Table 53: | IRRcvClkDivideCount Register Bit Field Descriptions                     | .55 |

| Table 54: | AudioSClkDivideCount Register Bit Field Descriptions                    | .55 |

| Table 55: | AudioLRckDivideCount Register Bit Field Descriptions                    | .56 |

| Table 56: | Audio Control Offset Register Bit Field Descriptions                    | .56 |

| Table 57: | Offhook Watchdog Register Bit Field Descriptions                        | .56 |

| Table 58: | Ethernet MAC Host Interface Register Address Spaces                     | .58 |

| Table 59: | Ethernet MAC Host Interface Registers                                   | .58 |

| Table 60: | Ethernet PHY MII Registers                                              | .59 |

| Table 61: | MII Shadow Registers                                                    | .60 |

| Table 62: | Device Control Register Bit Field Descriptions (BCM4401 B0 and Later)   | .62 |

| Table 63: | Device Control Register Bit Field Descriptions (Rest of BCM440X Family) | .63 |

| Table 64: | BIST Status Register Bit Field Descriptions (BCM4401 B0 and Later)      | .64 |

| Table 65: | RAM-to-Bit Mapping (BCM4401 B0 and Later)                               | .64 |

| Table 66: | BIST Status Register Bit Field Descriptions (Rest of BCM440X Family)    | .65 |

| Table 67: | RAM-to-Bit Mapping (Rest of BCM440X Family)                             | .65 |

| Table 68: | Wakeup Length Register Bit Field Descriptions                           | .66 |

### Programmer's Reference Guide

| Table 69: | Interrupt Status Register Bit Field Descriptions (BCM4401 B0 and Later)          | 68 |

|-----------|----------------------------------------------------------------------------------|----|

| Table 70: | Interrupt Status Register Bit Field Descriptions (Rest of BCM440X Family)        | 69 |

| Table 71: | Interrupt Mask Register Bit Field Descriptions                                   | 71 |

| Table 72: | General Purpose Timer Register Bit Field Descriptions                            | 73 |

| Table 73: | Ethernet Magic Packet Address Lower Register Descriptions (BCM4401 B0 and Later) | 75 |

| Table 74: | Ethernet Magic Packet Address Upper Register Descriptions (BCM4401 B0 and Later) | 75 |

| Table 75: | Ethernet Filter Table Address Register Bit Field Descriptions                    | 76 |

| Table 76: | Ethernet Filter Table Address Space                                              | 76 |

| Table 77: | Ethernet Filter Table Data Register Bit Field Descriptions                       | 77 |

| Table 78: | Ethernet MAC Control Register Bit Field Descriptions                             | 79 |

| Table 79: | LED Control 000 Selects                                                          | 80 |

| Table 80: | LED Control 001 Selects                                                          | 80 |

| Table 81: | LED Control 010 Selects                                                          | 80 |

| Table 82: | LED Control 011 Selects                                                          | 80 |

| Table 83: | LED Control 100 Selects                                                          | 80 |

| Table 84: | LED Control 101 Selects                                                          | 81 |

| Table 85: | LED Control 110 Selects                                                          | 81 |

| Table 86: | LED Control 111 Selects                                                          | 81 |

| Table 87: | Transmit FIFO Control Register Bit Field Descriptions                            | 82 |

| Table 88: | Interrupt Receive Lazy Time-out Register Bit Field Descriptions                  | 83 |

| Table 89: | Receiver Configuration Register Bit Field Descriptions                           | 85 |

| Table 90: | Receive Maximum Length Register Bit Field Descriptions                           | 86 |

| Table 91: | Transmit Maximum Length Register Bit Field Descriptions                          | 86 |

| Table 92: | MII Status/Control Register Bit Field Descriptions                               | 86 |

| Table 93: | MII Data Register Bit Field Descriptions                                         | 87 |

| Table 94: | Ethernet Interrupt Mask Register Bit Field Descriptions                          | 87 |

| Table 95: | Ethernet Interrupt Status Register Bit Field Descriptions                        | 88 |

| Table 96: | CAM Data Low Register Bit Field Descriptions                                     | 88 |

| Table 97: | CAM Data High Register Bit Field Descriptions                                    | 89 |

| Table 98: | CAM Control Register Bit Field Descriptions                                      | 89 |

| Table 99: | Ethernet Control Register Bit Field Descriptions                                 | 90 |

| Table 100 | :Transmit Control Register Bit Field Descriptions                                | 91 |

| Table 101 | :Transmit Watermark Register Bit Field Descriptions                              | 92 |

| Table 102 | :MIB Control Register Bit Field Descriptions 7                                   | 93 |

| Table 103 | :MIB Statistics Counters                                                         | 94 |

| Table 104:MII Control Register Bit Field Descriptions                                      | 98  |

|--------------------------------------------------------------------------------------------|-----|

| Table 105:MII Status Register Bit Field Descriptions                                       | 100 |

| Table 106:PHY Identifier High Register Bit Field Descriptions                              | 102 |

| Table 107:PHY Identifier Low Register Bit Field Descriptions                               | 102 |

| Table 108:Auto-Negotiation Advertisement Register Bit Field Descriptions                   | 103 |

| Table 109:Auto-Negotiation Link Partner Ability Register Bit Field Descriptions            | 104 |

| Table 110:Auto-Negotiation Expansion Register Bit Field Descriptions                       | 105 |

| Table 111:Auto-Negotiation Next Page Transmit Register Bit Field Descriptions              | 106 |

| Table 112:Auto-Negotiation Link Partner Next Page Transmit Register Bit Field Descriptions | 107 |

| Table 113:100BASE-X Auxiliary Control Register Bit Field Descriptions                      | 108 |

| Table 114:100BASE-X Auxiliary Status Register Bit Field Descriptions                       | 110 |

| Table 115:100BASE-X Receive Error Counter Bit Field Descriptions                           | 112 |

| Table 116:100BASE-X False Carrier Sense Counter Bit Field Descriptions                     | 112 |

| Table 117:100BASE-X Disconnect Counter Bit Field Descriptions                              | 113 |

| Table 118:100BASE-X Auxiliary Control/Status Register Bit Field Descriptions               | 114 |

| Table 119:100BASE-X Auxiliary Status Summary Register Bit Field Descriptions               | 116 |

| Table 120:Interrupt Register Bit Field Descriptions                                        | 118 |

| Table 121:Auxiliary Mode 2 Register Bit Field Descriptions                                 | 119 |

| Table 122:10BASE-T Auxiliary Error and General Status Register Bit Field Descriptions      | 121 |

| Table 123:Auxiliary Mode Register Bit Field Descriptions                                   | 123 |

| Table 124:Auxiliary Multiple PHY Register Bit Field Descriptions                           | 124 |

| Table 125:Auxiliary Mode 4 Register Bit Field Descriptions                                 | 127 |

| Table 126:Auxiliary Status 2 Register Bit Field Descriptions                               | 128 |

| Table 127:Cable Length                                                                     | 129 |

| Table 128:Auxiliary Status 3 Register Bit Field Descriptions                               | 129 |

| Table 129:Auxiliary Mode 3 Register Bit Field Descriptions                                 |     |

| Table 130:Current Receive FIFO Size                                                        | 130 |

| Table 131:Auxiliary Status 4 Register Bit Field Descriptions                               | 130 |

| Table 132:Receive Packet Discard                                                           | 134 |

| Table 133:Receiver Modes                                                                   | 135 |

| Table 134:RMON Statistics Group (RFC 1757)                                                 | 141 |

| Table 135:Ethernet Like MIB (RFC 1643)                                                     | 142 |

| Table 136:Ethernet MIB (IEEE 802.3u) Selected Counters                                     | 142 |

| Table 137:MAC Control Frame Format                                                         | 143 |

| Table 138:MAC Interrupts                                                                   | 144 |

### Programmer's Reference Guide

| Table 139:Built-in Self Test Status Register Bit Field Descriptions                         | 151 |

|---------------------------------------------------------------------------------------------|-----|

| Table 140:RAM-to-Bit Mapping                                                                |     |

| Table 141:Interrupt Status Register Bit Field Descriptions                                  | 153 |

| Table 142:Interrupt Mask Register Bit Field Descriptions                                    | 154 |

| Table 143:System Backplane to PCI Mailbox Register Bit Field Descriptions                   |     |

| Table 144:System Backplane to PCI Translation 0 Register Bit Field Descriptions             | 160 |

| Table 145:Access Types                                                                      | 160 |

| Table 146:System Backplane to PCI Translation 1 Register Bit Field Descriptions             | 161 |

| Table 147:Vendor ID Register Bit Field Descriptions                                         | 164 |

| Table 148:Device ID Register Bit Field Descriptions                                         |     |

| Table 149:Command Register Bit Field Descriptions                                           |     |

| Table 150:Status Register Bit Field Descriptions                                            | 167 |

| Table 151:Base Address 0 Register Memory Mapped Bit Field Descriptions (BCM4401 B0 Only)    | 169 |

| Table 152:Base Address 0 Register Memory Mapped Bit Field Descriptions                      | 169 |

| Table 153:Base Address 1 Register Bit Field Descriptions                                    | 170 |

| Table 154:Expansion ROM Bar Register Bit Field Descriptions                                 | 171 |

| Table 155:PCI Power Management Capability Register Bit Field Descriptions                   | 173 |

| Table 156:PCI Power Management Control/Status Register Bit Field Descriptions               | 174 |

| Table 157:Power Management Data Items                                                       | 174 |

| Table 158:Power State Encoding                                                              | 175 |

| Table 159:PCI to Bar 0 Window Register Bit Field Descriptions (BCM4401 B0 and Later)        | 176 |

| Table 160:PCI to Bar 0 Window Register Bit Field Descriptions (Rest of BCM440X Family)      | 176 |

| Table 161:SPROM Control Register Bit Field Descriptions                                     | 177 |

| Table 162:BAR 1 Burst Control Register Bit Field Descriptions                               | 178 |

| Table 163:PCI Interrupt Status Register Bit Field Descriptions (BCM4401 B0 and Later)       | 179 |

| Table 164:PCI Interrupt Status Register Bit Field Descriptions (rest of the BCM440X family) | 179 |

| Table 165:PCI Interrupt Mask Register Bit Field Descriptions (BCM4401 B0 and Later)         | 180 |

| Table 166:PCI Interrupt Mask Register Bit Field Descriptions (rest of the BCM440X family)   | 180 |

| Table 167:PCI to System Backplane Mailbox Register Bit Field Descriptions                   | 181 |

| Table 168:Backplane Address Register Bit Field Descriptions (BCM4401 B0 and Later)          | 183 |

| Table 169:Backplane Address Register Bit Field Descriptions (rest of the BCM440X family)    | 183 |

| Table 170:Backplane Data Register Bit Field Descriptions                                    | 184 |

| Table 171:SPROM Layout (BCM4401 B0 and Later)                                               | 188 |

## **Section 1: Overview**

## **BCM440X DESCRIPTION**

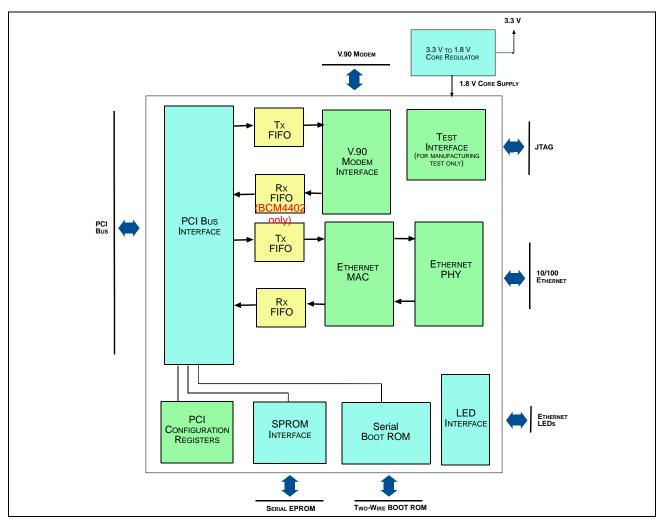

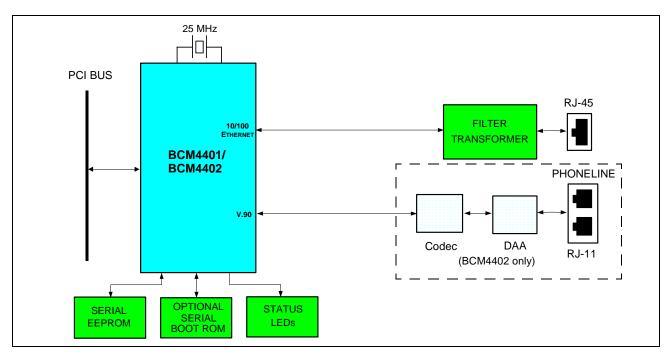

The BCM440X is a fully integrated 10/100 Ethernet MAC/PHY and V.90/V.92 modem (BCM4402 only) device targeted for use in PCI/Mini PCI adapters, and LAN on Motherboard (LOM) implementations. The BCM440X controller provides a PCI 2.2 and Mini PCI 1.0 host interface. Complete WHQL certified drivers for Windows<sup>®</sup> 98, Windows Millennium Edition (ME), Windows 2000, and Windows XP are available for 10/100 Ethernet and V.90/V.92 data/fax/voice (BCM4402 only) functions. Each interface operates concurrently as a separate function.

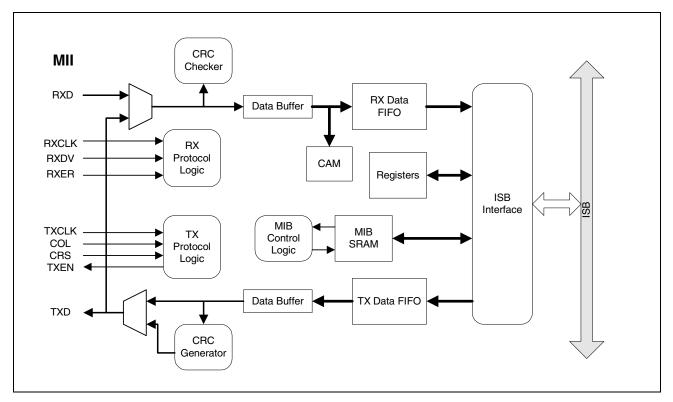

Figure 1: BCM440X Block Diagram

## BCM440X FEATURES

- Combination 10/100 Ethernet MAC/PHY and PCI Soft Modem with concurrent operation

- PCI 2.3, Mini PCI 1.0, and LOM

- Meets PCI Power Management Interface Specification v1.1 for Advanced Power Management

- Fully PC2001 WHQL certified drivers for Windows 98, Windows Millennium Edition, Windows 2000, and Windows XP

Figure 2: BCM440X System Diagram

- 1 KB, 4 KB, or 16 KB serial EEPROM support for MAC address and configuration parameters

- Optional serial boot ROM support for PXE support

- JTAG

- 0.18µ CMOS, 3.3V supply, 3/5V PCI I/O

- Integrated 3.3V to 1.8V regulator

- 33 MHz PCI 2.2 Local Bus

- 128-pin LQFP

## 10/100 ETHERNET MAC/PHY

The BCM440X 10/100 Ethernet function incorporates a complete IEEE 802.3u compliant MAC and PHY. The MAC also supports management functions including RMON, Ethernet-like MIB, and IEEE 802.3u Ethernet MIB. The 10/100 PHY uses Broadcom's advanced Digi- $\Phi^{TM}$  architecture for low power and includes advanced power management. The 10/100 PHY also supports Auto-Negotiation and HP Auto-MDIX functions to eliminate installation errors.

- IEEE 802.3u compliant Transmit and Receive engines

- Transmit and Receive FIFOs (2KB transmit and 4KB receive)

- Full- and Half-Duplex operation

- Full-duplex frame-based Flow Control compliant with IEEE 802.3x

- Internal 64-entry Content Addressable Memory (CAM) for perfect address filtering

- MII Management interface allows control of internal transceiver functions

- Internal MAC and PHY loopbacks

- Integrated MIB counters supporting RMON, Ethernet-like MIB, and IEEE 802.3™ Ethernet MIB

- Low power 10BASE-T/100BASE-TX IEEE 802.3u Fast Ethernet Transceiver

- Auto-Negotiation support with Next Page

- Baseline Wander correction

- Link LEDs (Link, Activity, Speed, Collision)

- Automatic Power-Down mode

- Unique Energy Detection Circuit enabling Intelligent Power Management

- HP Auto-MDIX

- Cable Length Indication

- Cable lengths greater than 120 meters supported

## CODEC MODEM FUNCTION (BCM4402 ONLY)

The BCM440X controller includes a data/fax modem interface to an external serial Modem Codec/DAA, allowing implementation of a complete, low-cost data/fax/voice soft modem. The data/fax Software Modem driver is available for Windows 98, Windows Millennium Edition, Windows 2000, and Windows XP.

## **DEVICE INITIALIZATION AND RESET**

Refer to the following sections for device initialization and reset:

- Section 2: "Backplane":

- Section 3: "DMA": see "Descriptor Processor Channel Initialization" on page 45 and "Descriptor Processor Channel Reset" on page 45.

- Section 4: "Codec Core (BCM4402 only)":

- Section 5: "Ethernet 10/100 Core": see "Ethernet Core Initialization" on page 162.

- Section 6: "PCI Core":

- Section 7: "Programming Hints": see "Reset" on page 203

## **RELATED DOCUMENTS**

- BCM4401 or BCM4402 data sheet

- Codec data sheet (from codec vendor)

- DAA data sheet (from DAA vendor)

## Section 2: Backplane

## BACKPLANE, CORES, AND AGENTS

The BCM440X uses a system backplane to connect all of its functional blocks. These functional blocks, known as cores, use the Open Core Protocol (OCP) interface to communicate with agents attached to the system backplane.

The BCM440Xis a member of a family of chips built using the same system backplane architecture. Each member of the family contains a different set of cores, but shares basic architectural features such as address space definition, interrupt and error architecture, and backplane register definitions. The information contained in this chapter is applicable to the entire family of chips and can contain information that is not relevant to the BCM440X.

In this chapter, the term *host interface core* refers to cores that implement slave devices that are accessible to outside hosts. The PCI and PCMCIA cores are host interface cores. *Communications cores* are those that implement networking protocols such as InsideLine or Ethernet.

The BCM440X contains three cores:

- Ethernet MAC

- Codec/V.90 (not applicable to the BCM4401)

- PCI

The BCM440X also contains an Ethernet PHY that is accessed using the Ethernet MAC core.

Each core can have an initiator agent that passes read and write requests onto the system backplane and a target agent that returns responses to those requests. Not all cores contain both an initiator and a target agent. Initiator agents are present in cores that contain host interfaces (PCI, PCMCIA), embedded processors (MIPS), or DMA processors associated with communications cores. All cores other than PCMCIA have a target agent.

### **SUPPORTED OPERATIONS**

The system backplane defines four types of bus transactions: reads, writes, exclusive reads, and broadcast writes. The BCM440X does not implement exclusive reads. Broadcast writes are used only to update system backplane configuration registers and are performed by accessing the PCI core's BroadcastAddr register and then writing the desired value to the PCI core's BroadcastData register.

### ARBITRATION

The system backplane arbitration mechanism consists of a high-priority Time-Division Multiplexing (TDM) allocation and a lower-priority token passing ring. Allocated TDM slots give cores a right of first refusal for system backplane accesses during that slot. By default, all cores compete for the round robin token. All of the other cores compete for the round robin token.

If necessary, the SBBWA0 configuration register (see "System Backplane Bandwidth Allocation Table 0 Register (SBBWA0, offset 0xFA0)" on page 16) and the SBPOLICY field of the SBIMSTATE configuration register (see "System Backplane Initiator State Register (SBIMSTATE, offset 0xF90)" on page 12) in the cores can be used to adjust system backplane arbitration priority.

In the BCM440X, the arbitration scheme cannot be changed by register accesses. TDM slots are not used, and all cores compete for the round robin token.

### INTERRUPT ARCHITECTURE

Each interrupt-generating core collects interrupt conditions internally and outputs a single interrupt signal over one of the sbFlags system backplane signals. sbFlags[2:0] are allocated to cores that raise interrupts as shown in Table 1.

#### Table 1: Interrupt Cores

| Bit | Core         |

|-----|--------------|

| 0   | PCI          |

| 1   | Ethernet MAC |

| 2   | Codec        |

The core target agents do not use the Interrupt signal to report interrupts. As a result, the SBINTMODE and SBINTFLG fields of the SBTMCONFIGLOW registers (see "System Backplane Target Configuration Low Register (SBTMCONFIGLOW, offset 0xFB8)" on page 20 and "System Backplane Target Configuration High Register (SBTMCONFIGHIGH, offset 0xFBC)" on page 21) are not used. Instead, cores use sFlag[0] to report interrupts and use the SBTTPSFLAGNUM0 field in the SBTPSFLAG register (see "System Backplane Target OCP Slave Flag Control Register (SBTPSFLAG, offset 0xF18)" on page 10) to route the interrupt to the correct sbFlag in the system backplane.

### **ERROR ARCHITECTURE**

There are three types of errors that occur on the system backplane: in-band error responses to read requests, out-of-band error assertions in response to write requests, and time-outs.

The system backplane supports two error reporting mechanisms: in-band error responses and an out-of-band shared error signal, SBERROR. Configuration register settings control which errors are reported on SBERROR and which cores receive SBERROR indications. In addition, each initiator and target agent contains error configuration and logging registers.

A read request causes an error response when it times out, when the target address is unclaimed by any core, and when the address is an undefined address within a core's address space. Time-outs are logged in the SBTOERR field of the SBIMSTATE register (see "System Backplane Initiator State Register (SBIMSTATE, offset 0xF90)" on page 12) and the other errors are logged in the SBIBERR field. In all cases, an error response is returned to the initiating core.

Because all writes on the system backplane are posted, there is no mechanism for in-band error indications to the initiating core. An attempt to write to an unclaimed address is logged in the SBIBERR field of the initiating agent and reported to the initiating core. Request time-outs are logged in the SBTOERR field. In response to these errors, the MIPS core generates a non-maskable interrupt and the PCI core and DMA engines log the error and assert an error interrupt.

**Note:** The setting of the InBandErrMode field also affects the reporting of read errors.

For write errors detected in the target, the initiating core does not receive any direct error indication. In the default configuration, out-of-band errors reported by any core assert the SBERROR signal. The SBERROR signal is sent to the MIPS core where it causes a non-maskable interrupt. Driver software must traverse the target cores examining error log bits to identify and clear the source of the out-of-band errors. Cores can not respond to system backplane accesses when the Reset or Reject fields of the SBTMSTATELOW register (see "System Backplane Target State Low Register (SBTMSTATELOW, offset 0xF98)" on page 14) are set or when the ClockEnable field of the SBTMSTATELOW register is clear.

## ADDRESS SPACE MAP

The BCM440X address space is described in Table 2. The addresses of all on-chip resources are restricted to the first 512 MB so that they can be accessed from each of the MIPS *X* segments, giving software maximum flexibility to determine the mapability and cacheability of each reference.

| A                        | ddress Range | Contents                        | Size   |

|--------------------------|--------------|---------------------------------|--------|

| 0x0000_0000              | 0x07FF_FFFF  | PCI                             | 128 MB |

| 0x0000_0000 <sup>a</sup> | 0x07FF_FFFF  | SDRAM                           | 128M   |

| 0x0800_0000              | 0x0FFF_FFF   | PCI                             | 128M   |

| 0x1000_0000 <sup>b</sup> | 0x17FF_FFFF  | SDRAM byte-swap                 | 128 MB |

| 0x1800_0000 <sup>a</sup> | 0x1800_0FFF  | Ethernet MAC registers          | 4k     |

| 0x1800_1000 <sup>b</sup> | 0x1800_1FFF  | Codec registers (BCM4402 only)  | 4k     |

| 0x1800_2000 <sup>b</sup> | 0x1800_2FFF  | PCI registers                   | 4k     |

| 0x1800_3000 <sup>b</sup> | 0x1800_FFFF  | Reserved                        | -      |

| 0x1900_0000              | 0x1EFF_FFFF  | Reserved                        | -      |

| 0x1F00_0000 <sup>a</sup> | 0x1F0F_FFFF  | PCMCIA memory accesses          | 1 MB   |

| 0x1F10_0000 <sup>a</sup> | 0x1F1F_FFFF  | PCMCIA I/O accesses             | 1 MB   |

| 0x1F20_0000 <sup>a</sup> | 0x1F2F_FFFF  | PCMCIA configuration accesses   | 1 MB   |

| 0x1F30_0000 <sup>a</sup> | 0x1F7F_FFFF  | Reserved                        | _      |

| 0x1F80_0000 <sup>a</sup> | 0x1FBF_FFFF  | Configurable External Interface | 4 MB   |

| 0x1Fc0_0000 <sup>a</sup> | 0x1FFF_FFFF  | Flash                           | 4 MB   |

| 0x4000_0000              | 0x7FFF_FFFF  | PCI                             | 1 GB   |

a. Not supported in BCM440X.

b. Enumeration Space.

All resources are mapped in one of these six address regions: SDRAM space, PCI space, big-endian SDRAM space enumeration space, core-dependent space, and external interface space.

The lower part of the address space is used to access up to 128MB of external SDRAM. The next 128MB region supplies a 128MB window onto an external PCI space. See Section 6: "PCI Core" for information on mapping internal addresses to PCI addresses. The PCI address space can be remapped dynamically to another otherwise unused address range. In particular, it can be remapped to the range starting at 0 to support systems that lack SDRAM. In this case, the SDRAM address region must be disabled.

The third 128MB region provides a big-endian window on to SDRAM space. Write accesses to this region are byte-swapped before being written to SDRAM and read accesses are byte-swapped before being returned to the system backplane.

Each core supports a 4KB internal register interface space that contains configuration control and status registers and, in most cases, the complete programming interface for the core. The configuration block occupies the last 256 bytes of these spaces.

These register interface spaces are allocated contiguously in the region designated as enumeration space in Table 2 on page 7. Because the register interface spaces are contiguous and contain configuration information at known offsets, software can determine which cores a present by reading the SBIDHIGH register (see "System Backplane Identification High Register (SBIDHIGH, offset 0xFFC)" on page 26) in each register space starting at 0x18000FFC and incrementing by 4KB until an invalid address is encountered. The SBIDHIGH register contains identifying information for its core. The address space after the end of the external device region is reserved for cores that require more than 4KB for their programming models.

## **CORE CONFIGURATION SPACE REGISTERS**

Each core contains a configuration block at offset 0xF00 in the host interface space. Registers in this block are used to identify cores, define address spaces, control clocks and reset, and setup arbitration, interrupt, and error routing information. The register definitions and many characteristics and reset values are common across all cores, but there are differences between core configurations that are described below.

These registers are part of the agent rather than the core. In particular, they are not affected by the core reset signals.

Table 3 shows the configuration registers that are present in at least one core.

| Address Offset | Name                                          | Abbreviation   | Туре   | Buffered | See |

|----------------|-----------------------------------------------|----------------|--------|----------|-----|

| 0xF08          | Initiator OCP slave flag control <sup>a</sup> | SBIPSFLAG      | R/W    | No       | 9   |

| 0xF18          | Target OCP slave flag control <sup>a</sup>    | SBTPSFLAG      | R/W    | No       | 10  |

| 0xF60          | Address match 3 <sup>a</sup>                  | SBADMATCH3     | R/W    | Yes      | 10  |

| 0xF68          | Address match 2 <sup>a</sup>                  | SBADMATCH2     | R/W    | Yes      | 10  |

| 0xF70          | Address match 1 <sup>a</sup>                  | SBADMATCH1     | R/W    | Yes      | 11  |

| 0xF90          | Initiator state                               | SBIMSTATE      | R/W    | No       | 12  |

| 0xF94          | Interrupt vector                              | SBINTVEC       | R/W    | No       | 13  |

| 0xF98          | Target state low                              | SBTMSTATELOW   | R/W    | No       | 14  |

| 0xF9C          | Target state high                             | SBTMSTATEHIGH  | R/W    | No       | 15  |

| 0xFA0          | Bandwidth allocation table 0                  | SBBWA0         | R/W    | Yes      | 16  |

| 0xFA8          | Initiator configuration low                   | SBIMCONFIGLOW  | R/W    | Yes      | 17  |

| 0xFAC          | Initiator configuration high                  | SBIMCONFIGHIGH | R/W    | Yes      | 18  |

| 0xFB0          | Address match 0                               | SBADMATCH0     | R/W    | Yes      | 19  |

| 0xFB8          | Target configuration low                      | SBTMCONFIGLOW  | R/W    | Yes      | 20  |

| 0xFBC          | Target configuration high                     | SBTMCONFIGHIGH | R/W    | Yes      | 21  |

| 0xFC0          | Broadcast configuration register              | SBBCONFIG      | R/W    | Yes      | 22  |

| 0xFC8          | Broadcast state register                      | SBBSTATE       | R/W    | No       | 23  |

| 0xFD8          | Activate configuration                        | SBACTCNFG      | pseudo | No       | 24  |

| 0xFE8          | Flag status <sup>a</sup>                      | SBFLAGST       | R      | No       | 24  |

| 0xFF8          | Identification low                            | SBIDLOW        | R      | No       | 25  |

| 0xFFC          | Identification high                           | SBIDHIGH       | R      | No       | 26  |

#### Table 3: Core Configuration Space Registers

a. Not included in all cores.

### **UPDATING BUFFERED REGISTERS**

Registers designated as buffered are designed to be updated simultaneously in all agents to guarantee proper SB operation. In order to update a buffered register, software must perform writes to all cores where the register's value changes and then must perform a broadcast write to the SBACTCNFG pseudo-register (see "System Backplane Activate Configuration Register (SBACTCNFG, offset 0xFD8)" on page 24) to commit the previous writes. This write is executed by writing the value 0xFD8 to the PCI core's BroadcastAddress register (see "Broadcast Address Register (BroadcastAddress, offset 0x50)" on page 173) and then writing a 0 to the PCI Core's BroadcastData register (see "Broadcast Data Register (BroadcastData, offset 0x54)" on page 173).

If subsequent operations must wait for the buffered register update to complete, software should perform another access to a register in the PCI core. That access does not complete until after the broadcast write completes. None of the buffered registers on the BCM440X contain writable fields, so these procedures are not necessary.

# SYSTEM BACKPLANE INITIATOR OCP SLAVE FLAG CONTROL REGISTER (SBIPSFLAG, OFFSET 0xF08)

The four-byte SBIPSFLAG register is used to route backplane flags to cores that handle interrupts. Each core that is capable of signaling an interrupt has an associated backplane flag. For cores that do not handle interrupts, this register is read-only and contains the value 0x0. For the MIPS core, this register is writable and maps interrupts from selected cores onto MIPS interrupts 1 through 4.

(For BCM4401 B0 only) For the PCI core, this register is read-only and is initialized so that input flag N is the interrupt used by the Nth core in enumeration space. See "PCI Interrupt Status Register (PCIIntStatus, offset 0x90)" on page 196 for more information on routing interrupts to the PCI bus.

| Field | Name          | Description                                                       | Access | Default |

|-------|---------------|-------------------------------------------------------------------|--------|---------|

| 31:30 | Reserved      | _                                                                 | _      | _       |

| 29:24 | IntFlag4 (F4) | Interrupt Flag 4                                                  | _      | -       |

|       |               | This field selects which core interrupt is routed to interrupt 4. |        |         |

| 23:22 | Reserved      | -                                                                 | _      | -       |

| 21:16 | IntFlag3 (F3) | Interrupt Flag 3                                                  | _      | _       |

|       |               | This field selects which core interrupt is routed to interrupt 3. |        |         |

| 15:14 | Reserved      | -                                                                 | _      | -       |

| 13:8  | IntFlag2 (F2) | Interrupt Flag 2                                                  | _      | _       |

|       |               | This field selects which core interrupt is routed to interrupt 2. |        |         |

| 7:6   | Reserved      | -                                                                 | _      | _       |

| 5:0   | IntFlag1 (F1) | Interrupt Flag 1                                                  | _      | _       |

|       |               | This field selects which core interrupt is routed to interrupt 1. |        |         |

#### Table 4: System Backplane Initiator OCP Slave Flag Control Register Bit Field Descriptions

See "System Backplane Interrupt Vector Register (SBINTVEC, offset 0xF94)" on page 13 for information on routing multiple core interrupts to MIPS interrupt 0. See "Interrupt Architecture" on page 6 for more information on interrupts.

# SYSTEM BACKPLANE TARGET OCP SLAVE FLAG CONTROL REGISTER (SBTPSFLAG, OFFSET 0xF18)

The four-byte SPTPSFLAG register is read-only and is used for interrupt routing. The entire register contains 0 for cores that do not generate interrupts.

| Table 5: System Backplane | Target OCP Slave Flag | Control Register Bit Field Descript | ions |

|---------------------------|-----------------------|-------------------------------------|------|

|                           |                       |                                     |      |

| Field | Name               | Description                                                                                                                                                  | Access | Default |  |

|-------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|--|

| 31:7  | Reserved           | -                                                                                                                                                            | RO     | 0       |  |

| 6     | SBTPSFLAG0EN0 (FE) | Target OCP Slave Flag 0 Enable 0                                                                                                                             | RO     |         |  |

|       |                    | This field is set to 1, indicating that the interrupt is always sent on the system backplane.                                                                |        |         |  |

| 5:0   | SBTPSFLAGNUM0 (FN) | Target OCP Slave Flag Number 0                                                                                                                               | RO     | See     |  |

|       |                    | This field specifies the number of the sbFlag system backplane flag used for the interrupt generated by this core. It is set to the values shown in Table 6. |        | Table 6 |  |

| Table 6: sbFlag Values |              |  |

|------------------------|--------------|--|

| Flag Number            | Core         |  |

| 0                      | PCI          |  |

| 1                      | Ethernet MAC |  |

| 2                      | Codec        |  |

| 3-63                   | Reserved     |  |

The remaining fields, SBTPSFLAG0ENx and SBTPSFLAGNUMx, where x is non-zero, always contain zero.

See "System Backplane Interrupt Vector Register (SBINTVEC, offset 0xF94)" on page 13 and "System Backplane Initiator OCP Slave Flag Control Register (SBIPSFLAG, offset 0xF08)" on page 9 for information on how interrupts are routed from the system backplane flags to cores that handle interrupts.

### SYSTEM BACKPLANE ADDRESS MATCH 3 REGISTER (SBADMATCH3, OFFSET 0xF60)

See "System Backplane Address Match 1 Register (SBADMATCH1, offset 0xF70)".

### SYSTEM BACKPLANE ADDRESS MATCH 2 REGISTER (SBADMATCH2, OFFSET 0xF68)

See "System Backplane Address Match 1 Register (SBADMATCH1, offset 0xF70)".

These four-byte SBADMATCHx registers are used by some cores to define additional address spaces beyond the standard 4KB host interface space defined by the SBADMATCH0 register. Use of these registers is described in the OCP Interface section of the documentation for each core that requires an additional address space.

| Field                            | Name               | Description                                                                                                                                                                                                                                                                                                                                                                                                                      | Access | Default |

|----------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| 31:8 (Type 0)                    | AddressBase (AB)   | Address Base                                                                                                                                                                                                                                                                                                                                                                                                                     | _      | _       |

| 31:12 (Type 1)<br>31:16 (Type 2) |                    | This field contains the base address for this range.                                                                                                                                                                                                                                                                                                                                                                             |        |         |

|                                  | NegativeMatch (NM) | Negative Match                                                                                                                                                                                                                                                                                                                                                                                                                   | -      | -       |

| only)                            |                    | When this field is set to 1, this address match register<br>performs subtractive decoding, accepting all addresses<br>that do not match the range specified by the<br>AddressBase and AddressSize registers. When cleared<br>to 0, positive address matching is used.                                                                                                                                                            |        |         |

|                                  | AddressEnable (AE) | Address Enable                                                                                                                                                                                                                                                                                                                                                                                                                   | _      | _       |

| only)                            |                    | When this field is set to 1, the address matching<br>performed by this register is enabled. When cleared to 0,<br>the address range specified by this register is disabled.<br>Type 0 address ranges are always enabled.                                                                                                                                                                                                         |        |         |

| 7:3 (Type 0)                     | AddressSize (AS)   | Address Size                                                                                                                                                                                                                                                                                                                                                                                                                     | _      | -       |

| 8:3 (Types 1 and 2)              |                    | This field specifies the size of the address region. It contains the index of the most-significant address bit that does not participate in the match. System backplane address bits [31:AddressSize+1] are compared to AddressBase[31:AddressSize+1] to determine whether the address matches the range specified by this register. This field is read only for address types 0 and 1 and has a minimum value of 15 for type 2. |        |         |

| 1:0                              | AddressType (AT)   | Address Type                                                                                                                                                                                                                                                                                                                                                                                                                     | -      | -       |

|                                  |                    | This read-only field specifies the kind of address<br>matching performed by this register. If this field contains<br>0, the address register performs a positive decode on a<br>fixed range. Address types 1 and 2 can perform either<br>positive or subtractive decodes, and address type 2<br>supports a programmable region size.                                                                                             |        |         |

#### Table 7: System Backplane Address Match Registers Bit Field Descriptions

### SYSTEM BACKPLANE INITIATOR STATE REGISTER (SBIMSTATE, OFFSET 0xF90)

The four-byte SBIMSTATE register is writable and contains the value 0x0 for the MIPS core and 0x20 for all other cores on device reset. This register contains information about the core's use of the system backplane bus.

| Field | Name             | Description                                                                                                                                                                                                                                                  | Access | Default |

|-------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|

| 31:19 | Reserved         |                                                                                                                                                                                                                                                              | R/W    | _       |

| 18    | TimeOut (TO)     | Timeout                                                                                                                                                                                                                                                      | R/W    | _       |