# PCI/EISA Bus-Master Adapter Driver Technical Reference

Members of the 3Com EtherLink® III and Fast EtherLink families of adapters

For 3Com User Group Information 1-800-NET-3Com or your local 3Com office

Manual Part Number 09-0681-001B Printed May 1995. Printed in the U.S.A. 3Com Corporation 5400 Bayfront Plaza Santa Clara, California, USA 95052-8145 © 3Com Corporation, 1995. All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without permission from 3Com Corporation.

3Com Corporation reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of 3Com Corporation to provide notification of such revision or change.

3Com Corporation provides this documentation without warranty of any kind, either implied or expressed, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. 3Com may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

#### UNITED STATES GOVERNMENT LEGENDS:

If you are a United States government agency, then this documentation and the software described herein are provided to you subject to the following restricted rights:

#### For units of the Department of Defense:

*Restricted Rights Legend:* Use, duplication or disclosure by the Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) for restricted Rights in Technical Data and Computer Software clause at 48 C.F.R. 52.227-7013. 3Com Corporation, 5400 Bayfront Plaza, Santa Clara, California 95052-8145.

#### For civilian agencies:

*Restricted Rights Legend:* Use, reproduction or disclosure is subject to restrictions set forth in subparagraph (a) through (d) of the Commercial Computer Software - Restricted Rights Clause at 48 C.F.R. 52.227-19 and the limitations set forth in 3Com Corporation's standard commercial agreement for the software. Unpublished rights reserved under the copyright laws of the United States.

Unless otherwise indicated, 3Com registered trademarks are registered in the United States and may or may not be registered in other countries.

3Com and EtherLink are registered trademarks of 3Com Corporation.

# Contents

#### **Chapter 1 Introduction**

Summary of Features 1-1 PCI/EISA Bus-Master Adapter Features 1-2 Nomenclature 1-2 Typographic Conventions 1-3 Register Definitions Legend 1-3

#### Chapter 2 PCI/EISA Bus Master Versus PIO

Functional Differences from PIO 2-1

Data Transfer Modes 2-1

Extra Register Window 2-1

Statistics Registers 2-1

Large Packet Support 2-2

Media-Related Functions 2-2

Station Address Masking Function 2-2

New Registers 2-3

Commands Not Supported 2-3

New Interrupt Bit 2-3

Miscellaneous Details 2-3

Differences Between PCI and EISA Bus Master Adapters 2-3

PIO/Bus Master Nomenclature 2-4

#### **Chapter 3 Adapter Operation**

Basic Operational Concepts 3-1 Register Windows 3-2 Bit-Widths of Register Accesses 3-2 Command Register 3-2 Command Summary 3-3 IntStatus Register 3-4 Optimized Adapter Operations 3-4 Timer Register 3-4 Data Transfer Modes 3-4 Programmed I/O 3-4 Bus Master 3-5 BIOS ROM 3-5 Configuration and Initialization 3-6

System Reset 3-6 Forced Configuration 3-6 Global Reset 3-6 PCI Adapter Configuration 3-7 EISA Adapter Configuration 3-7 Adapter Initialization 3-7 Serial EEPROM 3-8 Selecting the Media Port 3-8 ResetOptions 3-9 Setting the RAM Partition 3-9 Station Address 3-9 Broadcast Address 3-9 Multicast Addresses 3-9 Capabilities Word 3-9 Frame Transmission 3-10 Frame Transmission Model 3-10 Transmit Data Writes 3-10 Programmed I/O 3-10 Bus Master 3-10 Frame Start Header 3-11 Completing a Transmit Frame Download 3-12 Padding to a Dword Boundary 3-12 Issuing a TxDone Command 3-12 Padding to Minimum Frame Length 3-12 Initiating Frame Transmission 3-12 Transmission Completion 3-13 Updating the Status 3-13 Multiple Transmit Completions 3-13 Frame Transmission Errors 3-13 Optimized Transmit Operations 3-14 Early Transmission Start 3-14 Frame Reception 3-14 Frame Reception Model 3-14 Top Frame 3-15 Normal Frame Reception 3-15 Receive Data Reads 3-15 Programmed I/O 3-15 Bus Master 3-15 RxStatus and RxError 3-16 Discarding the Top Frame 3-16 Queued Receives 3-16 Receive Frame Size Limits 3-16 Optimized Frame Reception 3-16 Early Receive Indications 3-16 Discarding a Frame During Reception 3-17 Interrupts and Indications 3-18 Interrupts Versus Indications 3-18 Determining the Cause of an Interrupt 3-18 IntStatus 3-18

Interrupt Acknowledgment 3-18 Interrupt and Indication Enable Mechanisms 3-18 Statistics 3-20 Transmit Statistics 3-20 Receive Statistics 3-21

#### Chapter 4 Register Listings

I/O Model 4-1 Register Definitions 4-3 AddressConfig (EISA Only) 4-3 Definition 4-3 BadSSD 4-5 Definition 4-5 BytesRcvdOk 4-5 Definition 4-5 BytesXmittedOk 4-6 Definition 4-6 CarrierLost 4-6 Definition 4-6 Command 4-7 Definition 4-7 Command Register Format 4-7 Supported Commands 4-8 Reserved Command Codes 4-13 ConfigControl (EISA Only) 4-14 Definition 4-14 EepromCommand 4-15 Definition 4-15 EepromData 4-17 Definition 4-17 FifoDiagnostic 4-18 Definition 4-18 FramesDeferred 4-19 Definition 4-19 FramesRcvdOk 4-19 Definition 4-19 FramesXmittedOk 4-20 Definition 4-20 IndicationEnable 4-20 Definition 4-20 InternalConfig 4-21 Definition 4-21 InterruptEnable 4-23 Definition 4-23 IntStatus 4-24 Definition 4-24 LateCollisions 4-26 Definition 4-26

MacControl 4-26 Definition 4-26 ManufacturerId (EISA Only) 4-28 Definition 4-28 MasterAddress 4-28 Definition 4-28 MasterLen 4-29 Definition 4-29 MasterStatus 4-30 Definition 4-30 MediaStatus 4-31 Definition 4-31 MultipleCollisions 4-33 Definition 4-33 Network Diagnostic 4-34 Definition 4-34 OtherInt 4-36 Definition 4-36 PhysicalMgmt 4-36 Definition 4-36 ProductId (EISA Only) 4-37 Definition 4-37 ResetOptions 4-38 Definition 4-38 ResourceConfig (EISA Only) 4-40 Definition 4-40 RomControl (EISA Only) 4-41 Definition 4-41 RxData 4-42 Definition 4-42 RxEarlyThresh 4-43 Definition 4-43 RxError 4-45 Definition 4-45 RxFilter 4-46 Definition 4-46 RxFree 4-47 Definition 4-47 RxOverruns 4-47 Definition 4-47 RxStatus 4-48 Definition 4-48 SingleCollisionFrames 4-49 Definition 4-49 SqeErrors 4-49 Definition 4-49 StationAddress 4-50 Definition 4-50 StationMask 4-50

Definition 4-50 Timer 4-51 Definition 4-51 TxAvailableThresh 4-51 Definition 4-51 TxData 4-52 Definition 4-52 Padding to Double-Word Boundary 4-52 TxFree 4-53 Definition 4-53 TxStartThresh 4-53 Definition 4-53 TxStatus 4-54 Definition 4-54 UpperFramesOk 4-55 Definition 4-55 VcoDiagnostic 4-55 Definition 4-55

#### **Chapter 5 Adapter Configuration**

PCI Configuration Overview 5-1 PCI Configuration Registers 5-2 VendorId 5-2 DeviceId 5-2 PciCommand 5-3 PciStatus 5-3 ClassCode 5-4 LatencyTimer 5-4 HeaderType 5-4 IoBaseAddress 5-5 BiosRomControl 5-5 InterruptLine 5-5 InterruptPin 5-5 MinGnt 5-6 MaxLat 5-6 ResetOptions 5-6 InternalConfig 5-6 EISA Configuration Overview 5-7 EISA Configuration Registers 5-8 EEPROM Data Format 5-8 PCI Data Format 5-8 EISA Data Format 5-9 Data Field Details 5-10 3Com Node Address 5-10 DeviceId (PCI Only) 5-10 ProductId (EISA Only) 5-10 Manufacturing Data - Date 5-10 Manufacturing Data - Division 5-10 Manufacturing Data - Product Code 5-10 ManufacturerId 5-11 PciParm (PCI Only) 5-11 RomInfo (PCI Only) 5-11 OEM Node Address 5-11 AddressConfig (EISA Only) 5-11 ResourceConfig (EISA Only) 5-12 Software Information 5-12 Compatibility Word 5-12 Capabilities Word 5-13 InternalConfig 5-14 Software Information 2 5-14 Checksum 5-14

#### Appendix A Errata List and Software Solutions

Introduction A-1 PCI Adapters (3C590 and 3C595): A-1 EISA Adapters (3C592 and 3C597): A-1 All Adapters A-2 Useful Tips A-3

# **Figures**

- 1-1. Register Bit Map Legend 1-3

- 3-1. Interrupt and Indication Enable Mechanisms 3-19

- 4-1. Register Bit Map Legend 4-3

- 4-2. **RxData** Example 4-42

- 4-3. **TxData** Example 4-52

- 5-1. PCI Configuration Registers 5-2

х

# **Tables**

4-1. ROM Configuration Table 4-4

4-2. Loopback Modes with Values for **NetworkDiagnostic**, **MacControl**, and **PhysicalMgmt** Registers 4-35

- 5-1. PCI EEPROM Data Format 5-8

- 5-2. EISA EEPROM Data Format 5-9

- 5-3. Code Numbers for 3Com 3C Numbers 5-10

# Chapter 1 Introduction

This manual defines the programming interface supported by first-generation bus mastering adapters for the PCI and EISA buses running at speeds of 10 or 100 Mbps.

This manual is for software engineers and test engineers to use as a reference in writing device drivers, diagnostics, and production test software. PCI and EISA bus master adapters share many of the same characteristics. In this manual, differences are clearly indicated as "PCI Only" or "EISA Only." If there is no such indication, the information is valid for either type of adapter.

# Summary of Features

PCI/EISA bus master adapters are based upon the EtherLink<sup>®</sup> III adapter architecture. PCI/EISA bus master adapters have a programming interface similar to that of the first-generation programmed input/output (PIO) and later adapters, augmented by a single-fragment bus master data transfer mode.

The PCI/EISA bus-master bus architecture adds specifications for several optional extensions to the PIO architecture. Bus master adapters indicate their support for these extensions to the software via a new Capabilities Word in the EEPROM.

The PCI/EISA bus master adapter architecture includes support for the 100BASE-TX/FX 100 Mbps signaling standard and the three 10 Mbps Ethernet signaling standards: 10BASE-T, 10BASE2, and 10BASE5. The PCI/EISA bus master architecture can also support other 10 Mbps and 100 Mbps signaling schemes (such as 100BASE-T4) using the Media Independent Interface. Adapters based upon the PCI/EISA bus master architecture will include various combinations of these media ports. Drivers may be written to support all combinations of these available media ports automatically.

New features supported by all PCI/EISA bus master adapters are CRC passthrough, the TxDone command, large packet handling, an extended deference mechanism, and individual address bit-masking.

PCI/EISA bus master adapters support a variable amount of packet buffer RAM. Since different adapters have differing amounts of RAM installed, drivers written for these adapters must allow for different amounts. The allocation of RAM between the receive and transmit functions is configurable through the **InternalConfig** register.

### **PCI/EISA Bus-Master Adapter Features**

PCI/EISA bus master architecture uses EtherLink III PIO architecture with fragment bus master extensions. To support bus master operations, a number of registers have been added in Window 7.

This architecture supports the following:

- 100 Mbps signaling standard (100BASE-TX)

- 10 Mbps signaling standards (10BASE-T, 10BASE2, and 10BASE5)

- 100BASE-T4 signaling standard through the Media Independent Interface (MII)

- Up to 128 KB of packet buffer RAM, which can be divided 1:1, 3:1, or 5:3 between the receive and transmit functions

- Packet sizes up to 4490 bytes

- CRC passthrough for bridging applications, via a static configuration option on receive and a frame-by-frame basis on transmit

- The TxDone command, to eliminate the need to dword pad the transmit data

- **8** K, 16 K, 32 K or 64 K BIOS ROM

# Nomenclature

The following nomenclature is used throughout this manual:

| Indications         | The reporting of any interesting event on the adapter. Any indication may be configured to cause an interrupt. |

|---------------------|----------------------------------------------------------------------------------------------------------------|

| Interrupts          | The actual assertion of the host machine's interrupt signal.                                                   |

| Download            | The process of transferring transmit data from system memory to the adapter.                                   |

| Upload              | The process of transferring receive data from the adapter to system memory.                                    |

| Byte                | An 8-bit wide quantity of data.                                                                                |

| Word                | A 16-bit wide quantity of data (2 bytes).                                                                      |

| Double Word (dword) | A 32-bit wide quantity of data (4 bytes).                                                                      |

# **Typographic Conventions**

The following typefaces are used to distinguish between object types.

| Object Type                   | Example    | Typeface                                                                  |

|-------------------------------|------------|---------------------------------------------------------------------------|

| Register Name                 | RxStatus   | Helvetica bold font; first character and embedded words capitalized       |

| Signal or Register Field Name | txComplete | Times italic font, first character lower case, embedded words capitalized |

| Code or Command Name          | RxEnable   | Courier font, first character and embedded words capitalized              |

# **Register Definitions Legend**

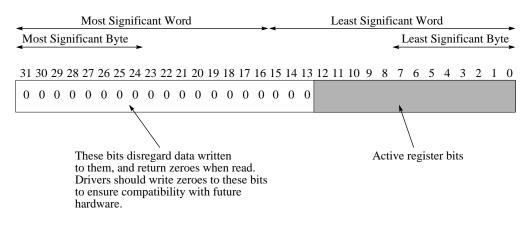

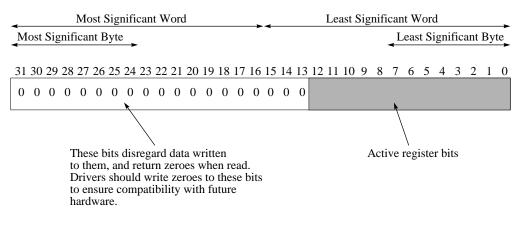

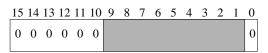

The figure below provides a legend for interpreting the register bit map diagrams.

Figure 1-1. Register Bit Map Legend

# Chapter 2 PCI/EISA Bus Master Versus PIO

This chapter lists the ways in which PCI/EISA bus master adapters differ programmatically from PIO adapters. It also explains the few differences between PCI and EISA bus master adapters. Refer to the next chapter for an introduction to adapter operation.

# **Functional Differences from PIO**

This section lists the major differences between PCI/EISA bus master and PIO adapters.

#### **Data Transfer Modes**

PCI/EISA adapters support fragment-based bus master transfer. The **MasterStatus** register provides transfer-complete bits that can be used for polling. A *transferInt* bit is included in **IntStatus** so that interrupts can be generated upon the completion of bus master transfers.

#### **Extra Register Window**

PCI/EISA bus master adapters implement Window 7, which contains the **MasterStatus**, **MasterAddress**, and **MasterLen** registers to support bus master operations.

### **Statistics Registers**

On PCI/EISA bus master adapters, some of the statistics registers have been increased in size to support the higher data rate required by 100 Mbps operation. The registers and their sizes for PIO adapters and bus master adapters are shown below.

| Register Name         | PIO Adapter<br>Size (bits) | Bus Master Adapter<br>Size (bits) |

|-----------------------|----------------------------|-----------------------------------|

| BytesXmittedOk        | 16                         | 16                                |

| BytesRcvdOk           | 16                         | 16                                |

| FramesDeferred        | 8                          | 8                                 |

| FramesRcvdOk          | 8                          | 10                                |

| FramesXmittedOk       | 8                          | 10                                |

| RxOverruns            | 8                          | 8                                 |

| LateCollisions        | 8                          | 8                                 |

| SingleCollisionFrames | 6                          | 8                                 |

| MultipleCollisions    | 6                          | 8                                 |

| SqeErrors             | 4                          | 4                                 |

| CarrierLost           | 4                          | 4                                 |

**FramesRcvdOk** and **FramesXmittedOk** are 10 bits wide, yet reside in 8-bit wide register spaces, so their high-order bits are made visible in a new register called **UpperFramesOk**.

**SqeErrors** and **CarrierLost** stick at 0xf, to prevent the host from reading a zero from them as they roll over.

All statistics registers have been redesigned so there is no longer any need to disable statistics collection when registers are read. This prevents statistics events from being lost at 100 Mbps.

# Large Packet Support

PCI/EISA bus master adapters support "large" packets, up to 4,494 bytes each, including the Frame Check Sequence (FCS). To accommodate this, all threshold registers have been increased to 13 bits wide. Since commands still only have an 11-bit parameter, all threshold-setting commands write the 11-bit parameter into the upper 11 bits of the threshold registers; the lower two bits are always zero. This has the side effect of scaling all threshold values by a factor of four when PIO code is running on PCI/EISA bus master adapters.

Receive frames are truncated at 1,792 bytes or 6 KB, depending upon the value of *allowLargePackets* in **MacControl**. Errors of the type *oversizedFrame* are flagged at either greater than 1,514 bytes or greater than 4,494 bytes, depending upon the value of *allowLargePackets*.

The **RxStatus** register functionality has been split into two registers, **RxStatus** and **RxError**. The error codes from PIO have been replaced with a bit-per-error condition.

Large packet support affects bit-field widths in the following registers: **RxStatus**, **MasterStatus**, **TxStartThresh**, **TxAvailableThresh**, and **RxEarlyThresh**.

# **Media-Related Functions**

Several functions have been added to support the 100 Mbps data rate and extended deference modes.

The MacControl register contains bits to allow setting of transmit deference options.

The **PhysicalMgmt** register allows control over the Management Interface portion of the Media Independent Interface.

# **Station Address Masking Function**

The **StationMask** register provides the ability to treat individual bits in **StationAddress** as unimportant when address comparisons on receive frames are performed.

#### **New Registers**

New registers added to PCI/EISA bus master adapters versus those supported on PIO adapters are as follows:

StationMask, PhysicalMgmt, MacControl, MasterLen, MasterAddress, MasterStatus, OtherInt, ResetOptions, RxError, UpperFramesOk, BadSSD

#### **Commands Not Supported**

This generation of adapters does not support the power management commands implemented on PIO adapters.

#### **New Interrupt Bit**

The transferInt bit has been added to IntStatus to support transfer complete interrupts.

#### **Miscellaneous Details**

Full duplex operation is enabled by setting *fullDuplexEnable* in **MacControl**, instead of *externalLoopback* in **NetworkDiagnostic**.

The *busMasterInProgress* bit has been added to **IntStatus**. The *otherInt* and *transferInt* bits in **IntStatus** are swapped relative to PIO adapters.

# **Differences Between PCI and EISA Bus Master Adapters**

**ProductId**, **AddressConfig**, **ConfigControl**, **EthernetControllerStatus**, and **ResourceConfig** are not supported by PCI adapters. Most of the functions in these registers have been moved to PCI configuration registers. PCI adapters are configured with special registers in the PCI configuration space.

EISA bus master adapters still support **ProductId**, **AddressConfig**, **ConfigControl**, and **ResourceConfig**.

EISA adapters are configured using the registers in Windows 0, which are mapped into the EISA slot-specific I/O space. Refer to Chapter 5 for more detail.

For both EISA and PCI adapters, the Power-on Reset bits (POR) have been moved into the new register **ResetOptions** at Window 3, offset 8. The transceiver select bits, *autoSelect* and *romSize*, have been moved to **InternalConfig**.

# **PIO/Bus Master Nomenclature**

This manual introduces new naming conventions to make names more meaningful. The following table lists the resulting inconsistencies between the PCI/EISA bus master documents and the PIO adapter documents.

| Bus Master Adapter Name    | PIO Adapter Name                             | Туре                  |

|----------------------------|----------------------------------------------|-----------------------|

| InterruptEnable            | InterruptMask                                | Register              |

| IndicationEnable           | ReadZeroMask                                 | Register              |

| RxData                     | RxPioDataRead                                | Register              |

| TxData                     | TxPioDataWrite                               | Register              |

| Frame start header         | Transmit preamble                            | Data structure        |

| hostError                  | adapterFailure                               | IntStatus bit         |

| interruptRequested         | interruptOnSuccess ful TransmissionRequested | TxStatus bit          |

| txFatalError               | txResetRequired                              | NetworkDiagnostic bit |

| forcedConfig               | TST                                          | EepromCommand bit     |

| eepromBusy                 | EBY                                          | EepromCommand bit     |

| eepromAddress/eepromOpcode | EEPROM COMMAND                               | EepromCommand field   |

Refer to the section "Typographic Conventions" on page 1-3 for an explanation of the meaning of the typefaces used here.

# Chapter 3 Adapter Operation

This chapter contains the following PCI/EISA bus master adapter topics:

- Basic operational concepts

- Configuration and initialization

- Frame transmission

- Frame reception

- Interrupts and indications

- Statistics

PCI and EISA bus master adapters share many of the same characteristics. In this manual, differences are clearly indicated as PCI or EISA. If there is no such indication, the information is valid for either type of adapter.

# **Basic Operational Concepts**

This section contains information about the following basic concepts:

- Register windows

- Bit-widths of register accesses

- Command register

- Command summary

- IntStatus register

- Optimized adapter operation

- Timer register

- Data transfer modes

- Support for multiple signaling standards

- BIOS ROM

# **Register Windows**

The host interacts with the adapter mostly through I/O mapped registers. The I/O registers are grouped into eight 16-byte "windows."

The adapter occupies 32 bytes in the host computer's I/O space. The first 16 bytes look essentially like the first-generation PIO adapter programming model. At any given time, one of eight possible register windows is visible in this space.

The upper 16 bytes are a fixed window into the Window 1 registers. This fixed window is provided as an aid to writing drivers to operate in multiprocessor environments. When the driver code is split among multiple processors, the critical-path data transfer code always has access to the key data transfer registers.

A register's location is specified by its window number and its offset within the window. For instance, information about transmit frames is available in the **TxStatus** register at Window 1, offset b and Window 7. Some registers appear in more than one window.

In general, registers are grouped together in a window because they are used together to perform a major adapter function. For instance, Window 0 registers are used for adapter configuration, and Window 1 registers are used for PIO data transfer.

The window currently visible in the first 16 bytes of I/O space is changed by issuing a command to the adapter. Commands are described in the section "Command Summary" on page 3-3.

# **Bit-Widths of Register Accesses**

In general, I/O registers must be accessed with instructions that are no larger than the bit-width of that register. For instance, even though the **BytesRcvdOk**, **UpperFramesOk**, and **FramesDeferred** registers all appear in the double word at offset 8 in Window 6, it is not legal to read all three registers with a single 32-bit I/O read instruction.

Additionally, **StationAddress** and **StationMask** must be accessed with no larger than wordwide (16-bit) cycles because of internal architecture limitations.

Some registers cannot be accessed with cycles narrower than the register. These restrictions are detailed in the individual register definitions.

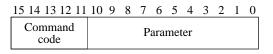

# **Command Register**

Many of the driver's interactions with the adapter are performed using a command structure. Commands are codes, sometimes including a parameter, written to the adapter to perform some action. For instance, the RxEnable command causes the adapter to start accepting receive frames from the medium.

Commands are written to the **Command** register. The write-only **Command** register is unusual in that it appears in every window. It resides at offset e.

# **Command Summary**

The commands are listed here for reference. Refer to the **Command** register definition in Chapter 4, "Register Listings," for complete definitions of these commands.

| piece deminitions of these commands.                                  |

|-----------------------------------------------------------------------|

| Perform an overall reset of adapter                                   |

| Change the visible window                                             |

| Enable the 10BASE2 DC-DC converter (10 Mbps only)                     |

| Disable frame reception                                               |

| Enable frame reception                                                |

| Reset the receive logic                                               |

| Signal that a transmit frame has been downloaded to the transmit FIFO |

| Discard the top receive frame from the adapter                        |

| Enable frame transmission                                             |

| Disable frame transmission                                            |

| Reset the transmit logic                                              |

| Cause the adapter to generate an interrupt                            |

| Acknowledge active interrupts                                         |

| Set the value of the InterruptEnable register                         |

| Set the value of the IndicationEnable register                        |

| Set the value of the <b>RxFilter</b> register                         |

| Set the value of the <b>RxEarlyThresh</b> register                    |

| Set the value of the <b>TxAvailableThresh</b> register                |

| Set the value of the <b>TxStartThresh</b> register                    |

| Start a bus master data transfer operation                            |

| Enable collection of statistics                                       |

| Disable statistics collection                                         |

| Disable the 10BASE2 DC-DC converter (10 Mbps only)                    |

|                                                                       |

# **IntStatus Register**

The read-only **IntStatus** register occupies the same location as the **Command** register: offset e in every window.

**IntStatus** is used by a driver to determine the sources of interrupts on the adapter, and to determine which window is currently visible. **IntStatus** also includes a bit to indicate when a command issued to the **Command** register is in the process of being executed.

# **Optimized Adapter Operations**

This specification describes several mechanisms by which adapter operations are optimized. An optimization mechanism involves generating an interrupt or starting a process before it would normally occur, to gain some benefit from parallel operation.

Optimization mechanisms involve the use of a threshold register, whose value specifies when the early interrupt or process start should occur. For instance, the **TxStartThresh** register specifies how many bytes of a frame must be downloaded to the adapter before the frame can begin transmission.

# **Timer Register**

The **Timer** register performs interrupt latency measurements to support some of the optimization mechanisms on the adapter. The timer is started when the adapter asserts an interrupt on the bus. Refer to the **Timer** register definition in Chapter 4, "Register Listings," for complete details.

# **Data Transfer Modes**

Two frame-data transfer modes are supported by PCI/EISA adapters. A driver can use any convenient combination of the transfer modes to perform frame data transfers. The data transfer modes (programmed I/O and bus master) are described briefly in the following paragraphs.

#### Programmed I/O

Programmed I/O (PIO) is the "base" data transfer mode, supported by all PIO and bus master adapters. Under PIO, a 32-bit wide register in Window 1 is used as a write-only port for transmit data, and as a read-only port for receive data.

PIO data transfers can be of byte, word, or double-word width, and can be at any byte alignment. Prior to performing PIO reads, a driver must first check that there is valid data in the receive FIFO by reading **RxStatus**. Before performing PIO writes, a driver must verify that space exists in the transmit FIFO by reading **TxFree**.

Refer to the sections "Frame Transmission" on page 3-10 and "Frame Reception" on page 3-14 for more details about PIO data transfers.

#### **Bus Master**

PCI/EISA adapters support fragment-based bus master transfers. This feature allows burst data transfer at four bytes for every system clock, yielding a maximum raw data transfer rate of over 100 MBps. Actual aggregate data transfer rates will be lower because of on-board RAM contention and contention with other system masters.

Fragment bus master data transfers are controlled using registers located in Window 7. The length and starting address for a data fragment transfer are programmed into **MasterLen** and **MasterAddress**, respectively. A command is then issued to the adapter to cause it to initiate the bus master transfer. Bus master transfers can be of any length and begin on any byte boundary.

Status information for bus master transfers can be read from the MasterStatus register.

When a fragment bus master transfer is complete, the adapter sets the appropriate completion bit in **MasterStatus**. The adapter can also be programmed to generate an interrupt upon completion of a bus master operation.

It is expected that bus master transfers will be intermixed with PIO transfers to move packets in the most efficient way. Small fragments will probably be more efficiently moved with PIO because of the overhead involved in setting up a bus master transfer. Host software should measure the overhead to initiate a bus master transfer at initialization time to determine the break-even point between PIO and bus master transfers.

Refer to the sections "Frame Transmission" on page 3-10 and "Frame Reception" on page 3-14 for more details about fragment bus master data transfers.

### **BIOS ROM**

Like other PIO and bus master adapters, Fast EtherLink bus master PCI/EISA adapters support an optional BIOS ROM. A variety of PROMs, EEPROMs, and flash ROMs are supported. The EISA adapter BIOS ROM interface is similar to the one found in previous PIO adapters. The PCI specification requires a few differences in the ROM interface compared to that of PIO adapters.

First, the BIOS ROM is configured through the **BiosRomControl** PCI configuration register. The physical size of the ROM can still be programmed into the EEPROM at the time of manufacture and read from there by a driver, but the PCI system power-on self-test (POST) will not be aware of the ROM's physical size.

Second, PCI requires that ROMs be accessible using byte, word, or double-word cycles. Therefore, a host read of the adapter's BIOS ROM receives wait-states while four byte-wide ROM accesses occur on the adapter. All write accesses to the ROM (with a flash or EEPROM device installed) must be made via double-word writes to the adapter. Configuration and Initialization

# **Configuration and Initialization**

This section contains information about the following topics that affect configuration and initialization:

- System reset

- Forced configuration

- Global reset

- PCI adapter configuration

- EISA adapter configuration

- Adapter initialization

# System Reset

System reset is the assertion of the hardware reset signal on the PCI or EISA bus. System reset causes a complete reset of the adapter, including forcing flip-flops to known values, and loss of any adapter configuration that has been set.

# **Forced Configuration**

Under some circumstances, it is necessary to force a usable configuration into the adapter ASIC without its being able to read the EEPROM. Examples of this are the ASIC IC production test and board-level production test.

The EEPROM data-in pin is sampled on the trailing edge of the system reset pulse. If it is low, the adapter is forced into the following configuration:

- PCI–I/O base address 0x200, I/O target cycles and bus master cycles enabled, memory target cycles disabled, and BIOS ROM disabled.

- EISA–I/O base address z000 (z equals the EISA slot number), card enable on, and BIOS ROM disabled.

### **Global Reset**

A GlobalReset command is available for use by the driver software in resetting the adapter. The GlobalReset command has a bit mask parameter that allows selective reset of various parts of the adapter. Refer to the **Command** register definition in Chapter 4 for details.

# PCI Adapter Configuration

Adapter configuration consists of allocating system resources to the adapter and setting adapterspecific options. This is done by writing values into special PCI configuration and I/O registers. The location of this configuration space in the host processor's address map is system-dependent. Configuration is performed by a POST routine supplied with the computer system.

The registers that are set during configuration are described in the following paragraphs.

| PciCommand     | Enables adapter operation by allowing it to respond to and generate PCI bus cycles. This register also allows enabling of parity error generation.                                                                                                                                                               |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IoBaseAddress  | Sets the I/O base address for the adapter.                                                                                                                                                                                                                                                                       |

| BiosRomControl | Sets the base address and size for an installed expansion ROM, if any.                                                                                                                                                                                                                                           |

| LatencyTimer   | Programs an adapter timer that controls how long the adapter can hold<br>the bus as a bus master.                                                                                                                                                                                                                |

| InterruptLine  | Maps the adapter's interrupt request to a specific interrupt line (level) on the system board.                                                                                                                                                                                                                   |

| InternalConfig | Selects the media port (transceiver) and local RAM parameters.<br>InternalConfig will probably not be written by the system<br>configuration utility, but it will be mapped in the PCI configuration<br>space for possible future use. InternalConfig is also mapped into<br>Window 3 of the I/O register space. |

Refer to Chapter 5, "Adapter Configuration," for complete details of the configuration registers.

# **EISA Adapter Configuration**

EISA systems dedicate 1 KB of I/O space to each card slot. EISA adapters are configured using a group of configuration registers, which are mapped to certain locations within this 1 KB slot-specific space. Under the EISA configuration scheme, after system reset the system checks each slot for a unique adapter ID code and matches the codes with data stored in the system's nonvolatile RAM. The system uses that data to program the various EISA configuration registers on the adapter. The basic configuration consists of such parameters as interrupt level and BIOS ROM base address.

See Chapter 5, "Adapter Configuration," for more information on EISA configuration.

# Adapter Initialization

After the system has performed basic configuration of the adapter, software needs to initialize the adapter, which means setting the adapter registers to the desired initial values.

Configuration and Initialization

#### Serial EEPROM

The serial EEPROM is used for nonvolatile storage of such information as the device ID, node address, manufacturing data, default configuration settings, and software information. Some of the EEPROM data is automatically read into the adapter logic after system reset (for example, device ID and configuration defaults), whereas other data (for example, node address and software information) is meant to be read by driver software.

Shortly after system reset, EEPROM control logic reads certain locations from the EEPROM, placing the data into the following host-accessible registers:

| PCI EEPROM Location | Register            | Space                  |

|---------------------|---------------------|------------------------|

| 3                   | DeviceId            | PCI configuration      |

| 12                  | InternalConfig Low  | I/O, PCI configuration |

| 13                  | InternalConfig High | I/O, PCI configuration |

| EISA EEPROM Location | Register            | Space                   |

|----------------------|---------------------|-------------------------|

| 8                    | AddressConfig       | EISA configuration      |

| 9                    | ResourceConfig      | EISA configuration      |

| 3                    | ProductId           | EISA configuration      |

| 12                   | InternalConfig Low  | I/O, EISA configuration |

| 13                   | InternalConfig High | I/O, EISA configuration |

#### **Selecting the Media Port**

The media port (transceiver) to be used is selected through the *xcvrSelect* field in the **InternalConfig** register. On PCI adapters, **InternalConfig** is mapped into both the PCI configuration and I/O register spaces but will in most cases be written in the I/O space.

Because the value of **InternalConfig** is also stored in the serial EEPROM, it is possible to set the media port once, write the value into EEPROM, and then have the adapter automatically use the stored value when it is powered up.

Alternatively, there is a mechanism for having the driver ignore the stored value for *xcvrSelect* and attempt to set the media port based on which one is currently active. This is called auto select. When the *autoSelect* bit in **InternalConfig** is set, the driver selects each port available on the adapter (see **ResetOptions** later in this chapter) in turn, and attempts to determine which port is connected to the network. If the driver fails to find a connected port, it restores the original value in *xcvrSelect*.

The recommended sequence for determining the active port is as follows (a driver skips the steps corresponding to those media types that are not installed on the adapter):

- 100BASE-TX *linkBeatDetect* in the **MediaStatus** register indicates an active port.

- 100BASE-FX *linkBeatDetect* in the **MediaStatus** register indicates an active port.

- MII the indication of an active port depends upon the type of transceiver that is connected to the MII. Typically, the management interface provided by the **PhysicalMgmt** register is used to check for a device connected to the MII.

- 10BASE-T *linkBeatDetect* in the **MediaStatus** register indicates an active port.

- 10Mbps AUI (10BASE5) The driver performs an external loopback to check for an active port. Refer to the section "Network Diagnostic" on page 4-34 for more information on loopback modes.

- 10BASE2 The driver performs an external loopback to check for an active port. Refer to the section "Network Diagnostic" on page 4-34 for more information on loopback modes.

#### **ResetOptions**

The **ResetOptions** register provides a way for driver or configuration software to determine the hardware media options installed on the adapter, and the media operational mode (normal or test).

**ResetOptions** attains its value upon hardware (system) reset, when certain ASIC pins are sampled and latched.

#### **Setting the RAM Partition**

The **InternalConfig** register also contains several fields related to the local packet buffer RAM. Three of the fields (*ramSize*, *ramWidth*, and *ramSpeed*) are fixed for a particular adapter, and are not writable by host software. The *ramPartition* field, however, is set by driver or configuration software to tune the adapter to the particular system environment.

The value of *ramPartition* determines how the local packet buffer RAM is divided between receive and transmit functions. It is expressed in terms of a ratio of receive space to transmit space. For instance, an adapter with 64 KB of local RAM with a *ramPartition* setting of 3:1 would have 48 KB of receive space and 16 KB of transmit space.

Refer to the InternalConfig register definition for more details on the RAM parameter fields.

#### **Station Address**

The driver is expected to program the adapter's network address into the **StationAddress** register. The adapter's network address can be obtained from the appropriate data locations within the EEPROM. The host is, of course, free to program any arbitrary value into **StationAddress**.

#### **Broadcast Address**

To have the adapter respond to broadcast frames, frames with a broadcast address (that is, ff:ff:ff:ff:ff:ff) can be received by setting the *receiveBroadcast* bit in **RxFilter**.

#### **Multicast Addresses**

The adapters include no support for multicast comparisons. The Fast EtherLink bus master adapters can be configured to accept all multicast frames by setting the *receiveMulticast* bit in **RxFilter**. Any further filtering must be accomplished in software.

#### **Capabilities Word**

The Capabilities Word is a 16-bit location in the EEPROM that specifies the capabilities of the adapter. Refer to the section "EEPROM Data Format" on page 5-8 for more details.

# **Frame Transmission**

This section contains an overview of the frame transmission process.

## **Frame Transmission Model**

The frame transmission mechanism is modeled as a logical FIFO. Data to be transmitted is transferred into the FIFO by the system interface and is removed from the FIFO by the network interface.

Within the FIFO, frames are delimited by a 32-bit frame start header (FSH), which includes the length of the frame that follows. The frame data consists of the destination address field through the info field. The adapter normally generates a CRC and inserts it into the frame check sequence (FCS) field automatically, although it is an option to disable this and supply the FCS along with the frame data.

Transmit data is moved into the FIFO using programmed I/O or bus master transfers. The methods used to download the data are transparent to the FIFO.

Frame transmission involves downloading (writing) the FSH and the transmit frame to the FIFO, issuing a TxDone command to inform the adapter that the frame is complete, and possibly responding to a transmit complete indication.

### **Transmit Data Writes**

The transmit FSH and frame data is written to the transmit FIFO using combinations of two data transfer modes: programmed I/O and bus master.

#### **Programmed I/O**

The first method is through I/O writes to the **TxData** register. This register is a special-purpose window into the transmit FIFO.

The data can be written to **TxData** as bytes, words, or double-words and can be aligned to any byte lane.

Prior to writing transmit frame data to the adapter, the host must verify that sufficient space remains in the transmit FIFO. This is determined by reading **TxFree**. The value returned by **TxFree** indicates the number of bytes of free space within the transmit FIFO.

If the driver determines that the free space is smaller than the frame to be transmitted, then the driver should issue the SetTxAvailableThresh command and await an interrupt. Upon responding to the *txAvailable* interrupt, sufficient room within the transmit FIFO is ensured.

#### **Bus Master**

In this second method, the host places data to be transmitted in a contiguous block of system memory. The starting address of the fragment buffer is written to the **MasterAddress** register, and the byte length of the buffer is written to **MasterLen** (the start address may have any byte alignment). The adapter's StartDma command is then issued to cause the adapter to perform the bus master transfer.

Unlike PIO, the adapter paces the data transfers so that no transmit FIFO overrun occurs during bus master transfers. It is not necessary to check the value of **TxFree** before a bus master download operation is started.

When the bus master transfer is complete, the adapter sets the *masterDownload* bit in the **MasterStatus** register. The adapter can also be programmed to generate an interrupt upon completion of a bus master download operation.

While a bus master download operation is in progress, it is an error to write to the **TxData** register, since this would insert data at unpredictable places in the transmit frame. The value in **TxFree** is also unreliable during bus master download operations.

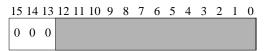

#### **Frame Start Header**

The first 32 bits of data transferred to the transmit FIFO are interpreted to be a frame start header. The frame start header contains frame length and control information for the frame.

The format of the frame start header is as follows:

```

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0<

```

| txIndicate       | [15]: This bit is set if the driver desires a <i>txComplete</i> indication upon completion of transmission of this frame. If this bit is cleared, no indication of transmit completion is given by the adapter.                                                                                                                                      |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| reserved         | [14]: This bit is reserved. A zero should be written here.                                                                                                                                                                                                                                                                                           |

| crcAppendDisable | [13]: The driver sets this bit to inhibit the adapter from appending a CRC to the end of this frame. When <i>crcAppendDisable</i> is set, it is expected that the frame's CRC will be supplied as part of the data downloaded to the FIFO. An exception to this is a transmit underrun, in which case a guaranteed-bad CRC is appended to the frame. |

|                  | When this bit is cleared, the adapter computes and appends CRCs for transmit frames.                                                                                                                                                                                                                                                                 |

|                  | An adapter indicates its support of <i>crcAppendDisable</i> through the Capabilities Word.                                                                                                                                                                                                                                                           |

| txLength         | [12:0]: This field contains the length of the frame to follow. When the driver writes data to the FIFO, it must pad the data to the next dword boundary (or use the TxDone command). The value in <i>txLength</i> must match the number of actual frame bytes and must not include any pad bytes.                                                    |

## **Completing a Transmit Frame Download**

The downloading of a transmit frame can be "completed" in one of two ways. In either case, the goal in completing a frame is to ensure that the frame is properly delimited and readied for transmission in the transmit FIFO.

The two ways to complete a frame download are:

- Padding to a double-word boundary

- Issuing a TxDone command

The need to properly complete a transmit frame applies equally whether the frame is being moved with PIO, bus mastering, or a combination of the two methods.

#### Padding to a Dword Boundary

To pad to a dword boundary, the driver must write sufficient bytes after the last data bytes of the packet to make the total number of bytes written for the packet be an even multiple of four.

For example, if a 61-byte packet is to be transmitted, and the FSH and 61 bytes of data have been downloaded, then three more bytes must be written, either as three-byte writes or a word write plus a byte write.<sup>1</sup> With bus mastering, this can also be accomplished by padding out the length of the final fragment transfer to include the extra bytes. Note that these pad bytes are important in getting the packet into the transmit FIFO and hence available for transmission. The transmit packet could underrun after all data bytes have been written if too much time elapses before the pad bytes are written.

#### Issuing a TxDone Command

The TxDone command is used when it is inefficient for the driver to pad the final write to the transmit FIFO. This might occur when the driver is using a bus master transfer to move the last fragment of a frame, and it is desired to write the fragment length as specified from upper layers of software directly into the **MasterLen** register.

When TxDone is used, the total number of frame bytes written to the FIFO must exactly match the frame length specified in the frame start header. After the last write operation to the FIFO, the driver issues TxDone to inform the adapter logic that the frame is complete.

### Padding to Minimum Frame Length

The adapter automatically appends the appropriate number of arbitrary data bytes to the end of the frame's data field to pad the frame to 60 bytes in length. The frame length value written as part of the frame start header does not reflect the padded frame length, but rather the number of bytes supplied by the driver to the adapter.

### **Initiating Frame Transmission**

The adapter initiates frame transmission as soon as either the entire frame is resident on the adapter or the number of bytes that are resident is greater than the value in **TxStartThresh**.

<sup>1.</sup> This example does not represent a particularly efficient way to move this 61-byte packet into the FIFO. A more efficient method would be to move the FSH and packet data in 17 dword write instructions: one dword for the FSH and 16 dwords for the packet data plus pad bytes.

# **Transmission Completion**

As soon as the adapter has completed its attempt(s) to transmit a frame, it can post the frame's transmit status. Status is not posted unless either an error occurred during frame transmission or the *txIndicate* bit in the frame start header was set.

Assuming that *txIndicate* for the frame is set and the interrupt and indication masks are appropriately configured, then the adapter generates an interrupt on the host's bus.

The host's initial reaction to an interrupt should be to read the **IntStatus** register to determine the cause of the interrupt. The *txComplete* bit in **IntStatus** is set.

Once the device driver has determined that the adapter has completed its attempt to transmit a frame, it may examine **TxStatus** to determine the outcome of the transmission.

# **Updating the Status**

When the device driver has checked the outcome of a transmission in **TxStatus**, writing an arbitrary value to **TxStatus** causes **TxStatus** to advance to the results of the next transmit frame, if one exists.

# **Multiple Transmit Completions**

If more than one frame has pending transmit status, txComplete remains set after the write to **TxStatus**, until the status of all completed transmissions has been read. If there are no more frames that have completed transmission, then txComplete is cleared and the other bits in **TxStatus** are undefined.

After servicing a *txComplete* interrupt and writing to **TxStatus**, the driver should test to see whether *txComplete* remains asserted. If *txComplete* is not asserted, then the driver should return from the interrupt service routine. If, however, *txComplete* is set, then the driver should read the **TxStatus** register for the status of the next completed transmission.

# **Frame Transmission Errors**

Although **TxStatus** is only of interest to the driver when *txComplete* indications are required, an exception to this is created when transmission errors occur. In this situation, a *txComplete* indication is always issued and transmit processes are stopped. When the host responds to the indication, it checks **TxStatus** for the cause of the error. Status for previous, successful transmit frames (that had the *txIndicate* bit set) may need to be read first to bring the error frame's status to the top of the **TxStatus** queue.

When a transmission error occurs, the driver must reenable the transmitter before subsequent transmissions can proceed. Some transmission errors may require the driver to reset the transmit logic to recover from the error.

# **Optimized Transmit Operations**

#### **Early Transmission Start**

The adapter can be enabled to begin transmission of a frame onto the network media prior to the transfer of the entire frame into the adapter's transmit FIFO. This is accomplished via **TxStartThresh**.

**TxStartThresh** specifies the number of bytes of the transmit frame that must reside on the adapter before it can commence with the transmission of the frame. The start of transmission may be delayed by other queued transmissions or by delays in gaining media access.

If this register is set to a value that is greater than the maximum allowed frame length, then the early transmit feature is disabled and the entire transmit frame must reside on the adapter before the adapter will begin to transmit it.

The value for this register must be carefully chosen to optimize performance. If set too low, system latencies or bandwidth limitations may cause the adapter to underrun the network during transmission, causing a partial (bad) frame to be transmitted. (The frame will have a bad CRC appended, guaranteeing its rejection by receiving stations.) If set too high, unnecessary delays are incurred before the start of transmission.

The adapter generates an indication of an underrun via the *txUnderrun* bit in **TxStatus**. A driver responds to a *txUnderrun* error by first waiting for any transmission in progress to finish by polling on the *txInProg* bit in **MediaStatus**. Next, the driver should reset the transmit process, including any active bus master download, using TxReset. The frame that experienced the underrun can then be resubmitted to the adapter for transmission.

When a *txUnderrun* indication does occur, the driver should increase the value in **TxStartThresh**. Further *txUnderrun* indications should cause the driver to continue to increase **TxStartThresh**. If **TxStartThresh** is eventually greater than the maximum allowable frame length, then the early transmit start feature is disabled.

# **Frame Reception**

This section contains an overview of the frame reception process.

### **Frame Reception Model**

The frame reception mechanism is modeled as a logical FIFO. Data to be received is transferred into the FIFO by the network interface, and removed from the FIFO by the system interface.

The frame data placed in the FIFO consists of the Destination Address field through the information field. The adapter normally strips the FCS automatically, although it is an option to disable this feature, causing the adapter to supply the FCS along with the frame data.

Receive data is moved out of the FIFO using PIO or bus master transfers. The methods used to upload the data are transparent to the FIFO.

The adapter receives all frames that meet the filtering criteria established by bits in **RxFilter** and by the address stored in **StationAddress**.

#### **Top Frame**

The concept of the "top receive frame" must be understood before any explanation of receive operations. The top frame is the oldest frame in the receive FIFO, and hence the frame for which status is available in **RxStatus**. The top frame can be either a frame that is currently being received off the network media or one that has already been completely received.

## **Normal Frame Reception**

In the nonoptimized condition, the driver is alerted to the presence of a receive frame by an interrupt on the host's bus. The *rxComplete* bit in **IntStatus** indicates to the driver that an entire frame has been received and is available in the receive FIFO. The received frame is available for examination upon receipt of the *rxComplete* interrupt.

### **Receive Data Reads**

The receive frame data is removed from the receive FIFO using combinations of two data transfer modes available on the adapter: programmed I/O and bus master.

#### **Programmed I/O**

The first method is through I/O reads of the **RxData** register. **RxData** is a 32-bit window into the adapter's receive FIFO. Sequential reads of bytes, words, and double words are allowed on any combination of contiguous byte lanes.

Prior to reading data from **RxData**, a driver must determine that there are bytes available to be read in the receive FIFO. This is done by checking the *rxBytes* field in the **RxStatus** register.

In general, it is illegal to read bytes from **RxData** beyond the last byte of the top frame. An important exception is to read extra bytes (up to three) within the last double word of the frame. This allows an entire frame to be read with 32-bit I/O cycles.

#### **Bus Master**

In this second method, the host writes the address of a fragment buffer into the **MasterAddress** register, and the byte length of the buffer into the **MasterLen** register (the start address may have any byte alignment). The adapter's StartDma command is then issued to cause the adapter to perform the bus master transfer.

Unlike PIO, the adapter paces the data transfers such that no receive FIFO underrun occurs during bus master uploads. It is not necessary to check the value of *rxBytes* before a bus master download operation is started.

When the bus master transfer has been completed, the adapter sets the *masterUpload* bit in the **MasterStatus** register. The adapter can also be programmed to generate an interrupt upon completion of a bus master upload operation.

While a bus master upload operation is in progress, it is an error to read from the **RxData** register, as this would remove data from the uploaded receive frame at unpredictable places. It is also illegal to issue an RxDiscard command while a bus master operation is in progress. Also, the values in *rxBytes* are unreliable during bus master upload operations.

#### **RxStatus and RxError**

Associated with the top receive frame is information related to the condition of the received frame and the number of bytes of the top frame that remain in the receive FIFO. This information is available via **RxStatus** and **RxError**.

**RxStatus** provides status information for receive frames and the number of bytes remaining in the FIFO for receive frames. Receive overruns, framing errors, CRC errors, and the oversized and runt frame conditions are the error conditions reported in **RxError**.

The length value returned by **RxStatus** represents the number of valid data bytes that remain to be transferred from the FIFO. Data bytes beyond the end of the frame are undefined and in some cases are illegal to read.

#### **Discarding the Top Frame**

Issuing the RxDiscard command causes the adapter to make the next receive frame the top frame. Until RxDiscard is issued, the status and data of the subsequent frame are unavailable to the host. Once RxDiscard is issued, the status of the top frame are discarded and cannot be recovered.

#### **Queued Receives**

If the driver is unable to keep up with the adapter's rate of frame reception, receive frames are queued up within the adapter's on-board receive FIFO.

If one or more received frames are queued on the adapter when RxDiscard is issued by the driver, an *rxComplete* indication occurs, informing the driver that the receive FIFO contains a new valid receive frame.

#### **Receive Frame Size Limits**

The adapter truncates any received frame to a length of 1,792 or 6,144 bytes, depending upon the value programmed into the *allowLargePackets* bit in **MacControl**.

Also, depending upon the value in *allowLargePackets*, the adapter generates an *oversizeFrame* error for receive frames greater than 1,518 bytes or 4,494 bytes, including the FCS field.

### **Optimized Frame Reception**

#### **Early Receive Indications**

A method is available for early indications of received frames. This involves setting a threshold relative to the start of a frame.

**RxEarlyThresh** is used to program an indication threshold relative to the start of the incoming frame. The first byte of the destination address is considered to be byte 1.

**RxEarlyThresh** is set using the SetRxEarlyThresh command. The current threshold setting can be read in the **RxEarlyThresh** register.

As soon as the number of bytes that have been received is greater than the value in **RxEarlyThresh**, the adapter generates an interrupt to the host (assuming the *rxEarly* indication and interrupt bits are not masked). The *rxEarly* indication only occurs when the frame being received is the top frame. In other words, the *rxEarly* indication only occurs if the frame being received can be transferred by the host during reception. The **RxEarlyThresh** mechanism causes one *rxEarly* indication per frame unless it is retriggered.

An *rxEarly* indication occurs whenever the **RxEarlyThresh** threshold has been exceeded and the frame being received is the top frame. These two conditions can be met in either order. In other words, it is reasonable to expect that issuing the RxDiscard command may cause an *rxEarly* indication by making a frame that is in the process of being received the top frame.

The driver can program any value into **RxEarlyThresh**, but setting **RxEarlyThresh** to less than 8 causes the adapter to interpret the value as 8, so as to allow the adapter to perform destination address filtering before generating an *rxEarly* indication.

**RxEarlyThresh** also involves the concept of frame "visibility." The value programmed into **RxEarlyThresh** determines how many bytes of a frame must be received before information about the frame is made visible in **RxStatus**. Frames become visible when **min (60, RxEarlyThresh)** bytes are received (that is, frames become visible after 60 bytes or when the number of bytes set in **RxEarlyThresh** has been received).

For bus master transfers, the value in **RxEarlyThresh** also determines how many bytes of a frame must be received before upload transfers for the frame are allowed to begin.

Setting **RxEarlyThresh** to a value that is too low may cause the host to process an excessive number of collision fragments. Setting **RxEarlyThresh** to a value that is too high introduces unnecessary delays in the system's receive response sequence.

If **RxEarlyThresh** is set to a value that is greater than the length of the received frame, then an *rxComplete* interrupt occurs at the completion of frame reception rather than an *rxEarly* interrupt.

If the host system is particularly slow in responding to an *rxEarly* interrupt, then it is entirely likely that the frame will have been completely received by the time the driver examines the adapter. In this case, *rxEarly* is overridden by *rxComplete*. The *rxEarly* and *rxComplete* interrupts are mutually exclusive. Because *rxEarly* "goes away" when *rxComplete* becomes set, *rxComplete* should only be disabled if *rxEarly* is also disabled. This prevents spurious interrupts.

*rxEarly* is meant to be usable as a retriggerable interrupt. In other words, it is legal for the driver to respond to an *rxEarly* interrupt because of a value set in **RxEarlyThresh** and then reprogram **RxEarlyThresh** to a larger value so that a subsequent interrupt is generated within the same receive frame. If a new value is set in **RxEarlyThresh** while a frame is being received from the medium, then an *rxEarly* indication is generated as soon as the *rxEarly* threshold is crossed, or it is generated immediately if the threshold has already been crossed.

#### **Discarding a Frame During Reception**

By issuing the RxDiscard command, the driver can discard a frame while it is being received. A frame discarded in this way does not generate an *rxComplete* interrupt.

## Interrupts and Indications

Interrupts are used to assert a signal to the host that asynchronous activities deserve the host's attention, whereas indications are read from a status register.

## **Interrupts Versus Indications**

There is an important distinction between interrupts and indications. An interrupt results in the assertion of the interrupt signal on the host bus. An indication is merely a bit set in the **IntStatus** register that can be read by the driver. All of the sources of interrupts on the adapter can be used as indications or as indications and interrupts.

## **Determining the Cause of an Interrupt**

When responding to an interrupt, the host reads IntStatus to determine the cause of the interrupt.

#### **IntStatus**

Seven bits in this register define the source of the interrupt. The least significant bit of **IntStatus**, *interruptLatch*, is always set whenever any of the interrupts are asserted. This prevents spurious interrupts on the host bus. The *interruptLatch* interrupt must be explicitly acknowledged using the AcknowledgeInterrupt command.

### Interrupt Acknowledgment

The host acknowledges interrupts by carrying out interrupt-specific actions. These actions are as follows:

| interruptLatch | acknowledged by AcknowledgeInterrupt command                  |

|----------------|---------------------------------------------------------------|

| txComplete     | acknowledged by writing to <b>TxStatus</b>                    |

| rxComplete     | acknowledged by RxDiscard command                             |

| rxEarly        | acknowledged by AcknowledgeInterrupt command                  |

| intRequested   | acknowledged by AcknowledgeInterrupt command                  |

| hostError      | acknowledged by issuing the appropriate resets                |

| updateStats    | acknowledged by reading one or more statistics registers      |

| txAvailable    | acknowledged by AcknowledgeInterrupt command                  |

| otherInt       | acknowledged by clearing interrupt sources in <b>OtherInt</b> |

| transferInt    | acknowledged by clearing interrupt sources in MasterStatus    |

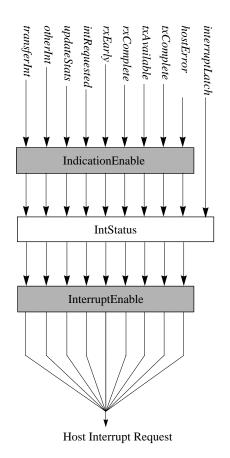

## **Interrupt and Indication Enable Mechanisms**

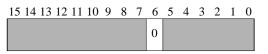

Figure 3-1 illustrates the relationship between interrupts, indications, and their respective enable mechanisms.

#### Figure 3-1. Interrupt and Indication Enable Mechanisms

An interrupt is an asynchronous indication that an event has taken place on the adapter that requires the attention of the host system. The host, however, may not respond quickly, or may not respond at all to certain events. The architecture provides a flexible scheme for allowing each type of event to be assigned the level of urgency sought by the host.

The shaded boxes in the figure above represent enable mechanisms. The white box is the **IntStatus** register, which the host uses to view the various indication bits.

Enable mechanisms have an immediate effect on indications and interrupts. In other words, if a particular interrupt is pending and the host clears its enable bit in **IndicationEnable**, the indication, though still pending, would appear as a zero in **IntStatus** and would no longer contribute to the assertion of the interrupt line on the host bus. Conversely, if the pending indication were to be enabled (by setting its enable bit), the indication would become set in the appropriate registers, and the interrupt signal on the host bus would be asserted by the adapter.

Masking prevents an interrupt or indication from acknowledging the interrupting event.

Before exiting the interrupt service routine, the host should recheck the **IntStatus** register to determine whether any further asynchronous events have occurred.

Statistics

## **Statistics**

The architecture includes specifications for 12 statistics counters of various widths. The gathering of statistics is enabled by issuing the StatisticsEnable command. When enabled, the statistics counters advance as the corresponding events occur. No host intervention is required to facilitate this counting.

Reading a statistics register clears it. It is not necessary to disable statistics collection while reading the statistics registers. It is legal to do so, but disabling statistics collection may result in missed statistical events.

Whenever any of the statistics registers reaches the half-way point of its count, it generates an *updateStatistics* interrupt. Reading a statistics register clears it.

Writing a value to a statistics register adds that value to the register. This is useful in diagnostics and IC production tests.

Reading all of the statistics will acknowledge the updateStatistics interrupt.

| FramesXmittedOk       | The number of frames of all types transmitted without<br>errors. Loss of carrier and absence of an expected SQE<br>are not considered to be errors by this statistic.                                                |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BytesXmittedOk        | A byte total for all frames transmitted without error.                                                                                                                                                               |

| FramesDeferred        | If the transmission of a frame had to defer to network<br>traffic, the event is recorded in this statistic. A single<br>frame may defer more than once as a result of<br>collisions; each deferral would be counted. |

| SingleCollisionFrames | Frames that are transmitted without errors after one and<br>only one collision (including late collisions) are<br>counted by this register.                                                                          |

| MultipleCollisions    | All frames transmitted without error after experiencing<br>from 2 through 15 collisions (including late collisions)<br>are counted here.                                                                             |

| LateCollisions        | Every occurrence of a late collision (there could be<br>more that one per frame transmitted) is counted by this<br>statistic.                                                                                        |

| CarrierLost           | Frames that were transmitted without error but<br>experienced a loss of carrier are counted by this<br>statistic.                                                                                                    |

| SqeErrors             | If the adapter is configured to expect an SQE pulse after<br>each transmission and did not receive such a pulse, the<br>event is counted here.                                                                       |

#### **Transmit Statistics**

| <b>Receive Statistics</b> |                                                                                                                                                                                                                                                 |

|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FramesRcvdOk              | Frames of all types that are received without error are counted here.                                                                                                                                                                           |

| BytesRcvdOk               | A byte total for all frames received without error.<br>A frame's bytes are included in this count if the frame is<br>received without errors and the frame is completely<br>moved into the receive FIFO before RxDiscard is<br>issued.          |

| RxOverruns                | This statistic is a count of <i>rxOverrun</i> errors. Only frames that are actually seen as overruns by the host are included in this count. Frames that are completely ignored by the adapter because of a full receive FIFO are not included. |

| BadSSD                    | A count of frames received with a bad start-of-stream delimiter. This statistic applies only to 100BASE-TX or 100BASE-FX operation.                                                                                                             |

# Chapter 4 Register Listings

## I/O Model

PCI/EISA bus master adapters present and map a set of registers to the host CPU I/O space. Since there are far more registers than is advisable to I/O map directly in DOS systems, the registers are broken into several groups that are made available to the host through 32 bytes worth of I/O space.

The lower 16 bytes of the I/O space look essentially like the PIO redundant model used in previous 3Com adapters. At any given time, one of eight possible register banks (windows) is visible in this space.

The upper 16 bytes are a fixed window into the Window 1 register set.

PCI and EISA bus master adapters share many of the same characteristics. In this manual, differences are clearly indicated as "PCI Only" or "EISA Only." If there is no such indication, the information is valid for either type of adapter.

## 4-2 Register Listings

I/O Model

PCI/EISA bus master adapter register windows are shown below.

| byte 3           | byte 2                                      | byte 1            | byte 0         | Offset   | Window |

|------------------|---------------------------------------------|-------------------|----------------|----------|--------|

| IntStatu         | s/Command                                   | Maste             | с              |          |        |