# EtherLink® III LAN PC Card ERS

Members of the 3Com EtherLink III family of adapters

http://www.3com.com/

Published May 1997

3Com Corporation 5400 Bayfront Plaza Santa Clara, California 95052-8145 Copyright © **3Com Corporation, 1997.** All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without permission from 3Com Corporation.

3Com Corporation reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of 3Com Corporation to provide notification of such revision or change.

3Com Corporation provides this documentation without warranty of any kind, either implied or expressed, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. 3Com may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

#### **UNITED STATES GOVERNMENT LEGENDS:**

If you are a United States government agency, then this documentation and the software described herein are provided to you subject to the following restricted rights:

### For units of the Department of Defense:

Restricted Rights Legend: Use, duplication, or disclosure by the Government is subject to restrictions as set forth in subparagraph (c) (1) (ii) for Restricted Rights in Technical Data and Computer Software Clause at 48 C.F.R. 52.227-7013. 3Com Corporation, 5400 Bayfront Plaza, Santa Clara, California 95052-8145.

### For civilian agencies:

Restricted Rights Legend: Use, reproduction, or disclosure is subject to restrictions set forth in subparagraph (a) through (d) of the Commercial Computer Software – Restricted Rights Clause at 48 C.F.R. 52.227-19 and the limitations set forth in 3Com Corporation's standard commercial agreement for the software. Unpublished rights reserved under the copyright laws of the United States.

If there is any software on removable media described in this documentation, it is furnished under a license agreement included with the product as a separate document, in the hard copy documentation, or on the removable media in a directory file named LICENSE.TXT. If you are unable to locate a copy, please contact 3Com and a copy will be provided to you.

[Portions of this documentation are reproduced in whole or part with permission from (as appropriate).]

Unless otherwise indicated, 3Com registered trademarks are registered in the United States and may or may not be registered in other countries.

3Com, AccessBuilder, Boundary Routing, LANplex, LanScanner, LinkBuilder, NETBuilder, NETBuilder II, Parallel Tasking, ViewBuilder, EtherDisk, EtherLink, EtherLink Plus, EtherLink II, SmartAgent, TokenLink, TokenLink Plus, TokenDisk and Transcend are registered trademarks of 3Com Corporation. 3TECH, CacheCard, FDDILink, FMS, NetProbe and Star-Tek are trademarks of 3Com Corporation. 3ComFacts is a service mark of 3Com Corporation

CompuServe is a registered trademark of CompuServe, Inc. OpenView is a registered trademark of Hewlett-Packard Co. AIX, IBM, and NetView are registered trademarks of International Business Machines Corporation. UNIX is a registered trademark of Novell Inc. OpenWindows, SunNet Manager, and SunOS are trademarks of Sun MicroSystems Inc. SPARCstation is a trademark and is licensed exclusively to Sun Microsystems Inc.

Other brand and product names may be registered trademarks or trademarks of their respective holders.

## **CONTENTS**

1

2

3

4

### **INTRODUCTION** Overview 1-1 3C589D PC Card Differences 1-2 Internal 8K RAM 1-2 Package Reduction 1-2 Added Multifunction Support 1-2 Added PCMCIA Power Down Bit 1-2 Removed PnP 1-2 Register Modified 1-3 Registers Added 1-3 Specification References **ARCHITECTURAL OVERVIEW** Block Diagrams 2-2 Attribute Memory Map 2-3 **DATA STRUCTURES** Receive Packet Structure 3-1 Transmit Packet Structure 3-2 **DESCRIPTION OF OPERATION** Receive 4-1 Receive Packet and RX Status 4-1 Transmit 4-2 Transmit Packet and Transmit Completion Transmitting a Packet 4-3 Disable CRC Generation (3C589B) 4-3 Transmit Underrun 4-4

### 5 WINDOW SET

Window 0 Registers – Setup 5-1

Changes for 3C589D 5-1

Window 1 Registers – Operating Set 5-2

Window 2 Registers – Station Address Setup/Read 5-2

Changes for 3C589D 5-2

Window 3 Registers – FIFO Management 5-3

Changes for 3C589D 5-3

Window 4 Registers – Diagnostic 5-3

Window 5 Registers – Command Results and Internal State 5-4

Window 6 Registers – Statistics 5-5

Added Registers for 3C589D 5-5

### **6** REGISTER DEFINITIONS

Command Register 6-1 Command Register Conventions 6-1 Global Reset\* 6-2 Select Register Window 6-3 Start Coaxial Transceiver 6-3 RX Disable 6-3 RX Enable 6-3 **RX** Reset 6-3 RX Discard Top Packet\* 6-4 6-4 TX Enable TX Disable 6-4 TX Reset\* 6-5 Request Interrupt 6-6 Acknowledge Interrupt Set Interrupt Mask Set Read Zero Mask 6-7 Set RX Filter 6-8 Set RX Early Threshold Set TX Available Threshold Set TX Start Threshold Statistics Enable Statistics Disable 6-9 Stop Coaxial Transceiver 6-10 Power-Management Commands (3C589B) 6-10

```

Status Register

6-11

Bit 0 Interrupt Latch

6-11

Bit 1 Adapter Failure†

6-12

Bit 2 TX Complete†

6-12

6-12

Bit 3 TX Available†

Bit 4 RX Complete†

6-12

Bit 5 RX Early† 6-12

Bit 6 Interrupt Requested†

Bit 7 Update Statistics†

6-12

Bit 12 Command-in-Progress

6-13

Bits 15–13 Window Number

FIFO Registers

6-13

RX Status

6-13

TX Status

6-15

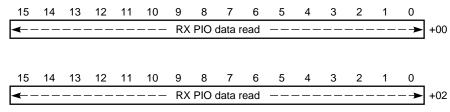

RX PIO Data Read

6-16

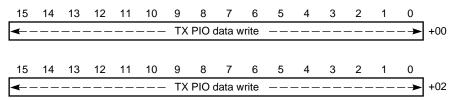

TX PIO Data Write

6-17

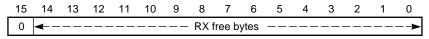

Free Receive Bytes

6-17

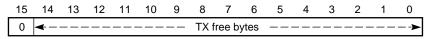

Free Transmit Bytes

6-18

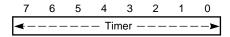

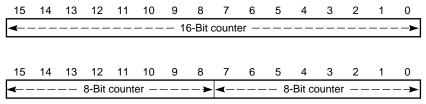

Timer Register

6-18

Statistics Registers

6-19

Statistics

6-19

Diagnostic Registers

6-21

Media Type and Status

6-21

Net Diagnostic Port

FIFO Diagnostic Port 6-23

Ethernet Controller Status

6-25

```

### 7 PC CARD CONFIGURATION AND ENABLE

```

Automatic Configuration at Power-on Reset

PCMCIA Activation Mechanism (3C589 PC Card)

7-1

Configuration Overview (3C589)

PCMCIA Configuration Option Register

Changes for 3C589D

7-3

PCMCIA Card Configuration and Status Register

7-4

Changes for 3C589D

7-4

Changes for 3C589D

7-5

LAN IOBASE 0

7-5

7-5

LAN IOBASE 1

MODEM COR

7-5

MODEM CSR

7-6

MODEM PRR

7-6

7-7

MODEM ESR

MODEM IOBASE 0

7-7

7-7

MODEM IOBASE 1

MODEM IOLIMIT

7-7

Multi-function Configuration Register

7-8

Changes for 3C589D

7-9

```

```

Attribute and Common Memory Access

WRITE MEMORY

7-9

READ MEMORY

7-9

I/O CYCLES

Implementation Notes 7-10

Window 0 Configuration Registers

7-11

Manufacturer ID Register (Read Only - Offset 0)

Product ID Register (3C589) (Read Only - Offset 2) 7-11

Configuration Control Register (3C589) (Read/Write - Offset 4)

7-12

Changes for 3C589D

7-12

Address Configuration Register (3C589) (Read/Write - Offset 6)

7-12

Changes for 3C589D

7-14

Changes for 3C589D

7-14

Resource Configuration Register (3C589, 3C589B) (Read/Write - Offset 8)

Changes for 3C589D

7-14

EEPROM Command Register

(Read/Write - Offset A)

Changes for 3C589D

7-15

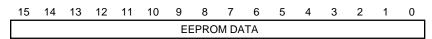

EEPROM Data Register (Read/Write - Offset C) 7-16

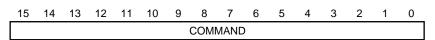

Command Register (Read/Write - Offset E)

Window 3 Configuration Registers

Changes for 3C589D

7-18

EEPROM Data Structure

7-18

EEPROM Data Structure, Offset ODh (Software Information)

7-19

EEPROM Data Structure, Offset 0Eh (Compatibility Word)

7-20

EEPROM Data Structure, Offset OFh (Checksum)

EEPROM Data Structure, Offset 10h (Capabilities Word)

EEPROM Data Structure, Offset 14h (Secondary Software Information)

7-21

EEPROM Data Structure, Offset 17h (Secondary Checksums)

EEPROM Data Structure, Offsets 18h-3Fh

3C589D EEPROM Contents 7-22

Data Field Details

7-23

PCMCIA-Specific Data Structures (3C589)

7-27

PCMCIA-Specific Data Structures (3C589B)

```

### 8 PCMCIA Bus Interfaces

Supported Slot Types and Cycle Types 8-7 PCMCIA Details 8-1

### 9 EXTERNAL CONFIGURATION OPTIONS

Boundary Scan Configuration 9-7

Changes for 3C589D 9-1

Forced Configuration 9-2

Physical Layer Configuration 9-2

Physical Layer Test Access 9-3

### 10 PC CARD DIFFERENCES

Changes in PCMCIA Adapters 10-1 Changes in the PCMCIA Adapters 10-2

### A DRIVER ROUTINE FLOWCHARTS

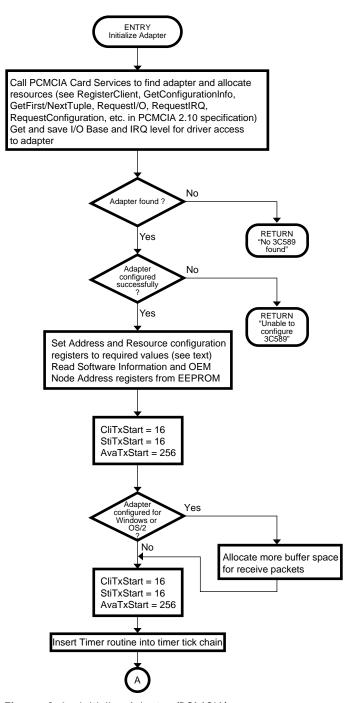

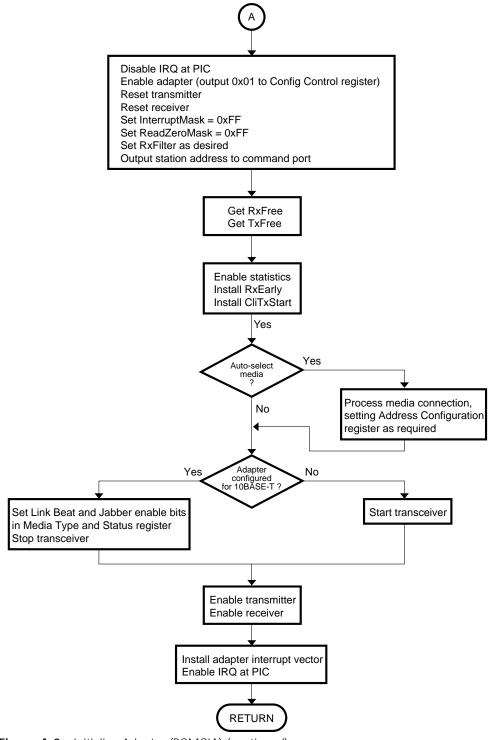

Initialize Adapter (PCMCIA) A-2

Get Bus Type A-4

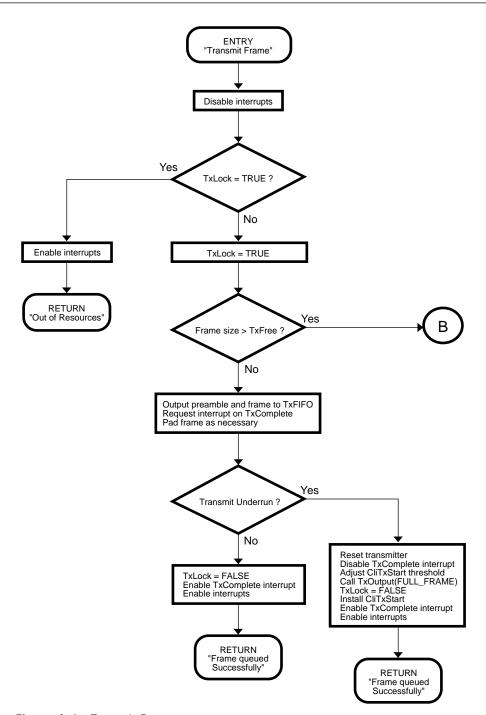

Transmit Frame A-5

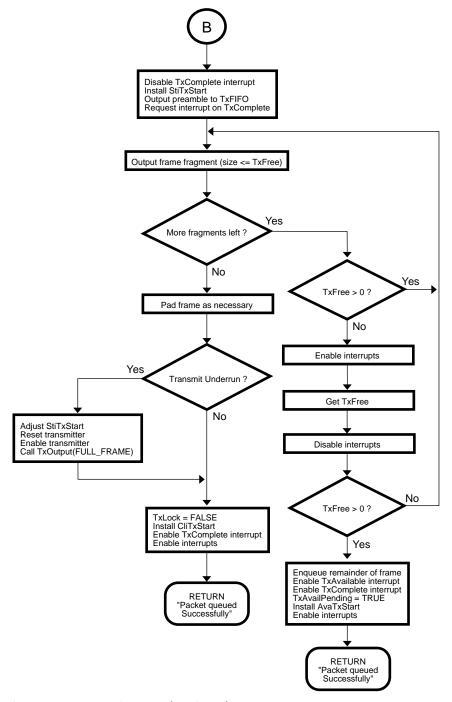

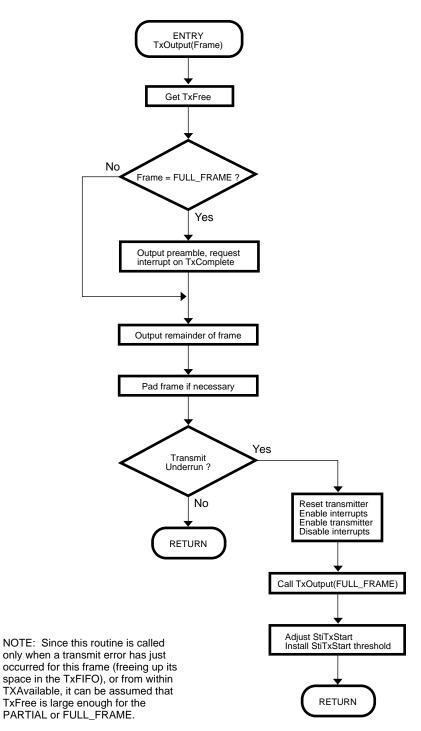

Transmit Output A-7

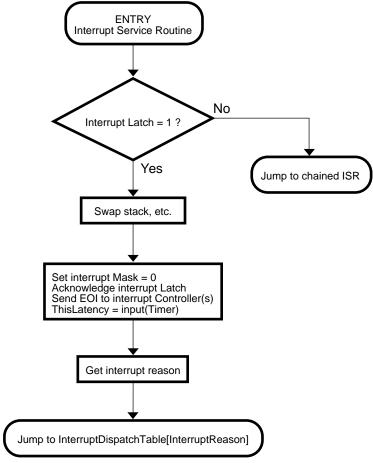

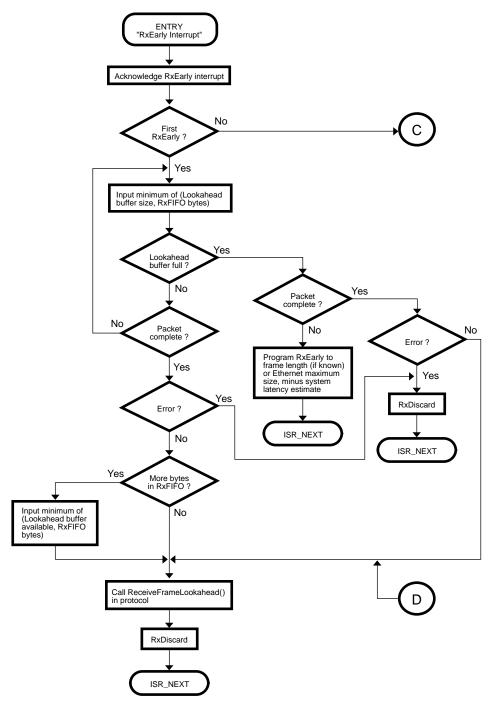

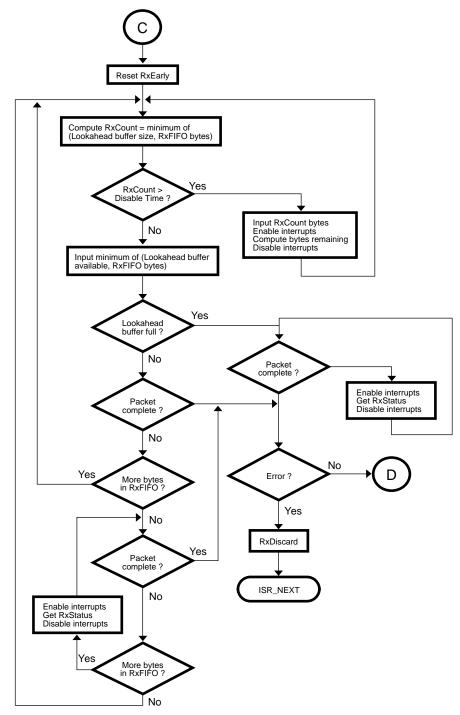

Interrupt Service Routines A-8

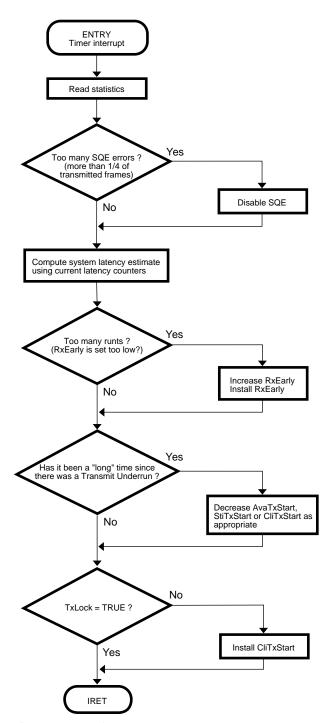

Timer Interrupt A-15

## **FIGURES**

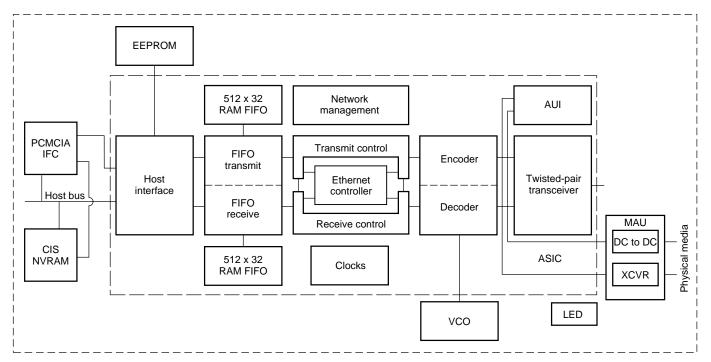

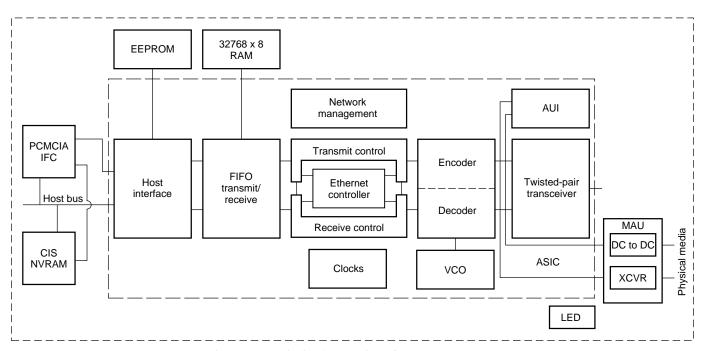

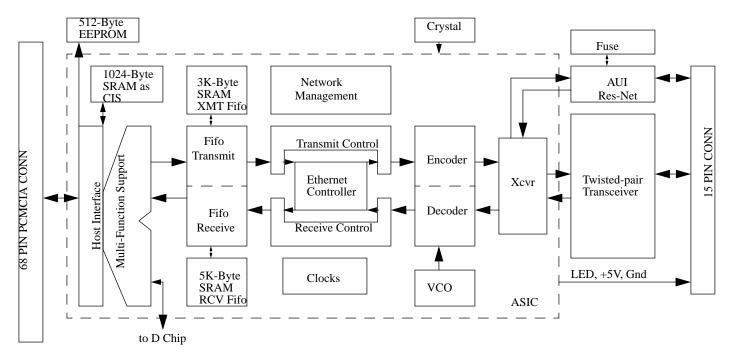

**2-1** Block Diagram for 3C589 2-2

| 2-2        | Block Diagram for 3C589B 2-2                   |

|------------|------------------------------------------------|

| 2-3        | Block Diagram for 3C589D 2-3                   |

|            | D 1 D 1 101 1 01                               |

| 3-1        | Receive Packet Structure 3-1                   |

| 3-2        | Transmit Packet Structure 3-2                  |

| 5-1        | Setup 5-1                                      |

| 5-2        | Operating Set 5-2                              |

| 5-3        | Station Address Setup/Read 5-2                 |

| 5-4        | FIFO Management 5-3                            |

| 5-5        | Diagnostic 5-3                                 |

| 5-6        | Command Results and Internal State 5-4         |

| 5-7        | Statistics Maintained by the Adapter 5-5       |

|            |                                                |

| 6-1        | Command Register 6-1                           |

| 6-2        | Status Register 6-11                           |

| 6-3        | FIFO Register 6-13                             |

| 6-4        | TX Status Register 6-15                        |

| 6-5        | 3                                              |

| 6-6        | TX PIO Data Write Register 6-17                |

| 6-7        | Free Receive Bytes Register 6-17               |

| 6-8        | Free Transmit Bytes Register 6-18              |

| 6-9        | Timer Register 6-18                            |

| 6-10       | Statistics Register 6-19                       |

| 6-11       | Media Type and Status Register 6-21            |

| 6-12       | Net Diagnostic Port Register 6-22              |

| 6-13       | FIFO Diagnostic Port Register 6-23             |

| 6-14       | Ethernet Controller Status Register 6-25       |

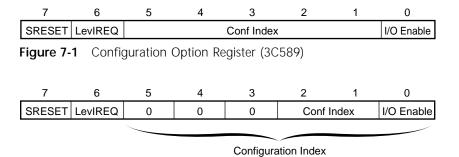

| 7-1        | Configuration Option Register (3C589) 7-2      |

| 7-2        | Configuration Option Register (3C589B) 7-2     |

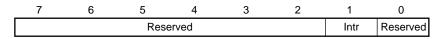

| 7-3        | Configuration and Status Register (3C589) 7-4  |

| 7-4        | Configuration and Status Register (3C589B) 7-4 |

| 7-5        | LAN IOBASE 0 7-5                               |

| 7-6        | IOBASE 1 7-5                                   |

| 7-7        | Modem COR 7-5                                  |

| <b>7-8</b> | Modem CSR 7-6                                  |

| 7-9        | Modem PRR 7-6                                  |

- **7-10** Modem ESR 7-7

- **7-11** Modem IOBASE 0 7-7

- **7-12** Modem IOBASE 1 7-7

- **7-13** Modem IOLIMIT 7-7

- **7-14** Manufacturer ID Register 7-11

- **7-15** Product ID Register 7-11

- **7-16** Configuration Control Register (3C589) 7-12

- **7-17** Configuration Control Register (3C589B) 7-12

- **7-18** Address Configuration Register (3C589) 7-12

- **7-19** Address Configuration Register (3C589B) 7-12

- **7-20** Resource Configuration Register (3C589, 3C589B) 7-14

- **7-21** EEPROM Command Register (3C589, 3C589B) 7-14

- **7-22** EEPROM Data Register 7-16

- **7-23** Command Register 7-16

- **7-24** Internal Configuration Register 7-16

- 7-25 Manufacturing Date Format 7-19

- **7-26** EEPROM Data Structure (Software Information) 7-19

- **7-27** EEPROM Data Structure (Compatibility Word) 7-20

- **7-28** Secondary Software Information 7-21

- A-1 Initialize Adapter (PCMCIA) A-2

- A-2 Initialize Adapter (PCMCIA) (continued) A-3

- A-3 Get Bus Type A-4

- A-4 Transmit Frame A-5

- **A-5** Transmit Frame (continued) A-6

- **A-6** Transmit Output A-7

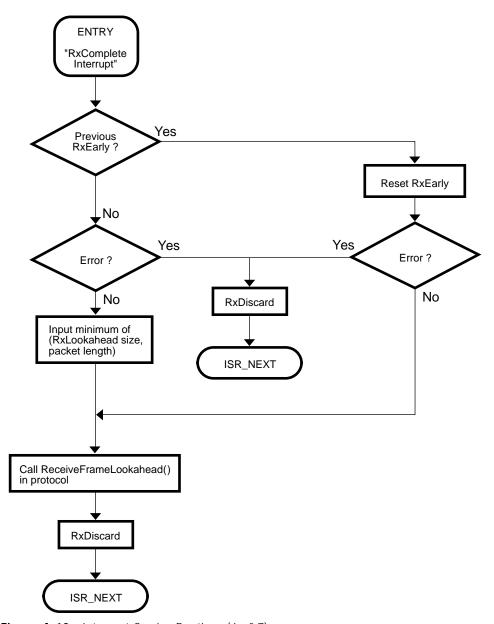

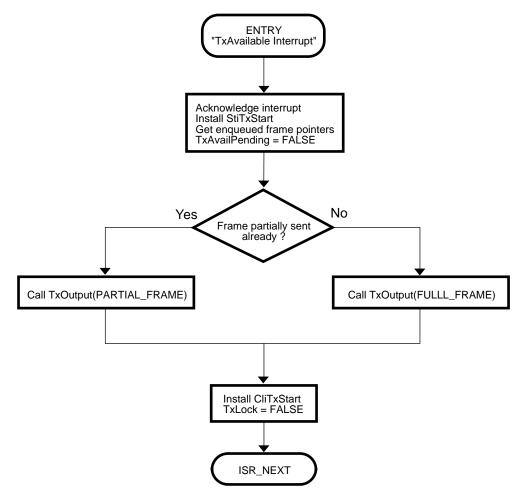

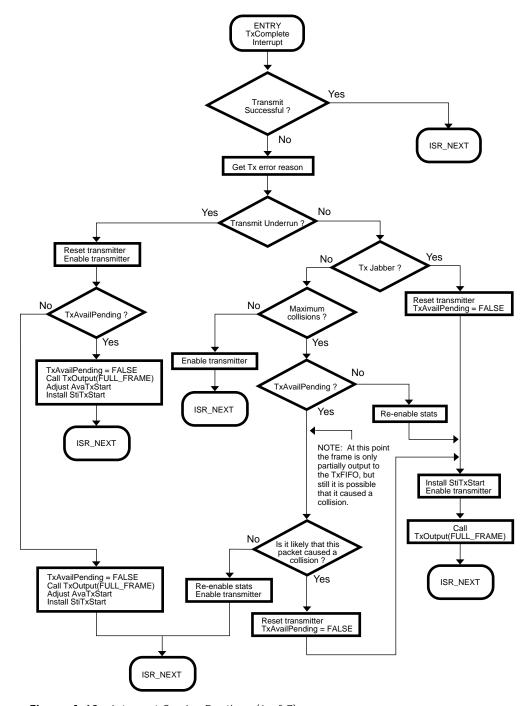

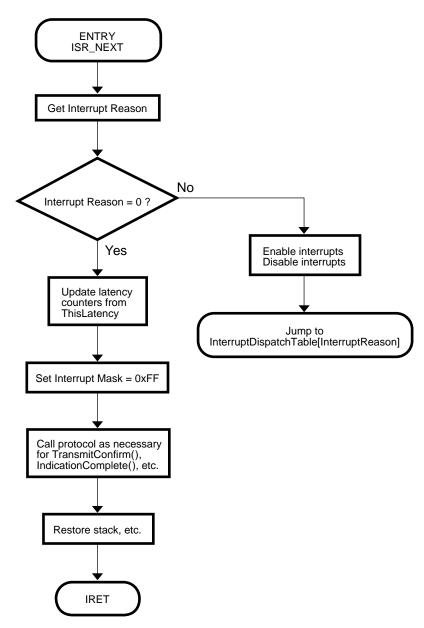

- **A-7** Interrupt Service Routines (1 of 7) A-8

- **A-8** Interrupt Service Routines (2 of 7) A-9

- **A-9** Interrupt Service Routines (3 of 7) A-10

- **A-10** Interrupt Service Routines (4 of 7) A-11

- A-11 Interrupt Service Routines (5 of 7) A-12

- A-12 Interrupt Service Routines (6 of 7) A-13

- A-13 Interrupt Service Routines (7 of 7) A-14

- A-14 Timer Interrupt A-15

# **TABLES**

**1-1** 3C589 PC Card 1-1

| 6-1        | Statistics in Statistics Register 6-20                                                    |     |

|------------|-------------------------------------------------------------------------------------------|-----|

| 7-1<br>7-2 | EEPROM Commands 7-15 ALT EEPROM Commands 7-16                                             |     |

| 8-1<br>8-2 | EtherLink III Adapter Slot and Cycle Types 8-1 PCMCIA Pin Assignments (Pins 1 Through 68) | 8-1 |

## **INTRODUCTION**

### Overview

This document describes the basic architecture of the 3Com® EtherLink® III Parallel Tasking® 3C589 LAN PC Card. Table 1-1 depicts the bus type, cable specifications, and connector types.

**Table 1-1** 3C589 PC Card

| Bus Type | PC Card Number | Connectors per<br>PC Card | Cable<br>Specification | Connector<br>Type |

|----------|----------------|---------------------------|------------------------|-------------------|

| PCMCIA   | 3C589D-TP      | One connector             | 10BASE-T               | RJ-45             |

|          | 3C589D-COMBO   | Two connectors            | 10BASE-T<br>Thin coax  | RJ-45<br>BNC      |

This document is designed for software engineers, independent software developers, and test engineers. Aspects of the architecture have patents applied for.

This PC Card is part of the EtherLink III family of high-performance adapters. The "D" in the 3C589D PC Card number indicates that this PC Card is the fifth generation of the EtherLink III LAN PC Card known as the 3C589 PC Card.

Features of the PC Card include:

- 3Com-designed Ethernet controller, encoder/decoder, 10BASE-T transceiver, and host interface integrated into one ASIC

- 4 K packet buffer

- High performance in client/server applications

- 8 K packet buffer

- VCO (voltage-controlled oscillator)

- 8-bit and 16-bit PCMCIA bus path

- Reduced power consumption

- Power Management (added for 3C589D release)

- Conservative Power Management

The PC Card wakes up on any packet received regardless of whether it is valid or not, and will not go back to sleep until 6.4us after any packets.

Aggressive Power Management

The clock stays on as long as the PC Card is ready to transmit. If the software set the PMmode bit, the clock will be turned off for the duration of a rejected packet, even if the chip is ready to transmit.

## 3C589D PC Card Differences

This section summarizes the changes between the 3C589C and 3C589D PC Cards.

### Internal 8K RAM

The 8K SRAM is inside the ASIC. The CIS will now be inside the chip after Power On Reset.

### Package Reduction

Since there are no external address, data, and control signals for external RAM, chip pins are reduced from 128 to 100 pins. With the 100 pin package, chip size is reduced. Below is a list of the eliminated pins for the 3C589D PC Card:

- LA[15:0]

- LD[7:0]

- A[19:17, 15:13]

- ROMCS

- RAMCS,

- MEMOEB

- MEMEN

- 5 N/C pins

This is a list of the pins added for the 3C589D PC Card:

- MO\_WAIT

- MO\_STSCHG

- MO\_IOR

- MO\_IOWR

- MO\_WE

- MO\_OE\_RDY

- MO\_RDY

- MO\_CLK

- MO\_RESET

- MO\_HALT

# Added Multifunction Support

LAN and MODEM multifunction support is added. Modem registers are available on chip.

### Added PCMCIA Power Down Bit

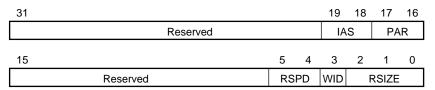

PMmode (power management mode bit) bit is added to Internal Configuration Register(Window 3/Port 00h); power up or reset to 0, meaning conservative power management; software can set to 1 for more aggressive power management.

### Removed PnP

Since PCMCIA does not use PnP; this logic is removed to reduce required real estate.

### **Register Modified**

The following are modified registers for 3C589D PC Card:

- Internal Configuration Register(Window 3/Port 00h)

- Address Configuration (Window 0/Port 06h)

- RomControl Register (Window 3/Port 05h)

- Configuration Control (Window 0/Port 04h)

- Resource Configuration (Window 0/Port 08h)

- PCMCIA COR

- PCMCIA CSR

### Registers Added

The following are new registers added for 3C589D PC Card:

- AltEepromCommandRegister (Window 2/Port 0Ah)

- LanIOBASE0

- LanIOBASE1

- ModemCOR

- ModemCSR

- ModemIOBASE0

- ModemIOBASE1

- ModemLIMIT

- ModemPRR

- ModemESR

- Multi-function Configuration Register(Window 2/Port 08h)

- SRAM Diagnostic Register(Window 2/Port 06h)

## Specification References

For detailed information on Plug and Play and PCMCIA standards, refer to the appropriate source listed below:

- Plug and Play ISA Specification Version 1.0: Microsoft Corporation, One Microsoft Way, Redmond, WA 98052-6399, Tel: (800) 426-9400.

- PCMCIA: Personal Computer Memory Card International Association, 1030 East Duane Avenue, Suite G, Sunnyvale, CA 94086, Tel: (408) 720-0107, Fax: (408) 720-9416.

Refer to Appendix A for a series of process flowcharts that will provide useful information for software developers.

### **ARCHITECTURAL OVERVIEW**

The 3C589 PC Card is designed to be an efficient, low-latency network PC Card optimized for server and client environments. This PC Card has 8 K of buffer space on board, which appears as two dedicated FIFOs to the host (one for transmit and one for receive). The two dedicated FIFOs are of variable size. Various early indication/early start mechanisms are incorporated to improve performance and make operation possible while minimizing the likelihood of overruns or underruns.

The network transceiver consists of a dedicated receiver and a dedicated transmitter, allowing loopback operation at full network bandwidth. At the 10BASE-T interface, automatic polarity reversal and hardware link beat LED indications are supported. At the register level, support is provided for critical network management functions as well as supplementary 10BASE-T functions.

To support a variety of platforms and operating systems, programmed I/O (PIO) is the only method of data transfer supported.

Interrupts can be programmed to signal the CPU under various early indication conditions, and timer mechanisms are incorporated to allow measurement of system latencies. These features reduce latency and optimize performance in platforms where this is appropriate.

A high-level command interface provides for detailed management at the PC Card while using only 16 bytes of I/O space.

The PCMCIA Card Information Structure (CIS) provides information about how the PC Card may be configured. Actual configuration of the card is performed by a slot controller in the host system. This configuration process is usually managed by the card driver communicating with the Card Services software layer supplied on the host. A functional configuration is provided by Card Services each time the card is configured.

In addition, the driver is required to set EtherLink III registers on the PCMCIA card to enable the card. The basis for these register values is provided in the EEPROM on the card.

For detailed information on PCMCIA, refer to the PCMCIA specification, which is available from the Personal Computer Memory Card International Association. Refer to Chapter 1 for address, telephone, and fax information.

### **Block Diagrams**

Refer to Figures 2-1 - 2-2 for block diagrams of the 3C589 PC Cards.

Figure 2-1 Block Diagram for 3C589

Figure 2-2 Block Diagram for 3C589B

Figure 2-3 Block Diagram for 3C589D

### Attribute Memory Map

The highest address bit of the PC Card (A11) does not need to be connected to the A11 of the PC-Card bus. In particular, if it is connected to A16 of the PC-Card bus, the attribute registers will appear at 0x10000 in attribute space, enabling compatibility with previous 3C589 drivers.

### **DATA STRUCTURES**

This chapter describes the data structures used for the PC Card's FIFO.

The PC Card's SRAM is organized into two FIFOs, a TX FIFO for transmit and an RX FIFO for receive. The size of these FIFOs depends on the size of the SRAM used and how space has been allocated between the transmit and receive FIFOs.

Packets being received are written to the RX FIFO by the PC Card, and read out of the RX FIFO by the host software. Packets to be transmitted are written to the TX FIFO by the host software and read out of the TX FIFO by the PC Card.

Multiple packets can be contained within either FIFO, depending on the size of the packets and the storage available.

Packets begin on, and are padded to, double word boundaries. The amount of unused space is visible in the free byte registers: TX Free and RX Free. The next two sections describe the packet structure for receive and transmit packets.

### Receive Packet Structure

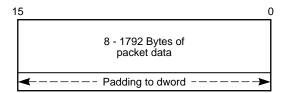

Figure 3-1 shows a model of the receive packet structure for PCMCIA (3C589) as it is stored in the FIFO. The RX Status register can be used to determine the number of bytes of data in the packet.

Figure 3-1 Receive Packet Structure

- Packet data is contained in the first 8 to 1,792 bytes (packets smaller than 60 bytes or larger than 1,514 bytes are flagged as receive errors: runts for the former, oversize for the latter).

- Padding to a double word (dword) boundary follows. These bytes can be read by the host if desired.

- There may be additional bytes per packet, which are hardware overhead. These should be ignored by the host.

## Transmit Packet Structure

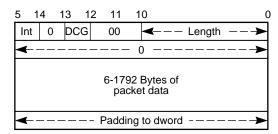

Figure 3-2 shows a model of the transmit packet structure for PCMCIA (3C589) as it is stored in the FIFO.

Figure 3-2 Transmit Packet Structure

Preceding the packet data is the transmit preamble, which is two words long. The first word contains the length of the packet in bytes, the Interrupt on Successful TX Completion bit (bit 15), and the Disable CRC Generation bit. The Interrupt on Successful TX Completion bit indicates whether the host wants an interrupt when the packet has been successfully transmitted (it will get one even if there is an error). This bit is maskable in the Interrupt Mask register. The Disable CRC Generation bit specifies whether the packet data following contains the 4-byte CRC or not. If not (the default), it will be generated automatically by the hardware. This bit may be used by bridging software to avoid regenerating the CRC. Bits that are currently unassigned must be written as zeros.

- The second word of the transmit preamble will be implemented as "don't cares." For future compatibility it is recommended that software write the second word as zeros.

- Packet data follows in the next 6 to 1,792 bytes (packets smaller than 14 bytes are not legal Ethernet packets; those bigger than 1,514 are oversized).

- Padding to a double word boundary is last.

- The packet length is in bytes. If it is not a multiple of 4, pad bytes must be added to bring the packet data in the TX FIFO to a 4-byte boundary. The packet length, however, reflects the true size of the packet in bytes.

Packets that are less than 60 bytes in length will be padded automatically by the hardware.

*Example:* A 14-byte packet would require a preamble and 16 bytes. Automatic padding will produce a 60-byte packet for transport onto the wire.

### **DESCRIPTION OF OPERATION**

The data transfer mode for the 3C589D PC Card is programmed I/O (PIO). As data is received off the wire, it accumulates in the receive FIFO. The driver reads the data off the PC Card a byte, word, or double word at a time through the PIO Data Read register. Similarly, transmit data can be written to the PC Card a byte, word, or double word at a time, and it accumulates in the transmit (TX) FIFO. Once a packet has been transmitted out of the TX FIFO, it is discarded and the space it occupied is available.

The transmit and receive algorithms are described below.

### Receive

## Receive Packet and RX Status

Each packet in the RX FIFO consists of the packet data, padded to a dword boundary. If the host reads beyond the end of the packet, the RX Bytes field of the RX Status register becomes negative.

The RX Status register always maintains the status of the packet at the head of the FIFO.

The driver transfers all of the receive data from the FIFO to host memory via PIO.

After using PIO to read the data, the host must issue an RX Discard command to update the RX Status register for the next packet.

The driver can take interrupts when RX Early threshold bytes of a packet have been received, or when an entire packet has been received.

The driver can determine the size of the packet (number of bytes received so far) at the head of the RX FIFO by reading the RX Status register. Once the packet has been completely received, any errors that occurred during reception are posted in the RX Status register. The packet size can only be determined from RX Status when the packet is "complete."

### **Receive Early**

The RX Early interrupt will be enabled only if the protocol interface allows for early receive indications. However, the driver can take the RX Early interrupt in order to compute the packet size (generally only for 802.3 packets) and generate the equivalent of an early RX Complete indication.

The driver may choose to set the RX Early threshold to slightly less than the protocol's early lookahead size to overlap the reception of the final bytes with the interrupt latency. On entry to the interrupt handler, the RX Status register can be examined to see whether the threshold needs to be adjusted.

Once RX Early has been set, the driver has only to acknowledge the interrupt and it will not become active again (unless reprogrammed higher) until RX Status is updated for the next packet.

The driver must transfer the data from the RX FIFO via PIO into a dedicated lookahead area to make the data addressable to the protocol stack.

### **Receive Complete**

If an RX Early indication is given for the packet, then the lookahead bytes have already been read in. Otherwise, they must be read in now, using PIO to transfer them to the dedicated lookahead area to make the data addressable to the protocol stack.

Once a scatter descriptor is available from the protocol, the data must be copied out of the lookahead area and the RX FIFO.

### **Transmit**

PIO is the only mode of operation supported for transmit. This mode is discussed in more detail below.

## Transmit Packet and Transmit Completion

Each packet in the TX FIFO consists of a transmit preamble followed by the transmit data padded to a dword boundary.

The transmit preamble consists of two words. The first word specifies the length of the packet in bytes, whether or not to generate an interrupt when the packet is transmitted successfully, and (for 3C589B) whether the CRC bytes are to be generated by the hardware or are contained within the packet. The second word is reserved, and should be set to zero.

The packet length is the actual number of bytes in the FIFO to be sent to the wire, excluding any padding to dwords. If the packet is less than the minimum length (60 bytes not including CRC), it need not be padded by the software. Instead, the PC Card will pad the packet to the minimum length before giving it to the Ethernet controller.

The driver will typically request an interrupt on successful transmit completion only if the protocol has requested a confirmation. The driver must queue up such requests to retrieve the protocol identification for the transmit confirmation. When any Transmit Complete interrupt comes in, the driver examines the TX Status register. This completion is for the head of the queue if the Interrupt Requested bit is set in TX Status, since transmits complete in order. The driver must serialize this process to guarantee that it works properly.

If an error occurs while the packet is being transmitted, the PC Card always generates an interrupt and disables the transmitter. If the host determines from TX Status that the confirmation is not for a queued request, it can use the error information to update its statistics counters. In any case, the host must manually restart the transmitter by issuing the TX Enable command once it has emptied the TX Status stack as the result of an error.

### Transmitting a Packet

All data to be transmitted must be moved into the FIFO by the driver. Multiple packets can be moved into the FIFO as long as the host is prepared to deal with running out of TX FIFO space.

Typically the driver will copy as much of the packet to the PC Card as possible. If one or more packets precede this one in the FIFO, then the FIFO can run out of space. If this happens, the driver can issue the TX Available command to request an interrupt once there is sufficient space for the rest of the packet.

The Set TX Available Threshold command causes the PC Card to generate an interrupt when the specified number of bytes is available in the TX FIFO. This allows the driver to return and continue copying the data later, when some of the data in the TX FIFO has been transmitted.

When TX Available is used, the possibility of an underrun always exists if the interrupt latency is high enough (for example, 1 ms on switching windows under OS/2®). If underruns are a problem, they can be avoided by reprogramming the TX Start threshold to be greater than the number of bytes transferred to that point. That way the driver can guarantee that the packet will not start transmitting before the TX Available interrupt is serviced. The driver can be written so that it makes this adjustment only when the amount of the packet copied to the FIFO is small enough for concern (that is, less than the number of bytes that can be transmitted within the measured interrupt latency), or the driver can make the adjustment semipermanently (reset on some timer tick multiple) whenever an underrun occurs.

When a packet is currently being copied to the FIFO or if the FIFO is full, and the protocol issues another transmit request, the driver will have to queue the gather descriptor. However, this queue—the awaiting download queue—is different from the transmit completion queue described above. The awaiting download queue is emptied and the queue entries released by copying the data to the PC Card.

## Disable CRC Generation (3C589B)

A typical driver will leave the DCG bit reset so the Ethernet controller will automatically generate the CRC for the packet that is to be transmitted. The DCG bit should only be set if the host software generates its own CRC, or if the host software is performing a bridging function, which must forward packets that include the original CRC.

When this bit is set, packets must be padded manually to a dword boundary by the driver. Also, packets must be 64 bytes in length, including CRC.

### Transmit Underrun

When the TX FIFO underruns, the PC Card will generate a bad CRC for the packet. A Transmit Complete interrupt will be generated to the driver, specifying a transmit underrun error. When the driver detects this error, it must first issue a TX Reset command before using TX Enable to reenable the transmitter.

Whenever the driver encounters an underrun, it should take special care to guarantee that the next transmit packet does not underrun by setting the TX Start threshold large enough so that it does not start until the packet is completely copied to the PC Card. For subsequent packets, the driver may react quickly to changes in the operating environment by adjusting the TX Start threshold according to new information on interrupt latencies, and other system performance measurements. The exact mechanism used is beyond the scope of this document.

Underruns occur only when the packet is being copied to the PC Card. Therefore, the driver should be able to retransmit the packet. Checking the number of underruns and retransmissions can greatly reduce the performance impact of an underrun (an occasional underrun is acceptable).

### WINDOW SET

The 3C589 PC Card register set consists of several 8-word register windows. The windows are numbered, and each window presents a different register set to the host through the standard 16-byte I/O space of the adapter.

At power-up, or after a Global Reset, Window 0 is the working register set. Window 0 contains setup information, including the registers reflecting the EEPROM setup information. Window 1 contains the standard register set, which includes all of the registers used on the driver critical path.

Accessing other windows will require switching away and then back again. The driver will switch to Window 1 during initialization and assume that this set is always current from that point on. Other windows contain the statistics information, report the adapter state, allow for reconfiguration, and support various diagnostics.

A soft reset from the host will also select Window 0 as the working register set.

### Window 0 Registers - Setup

This window contains configuration registers, including setup and EEPROM access.

|        | Write function           |          |

|--------|--------------------------|----------|

| Port   |                          |          |

| offset | High byte                | Low byte |

| 0E     | Command                  |          |

| 0C     | EEPROM data              |          |

| 0A     | EEPROM command           |          |

| 80     | Resource configuration*† |          |

| 06     | Address configuration*†  |          |

| 04     | Configuration control*   |          |

| 02     |                          |          |

| 00     |                          |          |

|        |                          |          |

### Read function

| High byte                | Low byte |

|--------------------------|----------|

| Window (0-7)             | Status   |

| EEPROM data              |          |

| EEPROM command           |          |

| Resource configuration   |          |

| Address configuration    |          |

| Configuration control    |          |

| Product ID*†/Adapter ID§ |          |

| Manufacturer ID          |          |

Figure 5-1 Setup

### Changes for 3C589D

- Modified Configuration Control (Window 0/Port 04h)

- Modified Address Configuration (Window 0/Port 06h)

- Modified Resource Configuration (Window 0/Port 08h)

<sup>\*</sup> ISA/EISA PCMCIA adapter

<sup>†</sup> PCMCIA adapter. The values are not loaded automatically at power-up and must be explicitly initialized by the driver software. See Chapter 7.

<sup>§</sup> MCA adapter

### Window 1 Registers -**Operating Set**

This window set is assumed to be on critical path. The TX Status and Timer registers must be read separately as byte registers. The TX PIO and RX PIO registers may be written and read as bytes, words, or double words.

|        | Write function    |          | Read fund  |

|--------|-------------------|----------|------------|

| Port   |                   |          |            |

| offset | High byte         | Low byte | High byte  |

| 0E     | Command           |          | Window (   |

| 0C     |                   |          | Free trans |

| 0A     | TX Status         |          | TX Status  |

| 08     |                   |          | RX Status  |

| 06     |                   |          |            |

| 04     |                   |          |            |

| 02     | TX PIO data write |          | RX PIO d   |

| 00     | TX PIO data write |          | RX PIO d   |

|        |                   |          |            |

Figure 5-2 Operating Set

## Read function

| High byte           | Low byte |

|---------------------|----------|

| Window (0-7)        | Status   |

| Free transmit bytes |          |

| TX Status           | Timer    |

| RX Status           |          |

|                     |          |

|                     |          |

| RX PIO data read    |          |

| RX PIO data read    |          |

|                     |          |

### Window 2 Registers -**Station Address** Setup/Read

The station address must be read out of the EEPROM and written into these registers before reception is enabled.

|        | Write function                   |           |

|--------|----------------------------------|-----------|

| Port   |                                  |           |

| offset | High byte                        | Low byte  |

| 0E     | Command                          |           |

| 0C     |                                  |           |

| 0A     | AltEEprom Command Reg            |           |

| 80     | Multi-function Configuration Reg |           |

| 06     | SRAM Diagnostic                  |           |

| 04     | Address 5                        | Address 4 |

| 02     | Address 3                        | Address 2 |

| 00     | Address 1                        | Address 0 |

| 00     | Address 1                        | Address 0 |

Figure 5-3 Station Address Setup/Read

#### Read function

| High byte                    | Low byte  |  |  |

|------------------------------|-----------|--|--|

| Window (0-7)                 | Status    |  |  |

|                              |           |  |  |

| AltEEprom Command Reg        |           |  |  |

| Multi-function Configuration |           |  |  |

| Reg                          |           |  |  |

| SRAM Diagnostic              |           |  |  |

| Address 5                    | Address 4 |  |  |

| Address 3                    | Address 2 |  |  |

| Address 1                    | Address 0 |  |  |

### Changes for 3C589D

- Added SRAM Diagnostic Register (Window 2/Port 06h)

- Added Multi-function Configuration Register (Window 2/Port 08h)

- Added AltEEpromCommand Register (Window 2/Port 0Ah)

### Window 3 Registers – FIFO Management

|             | Write function (3C5            | 509, 3C579, 3C529, 3C589) | Read function (3C509, 3C579, 3C529, 3C589) |          |  |

|-------------|--------------------------------|---------------------------|--------------------------------------------|----------|--|

| Port offset | High byte                      | Low byte                  | High byte                                  | Low byte |  |

| 0E          | Command                        | ,                         | Window (0-7)                               | Status   |  |

| 0C          |                                |                           | Free transmit bytes                        |          |  |

| 0A          |                                |                           | Free receive bytes                         |          |  |

| 08          |                                |                           | Resource configurati                       | on       |  |

| 06          |                                |                           | Tx reclaim threshold                       | *        |  |

| 04          |                                |                           |                                            |          |  |

| 02          |                                |                           |                                            |          |  |

| 00          |                                |                           |                                            |          |  |

|             |                                |                           | *MCA adapter                               |          |  |

|             | Read function (3C509B, 3C589B) |                           | Read function (3C509B, 3C589B)             |          |  |

| Port        |                                |                           | 18.1.1.4                                   |          |  |

| offset      | High byte                      | Low byte                  | High byte                                  | Low byte |  |

| 0E          | Command                        |                           | Window (0-7)                               | Status   |  |

| 0C          |                                |                           |                                            |          |  |

| 0A          |                                |                           | Free receive bytes                         |          |  |

| 80          |                                |                           |                                            |          |  |

| 06          |                                |                           |                                            |          |  |

| 04          | ROM control*                   |                           | ROM cotnrol*                               |          |  |

| 02          | Internal configuration         |                           | Internal configuration                     |          |  |

| 00          | internal configuration         | JII                       | internal configuration                     |          |  |

|             | *3C509B only                   | FIFO.N4                   | *3C509B only                               |          |  |

Figure 5-4 FIFO Management

Changes for 3C589D

- Modified Internal Configuration Register (Window 3/Port 00h)

- Modified RomControl Register (Window 3/Port 05h) (R/W)

### Window 4 Registers – Diagnostic

| •      |                            |          |

|--------|----------------------------|----------|

|        | Write function             |          |

| Port   |                            |          |

| offset | High byte                  | Low byte |

| 0E     | Command                    |          |

| 0C     |                            |          |

| 0A     | Media type and status      |          |

| 08     | Ethernet controller status |          |

| 06     | Net diagnostic             |          |

| 04     | FIFO diagnostic            |          |

| 02     |                            |          |

| 00     |                            |          |

|        |                            |          |

Figure 5-5 Diagnostic

### Read function

| High byte                  | Low byte |  |  |

|----------------------------|----------|--|--|

| Window (0-7)               | Status   |  |  |

|                            |          |  |  |

| Media type and status      |          |  |  |

| Ethernet controller status |          |  |  |

| FIFO diagnostic            |          |  |  |

|                            |          |  |  |

|                            |          |  |  |

|                            |          |  |  |

| •                          |          |  |  |

### Window 5 Registers – Command Results and Internal State

This window contains registers that allow the parameters set by command to be read back for diagnostic purposes. These registers can be accessed as bytes as well as words.

|             | Write function (All) |          |        | Read function (3C509, 3C579, 3C589)   |          |

|-------------|----------------------|----------|--------|---------------------------------------|----------|

| Port offset | High byte            | Low byte |        | High byte                             | Low byte |

| 0E          | Command              |          |        | Window (0-7)                          | Status   |

| 0C          |                      |          |        | Read zero mask                        |          |

| 0A          |                      |          |        | Interrupt mask                        |          |

| 80          |                      |          |        | RX filter (lower 4 bits               | only)    |

| 06          |                      |          |        | RX early threshold                    |          |

| 04          |                      |          |        |                                       |          |

| 02          |                      |          |        | TX available threshold                |          |

| 00          |                      |          |        | TX starts threshold + 4               |          |

|             |                      |          |        | Read function (3C509B, 3C529, 3C589B) |          |

|             |                      |          | Port   |                                       | •        |

|             |                      |          | offset | High byte                             | Low byte |

|             |                      |          | 0E     | Window (0-7)                          | Status   |

|             |                      |          | 0C     | Read zero mask                        |          |

|             |                      |          | 0A     | Interrupt mask                        |          |

|             |                      |          | 08     | RX filter (lower 4 bits only)         |          |

|             |                      |          | 06     | RX early threshold                    |          |

|             |                      |          | 04     |                                       |          |

|             |                      |          | 02     | TX available threshold                | 1        |

|             |                      |          | 00     | TX starts threshold +                 | 4        |

Figure 5-6 Command Results and Internal State

### Window 6 Registers – Statistics

Reading a statistic also zeroes it. These registers may be read only while statistics collection has been disabled temporarily. Statistics that are word-sized must be read as words, and those that are bytes must be read as bytes. Writing to these registers is supported for debugging purposes. These registers can be accessed as bytes as well as words. Refer to the section "Statistics Registers" in Chapter 6 for more information.

|        | Write function                                 |                                              |  | Read function                                  |                                              |  |

|--------|------------------------------------------------|----------------------------------------------|--|------------------------------------------------|----------------------------------------------|--|

| Port   |                                                |                                              |  |                                                |                                              |  |

| offset | High byte                                      | Low byte                                     |  | High byte                                      | Low byte                                     |  |

| 0E     | Command                                        |                                              |  | Window (0-7)                                   | Status                                       |  |

| 0C     | Total bytes transmitted OK                     |                                              |  | Total bytes transmitted OK                     |                                              |  |

| 0A     | Total bytes received OK                        |                                              |  | Total bytes received OK                        |                                              |  |

| 08     |                                                | Transmit deferrals                           |  |                                                | Transmit deferrals                           |  |

| 06     | Frames received OK                             | Frames transmitted OK                        |  | Frames received OK                             | Frames transmitted OK                        |  |

| 04     | Received overruns                              | Late collision on transmit                   |  | Received overruns                              | Late collision on transmit                   |  |

| 02     | Frames transmitted after exactly one collision | Frames transmitted after multiple collisions |  | Frames transmitted after exactly one collision | Frames transmitted after multiple collisions |  |

| 00     | Frames transmitted no CD heartbeat (SQE)       | Carrier sense lost during transmission       |  | Frames transmitted no CD heartbeat (SQE)       | Carrier sense lost during transmission       |  |

|        |                                                |                                              |  |                                                |                                              |  |

Figure 5-7 Statistics Maintained by the Adapter

## Added Registers for 3C589D

- LAN IOBASE 0 (0x80a)

- LAN IOBASE 1 (0x80c)

- ModemCOR (0x900)

- ModemCSR (0x902)

- Modem PRR (0x904)

- Modem ESR (0x908)

- Modem IOBASE 0 (0x90a)

- Modem IOBASE 1 (0x90c)

- Modem IOLIMIT (0x912)

- Multi-function Configuration Register

### **REGISTER DEFINITIONS**

This chapter describes the function and use of each register needed in normal operation of the 3C589 PC Card. The adapter configuration and enable registers in Window 0 are explained in Chapter 7.

### PCMCIA (3C589, 3C589B)

The registers defined in this section are those of the EtherLink III ASIC portion of the PCMCIA board. PCMCIA-specific registers are defined in Chapter 7.

### **Command Register**

Function: Issues commands to PC

Card.

Location: All windows/Port 0E

Type: Write only Size: 16 bits

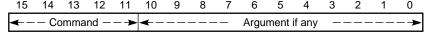

Figure 6-1 Command Register

Bit Description: Bits 15–11 5-bit code for command to be executed.

Bits 10–0 11-bit argument if any. For commands with

no arguments, these bits should be set to

zero for future compatibility.

## Command Register Conventions

The Command register controls many PC Card functions. For example, a command is used to switch windows. In general, commands must be written as a word. However, the following is acceptable for commands with no parameters:

mov dx, PortCmdStatus

mov ah, CMD\_X out dx, ax

Commands, except those marked with an asterisk (\*), execute in one I/O cycle. For commands that are not completed in one cycle, the software must poll the Command-in-Progress bit in the Status register to determine when one of these commands is completed. Since only a single command can be outstanding at any given time, the host must do this in a critical section.

The commands are listed below. The 16 bits of each command register are given after each command name, in this format:

command argument 0000 0 XXX XXXX XXXX

The 5-bit command code is specified in binary. The 11-bit argument follows the vertical bar in the format aaa aaaa aaaa. Also:

- An x signifies a variable bit in the argument.

- A 0 signifies a bit that must be zero.

- A z signifies either a 0 or a 1, but will be treated as a 0.

- A 1 signifies either a 0 or a 1, but will be treated as a 1.

### Global Reset\*

0000 0 000 0000 0000 (3C589) 0000 0 000 00xx xxxx (3C589B)

### **PCMCIA (3C589)**

This command has the same effect as a power-up reset. It is implemented with a minimum amount of logic to ensure success. This command requires a significant amount of time to execute, since it involves rereading the EEPROM. The Timer register may not be used for this delay period and the Command-in-Progress bit will not be visible. The host must wait at least 1 ms after issuing this command before it touches the PC Card again. The argument to this command must be all zeros.

### (3C589B)

This command argument masks the Global Reset command to a module if the mask bit is set. The command has the same effect as a power-up reset for the modules which are reset and has no effect on modules which are masked.

The Command-in-Progress bit will not be visible if a Host Reset command is executed. If the argument is all zeros, this Global Reset command has the same effect as the PCMCIA Global Reset command, and it resets all of the modules.

The command argument is defined as follows:

- Bit 0: TPAUI Reset. Resets the 10BASE-T and AUI transceivers.

- Bit 1: EnDec Reset. Resets the internal encoder/decoder.

- Bit 2: Network Reset. Resets the Network module, including the Ethernet controller.

- Bit 3: FIFO Reset. Resets the FIFO module.

- Bit 4: AISM Reset. Resets the Auto Initialize state machine. This forces the EEPROM to be reread unless the PC Card is in test mode.

- Bit 5: Host Reset. Resets the bus interface, excluding the Auto Initialize state machine. It does not reset the POS registers, so the current base addresses remain valid.

In general, host software should reset all modules, using a command argument of zero (0). The other arguments are typically intended for debugging.

### PCMCIA (3C589, 3C589B)

The Global Reset command resets the EtherLink III ASIC but not the PCMCIA interface chip. All ASIC registers must be reloaded following this command.

### **Select Register Window**

0000 1 000 0000 0XXX

This command selects register window xxx. The current register window is available in the Status register. After power-up or Global Reset, which includes host reset, Window 0 is in effect.

### Start Coaxial Transceiver

0001 0 000 0000 0000

This command affects only the 10BASE2 operation. It starts the DC-DC converter that drives the on-board coaxial Ethernet transceiver. After power-up, the coaxial transceiver must be started manually with this command. The host must delay at least 800 µs after issuing this command before using the coaxial transceiver. This can be accomplished by starting the timer and waiting until it pegs at its maximum value of FFh. The host must read the Address Configuration register (refer to the "Address Configuration Register" section in Chapter 7) from the EEPROM to determine whether to issue this command.

### PCMCIA (3C589, 3C589B)

The Start Coaxial Transceiver command has only one function in the PCMCIA card: it turns on the LED.

### **RX** Disable

0001 1 000 0000 0000

This command disables the Ethernet controller receiver. If a packet is in the process of being received, it will be received and the Ethernet controller receiver will be disabled after the packet has been completely received. To enable the receiver, use RX Enable. After power-up, the receiver is in the disabled state.

#### **RX Enable**

0010 0 000 0000 0000

This command enables the Ethernet controller receiver. If a packet is in the process of being transmitted on the wire, it will not be received. To disable the receiver, use RX Disable or RX Reset. After power-up, the receiver is in the disabled state and must be enabled with this command.

### **RX Reset**

0010 1 000 0000 0000

(AII)

0010 1 000 0000 XXXX

(3C589B)

Do not issue RX Reset unless it is absolutely required.

#### ΑII

This command empties the RX FIFO, disables the Ethernet controller, resets the RX Filter and RX Early threshold to defaults, and aborts reception if a packet is currently being received. The argument to this command must be all zeros.

## PCMCIA\* (3C589B)

This command argument masks the RX Reset command to a module if the mask bit is set. The argument is defined as follows:

Bit 0: TPAUL RX Reset. Resets the 10BASE-T and AUI transceiver logic.

Bit 1: EnDec RX Reset. Resets the encoder/decoder receive logic.

Bit 2: Network RX Reset. Resets the Network Receive logic. Aborts any current packet reception. This includes disabling the Ethernet controller and receiver. Resets RX Filter to disable.

Bit 3: FIFO RX Reset. Resets the FIFO Receive logic. This includes emptying the RX FIFO and resetting RX Filter to disable and RX Early Threshold to default.

Set mask bits to zeros for compatibility with all EtherLink III adapters.

### **RX Discard Top Packet\***

### 0100 0 000 0000 0000

This command discards the remainder of the top packet in the RX FIFO. The host can also use this command to discard packets that are in error or are not needed. One reason for discarding packets is that they do not match any multicast address currently enabled through the protocol interface.

If the packet has not been completely received, the PC Card will ignore the remainder of the packet as if the receiver had been disabled, then reenabled.

If the packet has been completely received, use the RX Status register to update any statistics before issuing this command.

The driver must issue this command at the completion of each packet received regardless of whether the packet reception was in error.

The RX Discard command pops the current RX Status and replaces it with the next packet status, if any. It is used to get from one packet to the next in the RX FIFO.

### TX Enable

### 0100 1 000 0000 0000

This command enables the Ethernet controller transmitter. It does not initiate transmission of a packet, which will not occur until at least the TX Start threshold bytes of the packet (or the entire packet) are in the TX FIFO. At power-up, the transmitter is disabled and must be enabled with this command. To disable the transmitter, use TX Disable. Transmit errors will also disable the transmitter.

### TX Disable

### 0101 0 000 0000 0000

This command disables the Ethernet controller transmitter. If a packet is currently being transmitted (that is, it has been presented to the Ethernet controller), issuing this command will not stop the transmission. The transmitter will be disabled after the packet has been completely transmitted (or has reached a nonrecoverable error). The transmitter is disabled on power-up, and can also become disabled as a result of a transmit error.

#### TX Reset\*

| 0101 1 000 0000 0000 | (All)    |

|----------------------|----------|

| 0101 1 000 0000 XXXX | (3C589B) |

| 0101 1 X00 0000 XXXX | (3C589B) |

This command, when bits 0–3 are all zeros, empties the TX FIFO, disables the Ethernet controller transmitter, and resets the TX Available and TX Start thresholds to default values. If a packet is currently being transmitted, the transmit will be aborted.

It is recommended that an argument of all zeros be used to ensure compatibility with all EtherLink III PC Cards.

After an underrun or jabber error on transmit, a TX Reset is required. Do not issue TX Reset unless it is absolutely required.

### PCMCIA (3C589B)

This command resets the specified transmit logic when any of bits 0–3 are nonzero.

Below are the bit positions of the various reset masks in the TX Reset command field with the internal signal name and a brief description. When any of these bits are set, the reset to the corresponding transmit modules is masked (that is, that module will not be reset).

# The argument is defined as follows:

Bit 0: TP AUI TX Reset. Resets the 10BASE-T and AUI transmit logic.

Bit 1: EnDec TX Reset. Resets the encoder/decoder transmit logic.

Bit 2: Network TX Reset. Resets the network transmit logic. This includes the

TX Status stack, and also disables the Ethernet controller and transmitter (equivalent to TX Disable).

3C589B only: If a packet is in the midst of being transmitted, Network TX Reset will be asserted according to the value of bit 10. If bit 10=0, the reset will be delayed until the transmission has been completed (Command in Progress will be asserted during this period), or is about to be retried. If FIFO Reset is also asserted, the TX FIFO will be emptied immediately, causing any partially transmitted packet to be sent out with a guaranteed bad CRC (no error will be visible in TX Status, since that is reset by Network TX Reset). In this case Command in Progress will not be asserted for more than 6  $\mu$ s or so. If bit 10=1, the transmit will be aborted immediately without guaranteeing a bad CRC, though a good CRC is highly unlikely.

Bit 3: FIFO TX Reset. Resets the FIFO transmit logic. This includes emptying the TX FIFO and resetting TX Available and TX Start thresholds to defaults.

# **PCMCIA (3C589B)**

TX Reset is required after a Power Up command is issued while the chip is in a Power Down Full state.

If a packet is being transmitted when this command is issued, the reset will occur immediately or be delayed, depending on the value of bit 10:

Bit 10: 0 = Transmit abort is delayed until a guaranteed bad CRC can be generated on the packet.

1 = Transmit will be aborted immediately. A bad CRC is not guaranteed to be generated. See discussion above.

## Request Interrupt

0110 0 000 0000 0000

This command sets the Interrupt Requested bit in the Status register, causing an interrupt whenever that interrupt bit is unmasked.

# Acknowledge Interrupt

0110 1 000 XXXX XXXX

This command acknowledges the interrupt reasons specified in the argument. These bits are laid out identically to those in the Status register. If a bit is set in the argument, it acknowledges the reason for that interrupt, and will in some cases turn off the bit in the Status register. In other cases, the bit in the Status register is wired to the PC Card state, and that state must be changed in order to turn the bit off. In this case, setting the bit in the argument has no effect. Multiple bits may be set in the argument. If a bit is set in the argument and that bit is not set in the Status register, nothing happens. For each bit, the following specifies whether or not acknowledging it will force the Status bit off.

■ Interrupt Latch 0110 1 000 0000 0001

This command turns off the Status register bit, releasing the interrupt. This bit must be acknowledged after all the interrupt reasons have been processed or masked off by setting the Interrupt Mask to zero (see Set Interrupt Mask).

Adapter Failure

0110 1 000 0000 0010

This command does nothing. The bit indicating the reason for the adapter failure in the FIFO Diagnostic register (bit 13 or bit 10) must be cleared to recover from this state.

■ TX Complete 0110 1 000 0000 0100

This command does nothing. The host must write the TX Status register (popping it) to turn the bit off (assuming there are no other transmit completions pending).

■ TX Available 0110 1 000 0000 1000

This command turns off the TX Available bit and resets the TX Available threshold to its disabled value. The Set TX Available Threshold command must be reissued each time it is required.

RX Complete 0110 1 000 0010 0000

This command does nothing. To turn off the Status register bit, the host should read the packet out of the RX FIFO and must issue an RX Discard command.

RX Early 0110 1 000 0010 0000

This command turns off the Status register bit. RX Early will remain off for the duration of this packet unless the RX Early threshold is reprogrammed. To change the RX Early threshold without having this bit turn on again, reprogram the threshold before acknowledging the RX Early bit. See the Set RX Early Threshold command for more details.

- Interrupt Requested 0110 1 000 0100 0000

This command turns off the Status register bit.

- Update Statistics 0110 1 000 1000 0000

This command does nothing. To turn off the Status register bit, read the statistics. This will reset them all to zero.

# Set Interrupt Mask

0111 0 000 XXXX XXXZ

This command sets the Interrupt mask; each bit that is set enables interrupts from that interrupt source. To mask off all interrupts from the PC Card, set the Interrupt mask to zero. When an interrupt reason is masked off, the corresponding interrupt bit in the Status register is still readable, although it is no longer a source for interrupts. Use the Set Read Zero mask command to force the bits to read as zero. The bits are laid out identically to their locations in the Status register. At power-up, the Interrupt mask defaults to zero.

#### Set Read Zero Mask

0111 1 000 XXXX XXXZ

This command sets the Read Zero mask; each bit that is clear causes the corresponding bit in the Status register to read as zero. The Read Zero mask is applied to the Status register before the Interrupt mask. Clearing a bit in the Read Zero mask also prevents it from causing interrupts.

To force all interrupt sources to zero, set the Read Zero mask to zero. Use the Set Interrupt Mask command to disable interrupts and still allow the bit in the Status register to be readable. The bits are laid out identically to their locations in the Status register. At power-up, the Read Zero mask defaults to zero.

The Interrupt Latch bit cannot be forced to zero with this command.

#### Set RX Filter

#### 1000 0 000 0000 XXXX

This command sets the Receive filter as follows:

0001 Individual address

0010 Group (multicast) addresses

0100 Broadcast address

1000 All addresses (promiscuous mode)

At power-up, the Receive filter defaults to zero and must be set with this command before any packets can be received. Enabling group address reception implies broadcast reception. There is no individual filtering of group/multicast addresses. Promiscuous mode implies all others.

## Set RX Early Threshold

# 1000 1 XXX XXXX XXZZ

This command sets a value for the RX Early threshold. When the number of bytes in the RX FIFO exceeds the argument (whether occurring before or after this command is issued), an RX Early interrupt will be generated to the host. A multiple of four with a range of 0 to 1,792 bytes is used. To disable, set to any value greater than 1,792. The PC Card truncates the argument to a dword multiple.

The RX Complete bit masks the RX Early bit. Whenever RX Complete is set, RX Early will be clear. Also, when the Ethernet controller signals the end of a receive packet, thereby clearing the RX Incomplete bit on the bottom of the RX Status stack, RX Early will be automatically acknowledged or cleared.

It is possible to reprogram the RX Early Threshold value in the middle of receiving a packet and still have the interrupt go off when appropriate. This feature may be used by the software to try to take an interrupt just before its computed packet length in order to overlap some of the packet reception with the expected interrupt latency. To do this, and to generate another interrupt, the RX Early threshold must be reprogrammed *after* the RX Early interrupt has been acknowledged.

Normal collisions may be received as bad packets by the host if the RX Early threshold is set to less than 60 bytes (one slot time). The driver must be prepared to increase this value if too many bad packets result when the setting is less than 60 bytes.

#### **PCMCIA (3C589)**

These PC Cards hide 16 bytes of an incomplete packet from the host. Therefore, if RX Early is set to 24, 40 bytes must be received before the packet becomes visible to the host. At that point RX Status shows 24 bytes received. When the packet reception is complete, the 16 bytes will be added to the byte count in the RX Status register all at once. Therefore, the software does not need to be aware of this process.

The power-on default for this threshold is 2,032 bytes.

#### PCMCIA (3C589B)

The power-on default for this threshold is 2,044 bytes.

The minimum threshold for RX Early is 8. Setting RX Early to less than 8 makes it operate the same as if it were set to 8.

# Set TX Available Threshold

#### 1001 0 XXX XXXX XXZZ

This command sets the TX Available threshold, which specifies the number of free bytes required by the host. A TX Available interrupt will be generated when the number of free bytes in the TX FIFO exceeds this threshold. This allows the host to return and perform other processing until there is sufficient free space to continue to copy data to the TX FIFO.

A multiple of four with a range of 0 to 2,044 bytes is used. Setting this threshold to any value greater than 1,792 disables it regardless of the TX FIFO size.

Once the TX Available bit is acknowledged, the threshold returns to default/ disabled, and it will not go off again. Therefore, the Set TX Available threshold command must be reissued each time the driver decides to return control until sufficient space is available to continue.

# Set TX Start Threshold

# 1001 1 XXX XXXX XXZZ

This command specifies the number of bytes required in the TX FIFO before the PC Card will start transmitting the packet. The packet will start transmitting either when the number of bytes in the TX FIFO exceeds the argument or when the entire packet has been copied to the TX FIFO. A multiple of four with a range of 0 to 1,792 or above bytes is used. The PC Card truncates the argument to a dword multiple. Setting this argument to any value greater than 1,792 (the power-on default) disables it, so that packet transmission starts only when the entire packet has been moved to the TX FIFO.

#### Statistics Enable

## 1010 1 000 0000 0000

This command enables the collection of statistics by the PC Card. These statistics are maintained in Window 6 registers. At power-up, statistics collection is disabled and must be enabled with this command. Before any of the statistics in Window 6 are read, statistics collection must be temporarily disabled with the Statistics Disable command. Once the statistics have been read, statistics can be reenabled with this command.

#### Statistics Disable

## 1011 0 000 0000 0000

This command disables the collection of statistics by the PC Card. At power-up, statistics collection is disabled. The PC Card latches statistics update requests while the statistics are disabled. As long as statistics are only kept disabled long enough to read in the statistics, no statistics will be lost in the process. Refer to the "Statistics Registers" section later in this chapter for more information.

# Stop Coaxial Transceiver

1011 1 000 0000 0000

This command shuts off the DC-DC converter that drives the on-board coaxial transceiver. This command might be used for diagnostic or power-management reasons. The host must delay at least 800 µs after issuing this command before using the AUI interface. This can be accomplished by starting the timer and waiting until it pegs at its maximum value of FFh.

# Power-Management Commands (3C589B)

The following three power-management commands are new with 3C589B PC Cards. They may also be ignored by other future adapters. The capabilities bits can be examined to determine whether power-management capabilities are present in the PC Card.

Power Up\* 1101 1 000 0000 0000

This command puts the chip in power-up state, which is the default state at power-on/reset. In power-up state the chip is always fully powered up. This command is typically used after a Power Down Full or Power Auto command. Power Up does nothing if the PC Card is already powered-up. If used after a Power Down Full, the TX Reset and RX Reset commands should be issued before proceeding with operation. See also Power Auto and Power Down Full.

Power Down Full 1110 0 000 0000 0000

This command puts the chip in full power-down state. In this state the only legal access to the chip is the Power Up command. The full power-down state will use the least amount of power, but will not power up automatically. If the DC-DC converter is being used, issuing this command will stop it automatically (the equivalent of Stop Coaxial Transceiver). However, the DC-DC converter must be restarted manually after power-up (with Enable DC Converter, requiring an 800 µs delay). Otherwise, the state of the chip and the contents of its various registers are preserved.

Power Auto 1110 1 000 0000 0000

This command puts the chip in auto-power state. In this state the chip will automatically reduce power when idle (though it will use more power than in the Power Down Full state), and it will return to power-up state automatically when this changes (that is, when an incoming packet starts to be received). After issuing a Power Auto command, the host software should not rely on whether the PC Card is currently powered-up or powered-down. The next access to the PC Card should be a Power Up command. Normally the host software would issue a Power Up command at the entry to any thread dealing with the PC Card (for example, the start of the ISR, or the transmit routine), and issue a Power Auto command before returning. Since the DC-DC converter will not be powered-off with this command, the savings when 10BASE2 is used will be limited, though the command can still be used. The most significant savings will be realized with the 10BASE-T connector, where only a limited amount of logic will remain powered-up (enough to handle the link beat pulse trains, for example).

# **Status Register**

Function: Reports the PC Card state, including window number and the

reasons for the interrupt.

Location: All windows/Port OE

Type: Read only

Size: 16 bits (8-bit reads also allowed to either byte)

| 15 | 14    | 13 | 12 | 11 | 10 | 9 | 8 | 7  | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|----|-------|----|----|----|----|---|---|----|----|----|----|----|----|----|----|

| W  | indow | #  | ΙP | 0  | 0  | 0 | 0 | US | IR | RE | RC | TA | TC | AF | IL |

Figure 6-2 Status Register

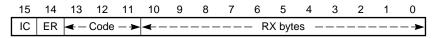

| Bit Description: | Bits 15-13 | Window Number (0-7)  |

|------------------|------------|----------------------|

|                  | Bit 12     | Command-in-Progress  |

|                  | Bit 11     | Reserved             |

|                  | Bit 10     | Reserved             |

|                  | Bit 9      | Reserved             |

|                  | Bit 8      | Reserved             |

|                  | Bit 7      | Update Statistics†   |

|                  | Bit 6      | Interrupt Requested† |

|                  | Bit 5      | RX Early†            |

|                  | Bit 4      | RX Complete†         |

|                  | Bit 3      | TX Available†        |

|                  | Bit 2      | TX Complete†         |

|                  | Bit 1      | Adapter Failure†     |

|                  | Bit 0      | Interrupt Latch      |

Those bits marked with a dagger (†) cause an interrupt when set, assuming they are not masked off in either the Interrupt mask or the Read Zero mask. These bits can be forced to zero with the Read Zero mask, disabled as a source of interrupts with the Interrupt mask, or acknowledged with the Acknowledge Interrupt command. All of these have identical layouts for these bits.

The low byte contains all of these interrupt causes and can be used directly as an index into a dispatch table if desired.

#### **PCMCIA (3C589B)**

A Host Reset (Global Reset with Host Reset enabled) clears the interrupt bits but does *not* clear the interrupt source. Therefore, if the Read Zero mask and the Interrupt mask are set, the interrupt may reappear. The driver must reset the interrupt in order to clear it.

#### Bit 0 Interrupt Latch

This bit is latched when the PC Card raises an interrupt to the host. The bit is cleared when it is acknowledged. In a shared interrupt environment (not ISA), this bit can be used to determine the source of the interrupt.

This bit does not cause an interrupt, it **is** the interrupt.

# Bit 1 Adapter Failure<sup>†</sup>

An error occurred that the PC Card was unable to recover from. Possible causes are:

- Transmit overrun (host writes more data than there is room for)

- Receive underrun (host reads data that is not yet available or attempts to read the RX FIFO beyond the pad bytes)

- Internally detected hardware errors as yet undefined

Possible causes are described in the FIFO Diagnostic Port register. The host must issue the appropriate Reset command to clear this condition and recover.

# Bit 2 TX Complete<sup>†</sup>

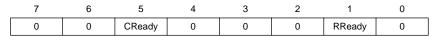

The PC Card has finished transmitting a packet and has updated the TX Status register with its transmit status (with the TX Complete bit set). To clear this bit, the host writes the TX Status register to pop the transmit status off the TX Status stack.