# 3C359 Network Interface Card Technical Reference

TokenLink Velocity® XL PCI token ring NIC with Parallel Tasking® II technology

http://www.3com.com/

Part Number: 89-0765-000 Published August 1998 3Com Corporation 5400 Bayfront Plaza Santa Clara, California 95052-8145 Copyright © 1998, 3Com Corporation. All rights reserved. No part of this documentation may be reproduced in any form or by any means or used to make any derivative work (such as translation, transformation, or adaptation) without written permission from 3Com Corporation.

3Com Corporation reserves the right to revise this documentation and to make changes in content from time to time without obligation on the part of 3Com Corporation to provide notification of such revision or change.

3Com Corporation provides this documentation without warranty, term, or condition of any kind, either implied or expressed, including, but not limited to, the implied warranties, terms or conditions of merchantability, satisfactory quality, and fitness for a particular purpose. 3Com may make improvements or changes in the product(s) and/or the program(s) described in this documentation at any time.

If there is any software on removable media described in this documentation, it is furnished under a license agreement included with the product as a separate document, in the hard copy documentation, or on the removable media in a directory file named LICENSE.TXT or !LICENSE.TXT. If you are unable to locate a copy, please contact 3Com and a copy will be provided to you.

#### UNITED STATES GOVERNMENT LEGEND

If you are a United States government agency, then this documentation and the software described herein are provided to you subject to the following:

All technical data and computer software are commercial in nature and developed solely at private expense. Software is delivered as "Commercial Computer Software" as defined in DFARS 252.227-7014 (June 1995) or as a "commercial item" as defined in FAR 2.101(a) and as such is provided with only such rights as are provided in 3Com's standard commercial license for the Software. Technical data is provided with limited rights only as provided in DFAR 252.227-7015 (Nov 1995) or FAR 52.227-14 (June 1987), whichever is applicable. You agree not to remove or deface any portion of any legend provided on any licensed program or documentation contained in, or delivered to you in conjunction with, this User Guide.

Unless otherwise indicated, 3Com registered trademarks are registered in the United States and may or may not be registered in other countries.

3Com, the 3Com logo, Parallel Tasking, and TokenLink Velocity are registered trademarks of 3Com Corporation.

Atmel is a trademark of Atmel Corporation. Dell is a registered trademark of Dell Computer Corporation. IBM is a registered trademark of International Business Machines Corporation. National Semiconductor is a registered trademark of National Semiconductor Corporation. Novell is a registered trademark of Novell, Inc.

All other company and product names may be trademarks of the respective companies with which they are associated.

# **CONTENTS**

# **1** INTRODUCTION

NIC Features 15 About This Technical Reference 15 Terms and Acronyms 16 Register Descriptions and Bit Maps 18

# **2 A**RCHITECTURE

Block Diagram 19 ASICs 20 Other NIC Devices 21 Flash ROM 21 EEPROM 21 64K SRAM 21 Host Registers 22 **Command Register** 22 Interrupt Status Register 22 Register Layout 23 MAC ASIC Registers 23

## **3** OPERATION

25 Software Interface Statistics 25 Flash ROM 25 Data Structure Lists 26 PCI Bus Master Operation 26 PCI Memory Commands 27 PCI Bus Request Control 27 Download 28 Upload 28 Power Management 28 Remote Wake-up Mode 28 Power States 29 Programming Remote Wake-up Events 30 Accessing and Managing Private Memory 31 Memory Usage 31 Without Flash ROM 31 With Flash ROM 32 Memory Access 32

CPAttention 34 MacAccessCmd 34 PrivateMemRead 35 PrivateMemWrite 35 MmioRead 35 MmioWrite 36 loRead 36 36 loWrite MacData 37 Pmbar 38 WRBR 38 WWCR 39 WWOR 39

## **4** CONFIGURATION

System Reset 41 Serial EEPROM 41 NIC Configuration 42 Autoinitialization 42 PCI Configuration 43 Driver Configuration 43 Without Flash ROM Installed 43 With Flash ROM Installed 44 PCI Configuration Registers 45 Vendorld 46 DeviceId 46 PciCommand 47 PciStatus 47 RevisionId 48 ClassCode 48 CacheLineSize 49 LatencyTimer 49 HeaderType 50 BaseAddress1 50 BaseAddress2 50 SubsystemVendorld 51 SubsystemId 52 BiosRomControl 52 CapPtr 52 InterruptLine 53 InterruptPin 53 MinGnt 53 MaxLat 54

Power Management Registers 54 Capld 54 NextPtr 54 PowerMgmtCap 55 PowerMgmtCtrl 56 Data 57

# 5 EEPROM

Data Format 59 3Com Node Address 60 Checksum 60 ConfigurationControl 60 ManufacturerId 60 Manufacturing Data 60 Date 60 Division 60 Product Code 60 OEM Node Address 60 PciParms1 61 PciParms2 61 Pmbar 61 DeviceId 61 ResourceRedirector 62 SubsystemId 62 SubsystemVendorld 62 SwitchSettings 62 MAC ASIC Registers 62 EeControl 62 EeData 63

### 6 DOWNLOAD AND TRANSMISSION

Packet Download Model 65 DPD Data Structure 66 DnNextPtr 66 FrameStartHeader 66 DnFragAddr 67 DnFragLen 67 Packet Download 68 Enabling Download 68 Simple Packet Download 68 Polling on DnNextPtr 68 Download Stalls and Idles 69 Download Completion 69

Multipacket Lists 70 Priority Queueing 70 Adding DPDs to the End of the Downlist 70 Inserting a DPD Near the Head of the Downlist 71 NIC Download Sequence 72 Byte Transmission Order 73 Packet Transmission 73 Packet Transmission Model 73 Optimized Packet Transmission 74 Reducing Interrupts 75 Limiting dnComplete Interrupts 75 Using CountDown Timer Instead of dnComplete 75 Underrun Recovery 75 Host Registers 76 DmaCtrl 76 DnBurstThresh 77 DnListPtr 78 DnPoll 79 DnPriRegThresh 79 TxStartThresh 80 **RECEPTION AND UPLOAD** Packet Upload Model 81 **UPD** Data Structure 81

### 7

UpNextPtr 82 FrameStatus 82 UpFragAddr 84 UpFragLen 84 Packet Reception 84 **Enabling Reception** 84 Packet Reception Model 84 Packet Upload 85 Upload Modes 85 Simple Packet Upload 86 Packet Upload Completion 86 Store-and-Forward Packet Reception 87 Store-and-Forward Procedure 87 Minimizing Register Accesses 88 Parallel Tasking Packet Reception 89 Combining Packet Reception Modes 89 Multicast Filtering 90 Multipacket Lists 91 Using Multiple UPDs 91 Early Interrupts 91 Packets with Errors 92 NIC Upload Sequence 93

Host Registers 93 DmaCtrl 93 UpBurstThresh 94 UpListPtr 94 UpPktStatus 95 UpPoll 97 MAC ASIC Registers 97 RxBufArea 97 RxEarlyThresh 98

# 8 INTERRUPTS AND INDICATIONS

Interrupt and Indication Enables 100 Host Registers 101 IndicationEnable 101 InterruptEnable 101 IntStatus 102 IntStatusAuto 104 MAC ASIC Registers 104 MISR 104 MacStatus 106

# 9 COMMAND REGISTER

Command 107 **Reset Commands** 108 GlobalReset \* 108 DnReset \* 109 UpReset \* 109 Transmit Commands 110 DnDisable \* 110 DnEnable 110 DnStall \* 110 DnUnstall 110 SetTxStartThresh 111 **Receive Commands** 111 RxDiscard \* 111 SelectHashFilterBit 111 UpStall \* 111 UpUnStall 112 Interrupt Commands 112 AckInterrupt 112 InterruptRequest \* 113 SetIndicationEnable 113 SetInterruptEnable 113 SetConfig 114

# **10** OTHER REGISTERS

Config 115 Countdown 116 FreeTimer 116 HashFilter 117 SwitchSettings 117 Timer 118

# **11** SOFTWARE OPERATION

MAC Packets 119 Multicast Reception 119 Communication with the Host 119 SRB Commands 120 Issuing SRB Commands 120 Change.Wakeup.Pattern 121 Close.NIC 122 Get.Statistics 122 Modify.Open.Parms 123 Open.NIC 123 Rules for TXI Protocol 127 Open Errors 127 Read.Log 129 Request.Interrupt 130 Restore.Open.Parms 131 Set.Funct.Address 131 Set.Group.Address 131 Set.Multicast.Mode 132 Set.Receive.Mode 132 Set.Sleep.Mode 133 ARB Commands 134 Received.Data 135 Ring.Status.Change 136 ASB Commands 137 Initializing the NIC 137 Detecting Ring Speed 138 Downloading the Microcode 138

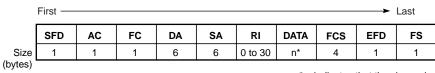

# A FRAME FORMAT

Bit Ordering 139 SFD and EFD Fields 140 AC Field 141 FC Field 141 DA Field 142 SA Field 142 RI Field 142 DATA Field 142 FCS Field 143 FS Field 143

# B ERRATA LIST AND SOFTWARE SOLUTIONS

Hash Calculation 145

INDEX OF REGISTERS

INDEX OF BITS

INDEX

# **FIGURES**

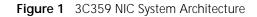

- **1** 3C359 NIC System Architecture 19

- 2 3C359 NIC Bus Request Structure 27

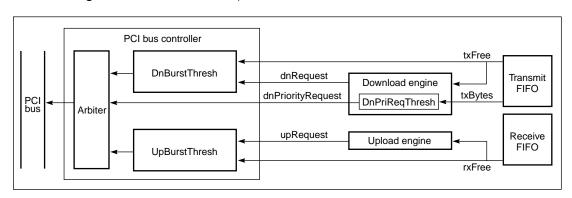

- **3** RAM-Based Configuration Memory Usage 31

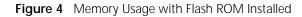

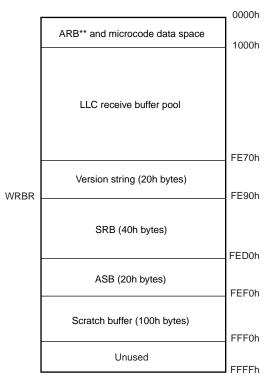

- 4 Memory Usage with Flash ROM Installed 32

- **5** Private Memory Partitioning 33

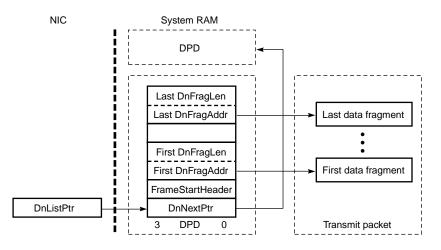

- 6 Downlist 65

- 7 DPD Format 66

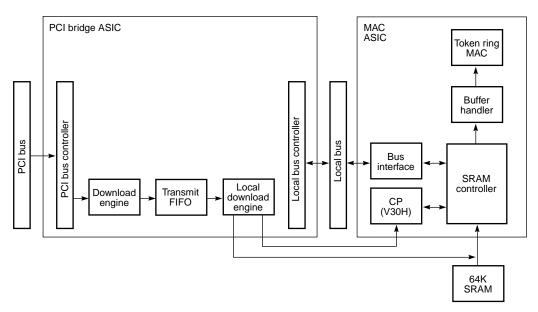

- 8 Packet Transmission Path 74

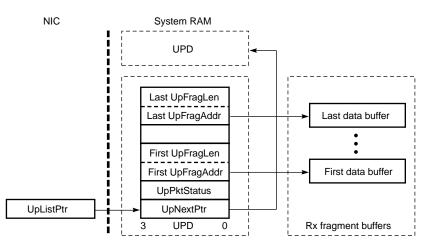

- 9 Uplist 81

- 10 UPD Format

- **11** Packet Reception Path 85

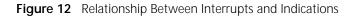

- 12 Relationship Between Interrupts and Indications 100

- **13** WILDFIRE.MAC File Format 138

82

- **14** Ring Transmission Order 139

- **15** SFD and EFD Field Formats and Timing 140

# **TABLES**

3Com 3C359 NIC Summary MAC ASIC PCI Bridge ASIC 3C359 Host Register Layout 3C359 MAC ASIC Register Layout Responses to Flash ROM Access PCI Memory Commands **Power States MMIO** Register Sizes and Locations I/O Register Sizes and Locations **EEPROM Data Locations** NIC Configuration After System Reset PCI Configuration Register Layout Data Register Values Based on dataSelect Bit Settings 3C359 NIC EEPROM Contents OEM Node Address Words in EEPROM OEM Node Address Words on the Network 61 Interrupt-specific Actions MISR Local Bus Memory Address Bit Definitions Command Summary Control Blocks SRB Command Summary Change.Wakeup.Pattern Command Parameters **Close.NIC Command Parameters** Get.Statistics Command Parameters MIB Statistics Counters Modify.Open.Parms Command Parameters **Open.NIC Command Parameters OPEN\_OPTIONS** Bit Descriptions SRB Response Format Open Error Code Values Responses to Open Error Codes Open Error Actions Read.Log Command Parameters Error Counters Available Through Read Log Request.Interrupt Command Parameters Restore.Open.Parms Command Parameters Set.Funct.Address Command Parameters Set.Group.Address Command Parameters

- **40** Set.Multicast.Mode Command Parameters 132

- 41 Set.Receive.Mode Command Parameters 132

- **42** Receive Options 133

- **43** Set.Sleep.Mode Command Parameters 133

- 44 ARB Commands 134

- 45 Received.Data Command Parameters 135

- 46 Received. Data ASB Response Parameters from the Host 136

- 47 Ring.Status.Change Command Parameters 136

- 48 ASB Responses 137

- **49** Token Ring Frame Fields 139

- **50** Token Priority Levels 141

# INTRODUCTION

This technical reference describes the basic architecture and defines the programming interface of the 3Com<sup>®</sup> TokenLink Velocity<sup>®</sup> XL PCI token ring network interface card (3C359 NIC). See Table 1.

### Table 1 3Com 3C359 NIC Summary

| Model | Bus | Ring Speed<br>(Mbps) | Cable                                                   | Connector        |

|-------|-----|----------------------|---------------------------------------------------------|------------------|

| 3C359 | PCI | 16 (default)<br>or 4 | Two-pair Category 3, 4, or 5 UTP;<br>or Type 1 or 6 STP | RJ-45 or<br>DB-9 |

| NIC Features                      | 3C359 NICs have these features:                                                                                                                                                                                                                                            |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                   | <ul> <li>Support for 4 Mbps and 16 Mbps IEEE 802.5 and IBM-compatible token ring<br/>LANs</li> </ul>                                                                                                                                                                       |

|                                   | <ul> <li>Support for IEEE P802.5r Draft 2 (dedicated token ring)</li> </ul>                                                                                                                                                                                                |

|                                   | <ul> <li>Fully independent transmit and receive data paths for full-duplex operation</li> </ul>                                                                                                                                                                            |

|                                   | <ul> <li>Support for both promiscuous and receive all group/multicast packet modes</li> </ul>                                                                                                                                                                              |

|                                   | <ul> <li>Built-in serial EEPROM controller for configuration and network address<br/>storage</li> </ul>                                                                                                                                                                    |

|                                   | <ul> <li>Support for Remote Wake-Up</li> </ul>                                                                                                                                                                                                                             |

|                                   | <ul> <li>Support for the maximum size packet (~18 KB)</li> </ul>                                                                                                                                                                                                           |

|                                   | <ul> <li>Parallel Tasking<sup>®</sup> II technology for superior performance</li> </ul>                                                                                                                                                                                    |

|                                   | <ul> <li>Plug and play configurability</li> </ul>                                                                                                                                                                                                                          |

|                                   | <ul> <li>Hash filtering of multicast packets</li> </ul>                                                                                                                                                                                                                    |

|                                   | <ul> <li>Optional flash ROM for BIOS code</li> </ul>                                                                                                                                                                                                                       |

|                                   | <ul> <li>Bus-mastering PCI for ultra-low CPU utilization</li> </ul>                                                                                                                                                                                                        |

|                                   | <ul> <li>Multipacket, multifragment DMA scatter and gather operations for uploads<br/>and downloads</li> </ul>                                                                                                                                                             |

|                                   | <ul> <li>64 KB SRAM for microcode and data buffers</li> </ul>                                                                                                                                                                                                              |

| About This Technical<br>Reference | This technical reference contains programming interface information that software engineers, independent software developers, and test engineers need to write device drivers, diagnostic programs, and production test software for 3C359 NICs This information includes: |

|                                   | <ul> <li>Theory of operation; for example, how transmission and reception occur.</li> </ul>                                                                                                                                                                                |

|                                   |                                                                                                                                                                                                                                                                            |

- Register set, including the size, type, address, and function of each register and the functions of the bits in the register.

- Software interface, which allows communication between the NIC and the host.

The information in this reference is language-independent. It applies regardless of the programming language you use to write the driver or other software program.

In this reference, addresses refer to physical addresses, not to logical or virtual addresses. Numeric values other than decimal values are presented in the following formats:

| Format  | Description                                          | Example                                |

|---------|------------------------------------------------------|----------------------------------------|

| #'rZZZZ | # is the number of bits.                             | 6'b100101 is a 6-bit binary notation.  |

|         | ' is a delimiter.                                    | 6'h25 is a 6-bit hexadecimal notation. |

|         | r is the radix (b for binary and h for hexadecimal). |                                        |

|         | ZZZZ is the value.                                   |                                        |

| ZZZr    | ZZZ is the value.                                    | 100101b is a binary notation.          |

|         | r is the radix (b for binary and h for hexadecimal). | 25h is a hexadecimal notation.         |

### Terms and Acronyms

**s** The following terms and acronyms are used in this reference:

| Attachment control area, the base address for MMIO registers.<br>Adapter request block, a control block in shared RAM that passes<br>receive information or commands from the CP to the host.<br>Adapter status block, a control block in shared RAM that passes<br>host responses to ARB commands to the CP. |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| receive information or commands from the CP to the host.<br>Adapter status block, a control block in shared RAM that passes                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                               |

| Basic input/output system. BIOS code is executed when the system boots.                                                                                                                                                                                                                                       |

| Read-only memory (ROM) that contains code that is executed when the system boots and performs remote program load over the network.                                                                                                                                                                           |

| Built-in self-test.                                                                                                                                                                                                                                                                                           |

| An 8-bit wide quantity of data.                                                                                                                                                                                                                                                                               |

| Communications processor (V30H).                                                                                                                                                                                                                                                                              |

| Cyclic redundancy check.                                                                                                                                                                                                                                                                                      |

| Destination address.                                                                                                                                                                                                                                                                                          |

| A 32-bit wide quantity of data (4 bytes).                                                                                                                                                                                                                                                                     |

| The process of transferring transmit data from system memory to the NIC.                                                                                                                                                                                                                                      |

| Download packet descriptor.                                                                                                                                                                                                                                                                                   |

| The type of PEROM used in 3C359 NICs to hold configuration information.                                                                                                                                                                                                                                       |

| Two or more adjacent bits; for example, [3:0] is a field of bits from bit 3 down to bit 0.                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                               |

| Term or Acronym | Meaning                                                                                                                                                                                                                              |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| flash ROM       | The type of PEROM used in 3C359 NICs to hold BIOS code.                                                                                                                                                                              |

| FSH             | Frame start header.                                                                                                                                                                                                                  |

| indication      | The reporting of any interesting event on the NIC. Any indication may be configured to cause an interrupt.                                                                                                                           |

| interrupt       | The actual assertion of the host machine's interrupt signal.                                                                                                                                                                         |

| LLC             | Logical link control. LLC packets typically originate and terminate<br>in the host. In this document, they are also called host packets.                                                                                             |

| MAC             | Media access control. MAC packets are used to implement the token ring access protocol and are usually local to the token ring subsystem. The driver and host software do not need to process them.                                  |

| microcode       | Code that runs on the NIC communications processor (CP). This code and the associated ASIC implement the token ring protocol Microcode is firmware held in ROM.                                                                      |

| MMIO            | Memory-mapped I/O. Memory locations embedded in silicon are<br>used to perform I/O control functions. MMIO is preferred over I/C<br>ports because memory operations on the PCI bus usually execute<br>faster than do I/O operations. |

| NIC             | Network interface card.                                                                                                                                                                                                              |

| NOS             | Network operating system.                                                                                                                                                                                                            |

| PEROM           | Programmable and erasable read-only memory.                                                                                                                                                                                          |

| PIO             | Programmed I/O.                                                                                                                                                                                                                      |

| PHY             | IEEE designation for physical layer.                                                                                                                                                                                                 |

| private memory  | The memory the NIC uses for data and firmware. It is implemented<br>in the 3C359 NIC with two 32 KB static RAMs (SRAMs) for a tota<br>of 64 KB. Private memory is also known as local memory.                                        |

| Remote Wake-Up  | The ability to turn on networked computers from a central location. The computers must have power management capabilities.                                                                                                           |

| RPL             | Remote program load. The BIOS code in the optional flash ROM performs RPL, which allows the computer to be booted from the network rather than from its own disk.                                                                    |

| SRAM            | Static RAM.                                                                                                                                                                                                                          |

| SRB             | System request block, a control block in shared RAM that passes transmit information or commands from the host to the CP.                                                                                                            |

| UPD             | Upload packet descriptor.                                                                                                                                                                                                            |

| upload          | The process of transferring received data from the NIC to system memory.                                                                                                                                                             |

| word            | A 16-bit wide quantity of data (2 bytes).                                                                                                                                                                                            |

Register DescriptionsThe register descriptions in this technical reference include register bit maps. For<br/>example:and Bit Mapsexample:

| Mo | Most significant word |    |    |    |    |    |    | _  | Least significant word |    |    |    |    |    |     |       |       |      |     |    |    |    |   |   |   |   |   |   |   |   |   |

|----|-----------------------|----|----|----|----|----|----|----|------------------------|----|----|----|----|----|-----|-------|-------|------|-----|----|----|----|---|---|---|---|---|---|---|---|---|

| Mc | Most significant byte |    |    |    |    |    |    |    |                        |    |    |    |    |    | Lea | st si | gnifi | cant | byt | е  |    | -> |   |   |   |   |   |   |   |   |   |

| 31 | 30                    | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22                     | 21 | 20 | 19 | 18 | 17 | 16  | 15    | 14    | 13   | 12  | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Х  | 0                     | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1                      | 1  | 0  | 0  | 0  | 0  | 0   | 0     | 0     | 0    | 0   |    |    | 0  | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

The first row of a bit map shows the bit numbers.

The second row of the bit map indicates the following information:

- Shaded areas indicate one of the following:

- Read-only bits. These bits read back the default values shown. If no value is shown, the read-back value varies.

- Unimplemented, reserved bits. These bits may be placeholders for possible use in a future revision of the NIC, or they may provide diagnostic information. Reserved bits are writable, but they do not control any function. They disregard data written to them and return zeros when they are read. To maintain compatibility with future versions of the NIC, drivers should write zeroes to reserved bits.

- Unshaded areas indicate active bits. The functions of these bits are described in the register descriptions. A value in an unshaded bit indicates that the driver must write that value to the bit.

- Vertical lines mark the boundaries of fields of bits (for example, [12:0]).

Default bit values are indicated as follows:

- 0 and 1 are known default states.

- x is a bit that is not initialized at reset; thus, its value varies.

# **A**RCHITECTURE

This chapter describes the 3C359 NIC architecture and shows the layout of the registers that the driver can control.

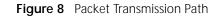

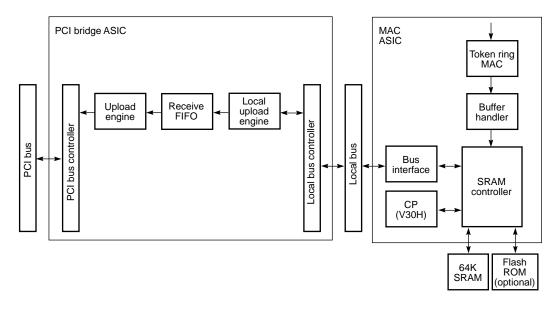

**Block Diagram** The block diagram for the 3C359 NIC is shown in Figure 1. The NIC devices are described in the following sections.

ASICs

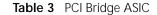

The NIC contains two ASICs:

- Media Access Control (MAC) ASIC (see Table 2)

- PCI bridge ASIC (see Table 3)

The PCI bridge ASIC connects the PCI bus and the local bus and uses the communications processor (CP) bus connection to write registers in the MAC ASIC directly, thereby controlling MAC ASIC transmissions. Performing this function in hardware rather than with microcode is largely responsible for the 3C359 NIC's very high throughput.

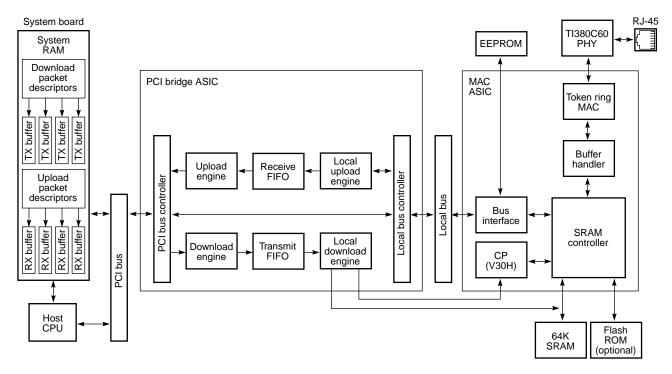

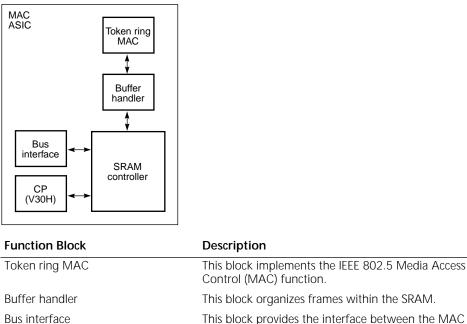

Table 2 MAC ASIC

CP (V30H)

SRAM controller

This block provides the interface between the MAC ASIC and the local bus. This block is the V30H communications processor. This block arbitrates among various requesters for

and implements the interface between the MAC ASIC and the SRAM and flash ROM.

| Host Registers            | The 3C359 NIC presents a set of registers to the host CPU. These host registers are mapped into 128 bytes of the host's I/O space, memory space, or both. A register that is mapped into memory space is called a memory-mapped I/O (MMIO) register.                                                                                                                                                                                                                                       |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                           | Because PCI memory transactions typically execute much faster than I/O operations, it is usually best to access the registers in memory space. However, the register set is also mapped into I/O space for the following reasons:                                                                                                                                                                                                                                                          |

|                           | <ul> <li>When memory resources are scarce, the only way to operate the NIC may be<br/>through I/O.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                              |

|                           | <ul> <li>If you need absolutely synchronous control of the NIC, then you must operate<br/>through I/O.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                          |

|                           | In general, host registers must be accessed as operands that are no wider than the bit width of the register. Specific register access limitations are described in the register definitions in this technical reference.                                                                                                                                                                                                                                                                  |

|                           | A host register's location is specified by its offset from a base address that is defined in the BaseAddress1 and BaseAddress2 PCI configuration registers. These registers are described in "PCI Configuration Registers" in Chapter 4.                                                                                                                                                                                                                                                   |

| Command Register          | Many of a driver's interactions with the NIC are performed using a command structure. Command codes written to the NIC perform some action. For example, the DnEnable command causes the download engine to download frames to the MAC ASIC.                                                                                                                                                                                                                                               |

|                           | Commands are written to the write-only Command register, which appears at offset 5E. For details on the commands, see Chapter 9.                                                                                                                                                                                                                                                                                                                                                           |

|                           | Commands and status are also exchanged between the host driver and the NIC firmware by means of the software interface. The software commands are described in Chapter 11.                                                                                                                                                                                                                                                                                                                 |

| Interrupt Status Register | The read-only IntStatus register shares the location offset 5E with the write-only<br>Command register. A driver uses IntStatus to determine the sources of interrupts<br>on the NIC. Some commands, such as DnStall, initiate a process that may take<br>some time to finish. The IntStatus register includes a bit that indicates when a<br>command issued to the Command register is in the process of being executed.<br>For details on the interrupt status registers, see Chapter 8. |

**Register Layout** Table 4 shows the 3C359 host register layout. Shaded areas in the table indicate reserved spaces. Do not program in these spaces.

Table 4

3C359 Host Register Layout

| Byte 3     | Byte 2   | Byte 1        | Byte 0         | Offset<br>(Hex) |

|------------|----------|---------------|----------------|-----------------|

| IntStatus/ | Command  | Indicatio     | 5C             |                 |

| Interrup   | otEnable | TxStart       | Thresh         | 58              |

| IntStat    | usAuto   |               |                | 54              |

|            |          |               |                | 50              |

|            |          |               |                | 4C              |

|            |          |               |                | 48              |

|            |          |               |                | 44              |

|            |          | DnBurstThresh | UpBurstThresh  | 40              |

|            |          | UpPoll        |                | 3C              |

|            | UpLi     | istPtr        |                | 38              |

| Count      | tdown    | Free          | 34             |                 |

|            | UpPkt    | Status        | 30             |                 |

|            |          | DnPoll        | DnPriReqThresh | 2C              |

|            |          | Config        | HashFilter     | 28              |

|            | DnLi     | istPtr        |                | 24              |

|            | Dma      | aCtrl         |                | 20              |

|            |          |               |                | 1C              |

|            | Timer    |               |                | 18              |

|            | MacAco   | cessCmd       |                | 14              |

|            |          | Mac           | Data           | 10              |

|            |          |               |                | 0C              |

|            |          |               |                | 08              |

|            |          |               |                | 04              |

|            |          |               |                | 00              |

### **MAC ASIC Registers**

MAC ASIC registers are not mapped directly into host I/O space. They must be accessed using the MacAccessCmd and MacData host registers, as described in Chapter 3.

The main method for host software to communicate with the NIC is through a group of private memory locations, called *control blocks*. See " Communication with the Host" in Chapter 11 for the means by which the locations of these blocks are communicated to the host. You can access control blocks through the MacAccessCmd and MacData host registers.

Table 5 shows the 3C359 MAC ASIC register layout. The memory-mapped I/O (MMIO) registers and the CpAttention I/O register are accessed with the MmioRead and MmioWrite commands in the MacAccessCmd register. The I/O registers, except CpAttention, are accessed with the PrivateMemRead and PrivateMemWrite commands in the MacAccessCmd register.

Shaded areas in the table indicate reserved spaces. Do not program in these spaces.

|                | Byte 1      | Byte 0 | Local<br>Address<br>(Hex) |  |  |  |  |

|----------------|-------------|--------|---------------------------|--|--|--|--|

| MMIO Registers | WF          | RBR    | CDE02                     |  |  |  |  |

|                | WW          | /OR    | CDE04                     |  |  |  |  |

|                | WV          | WWCR   |                           |  |  |  |  |

|                | Macs        | itatus | CDE08                     |  |  |  |  |

|                | MISR        |        | CDE0B                     |  |  |  |  |

|                | RxBu        | fArea  | CDE10                     |  |  |  |  |

|                | RxEarly     | Thresh | CDE12                     |  |  |  |  |

| I/O Registers  | CPAttention |        | 180D                      |  |  |  |  |

|                | Pm          | 1C80   |                           |  |  |  |  |

|                | Switchs     | 1C88   |                           |  |  |  |  |

|                | EeCo        | ontrol | 1C8A                      |  |  |  |  |

|                | EeD         | Data   | 1C8C                      |  |  |  |  |

Table 5

3C359 MAC ASIC Register Layout

**O**PERATION

|                    | This chapter summarizes NIC operational characteristics.                                                                                                                                                                                                                                                                                                                                                                                                 |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Software Interface | The software interface allows a driver to perform high-level operations such as inserting the NIC into the ring (opening the NIC) or requesting statistics from the MAC ASIC. The software interface is described in Chapter 11.                                                                                                                                                                                                                         |

| Statistics         | The NIC accumulates statistics to support network management software. The host retrieves these statistics with the Get.Statistics command, described in Chapter 11.                                                                                                                                                                                                                                                                                     |

| Flash ROM          | The 3C359 NIC has a socket to hold an optional flash ROM (also called a boot ROM). The flash ROM contains BIOS code that allows the host computer to be booted remotely over the network, rather than from its own disk. It also contains a copy of the NIC microcode, which is normally held in SRAM. Placing microcode in the flash ROM frees SRAM, allowing additional data buffer space, which is an important consideration in server applications. |

|                    | The flash ROM is a $64K \times 16$ -bit flash device that can be written electrically with a flash write utility. The flash ROM and utility are available together from 3Com (part number 3C359-TRIROM).                                                                                                                                                                                                                                                 |

|                    | The flash ROM size is 128 KB. The top 64 KB is reserved for microcode; the bottom 64 KB is reserved for BIOS code. The flash ROM is configured through the BiosRomControl PCI configuration register. This register causes the ROM to be mapped into the memory space of the host system, allowing the ROM contents to be scanned, copied to system RAM, and executed at initialization time.                                                            |

|                    | The 3C359 NIC uses the enBios bit in the Pmbar register to decide how to respond<br>to accesses to the flash ROM space defined in the BiosRomControl register. Also,<br>if either the addressDecodeEnable bit in the BiosRomControl register or the<br>memorySpace bit in the PciCommand register is cleared, then the PCI bridge ASIC<br>does not respond to accesses to flash ROM space.                                                               |

|                    | Table 6 shows the possible bit combinations for flash ROM access (cases A, B, C, and D) and the 3C359 NIC's responses in each case.                                                                                                                                                                                                                                                                                                                      |

### Table 6 Responses to Flash ROM Access

|      |                  | Bits                         |         |                                                                                                                                                                                                                                                                                                  |  |  |  |

|------|------------------|------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Case | memory<br>Space* | address<br>Decode<br>Enable† | enBios‡ | NIC Response                                                                                                                                                                                                                                                                                     |  |  |  |

| A    | 0                | Х                            | Х       | No response to memory access. The NIC does not activate the DEVSEL# signal on the PCI bus.                                                                                                                                                                                                       |  |  |  |

| В    | 1                | 0                            | Х       | Responds only to memory accesses to the area defined by the BaseAddress2 register (MMIO).                                                                                                                                                                                                        |  |  |  |

| С    | 1                | 1                            | 0       | Responds to memory accesses as in case B, but returns ones for memory accesses to the area defined by the BiosRomControl register.                                                                                                                                                               |  |  |  |

| D    | 1                | 1                            | 1       | Responds to MMIO accesses as in case B and returns ROM data for a memory access to the area defined by BiosRomControl. The MAC ASIC's Pmbar register must be set to F9C0h to read the ROM correctly. The EEPROM must be written with this private memory base address when the ROM is installed. |  |  |  |

\* The memorySpace bit is located in the PciCommand register.

† The addressDecodeEnable bit is located in the BiosRomControl register.

‡ The enBios bit is located in the MAC ASIC Pmbar register.

| Data Structure Lists        | To move data between the host and the NIC, drivers set up data structures in<br>system RAM to specify the buffers to be used for packet data movement. These<br>data structures, called descriptors, are linked together in system memory to form<br>lists.                                                                                                                                                                                                                                                                                     |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                             | All packet data is moved across the 3C359 PCI bus by bus master operations. The 3C359 NIC also uses bus master operations to read descriptor information out of system RAM and to write status back into the descriptors.                                                                                                                                                                                                                                                                                                                       |

|                             | Movement of a transmit packet to the NIC is called a download. The list of download packet descriptors (DPDs) is called the <i>downlist</i> . Similarly, a receive packet movement is called an upload, and the list of upload packet descriptors (UPDs) is the <i>uplist</i> .                                                                                                                                                                                                                                                                 |

|                             | The driver creates and maintains the uplist and downlist. It starts the download process by writing the address of the first download descriptor in the downlist to the DnListPtr register. Uploads are started by writing the first upload descriptor address to the UpListPtr register. The driver also accesses NIC registers for initialization, interrupt handling, statistics collection, and error handling. For details on data structure lists, see Chapter 6 and Chapter 7.                                                           |

| PCI Bus Master<br>Operation | This section describes aspects of bus master operation that can be controlled by software. For information about PCI configuration, see "PCI Configuration Registers" in Chapter 4.                                                                                                                                                                                                                                                                                                                                                             |

|                             | An on-board bus mastering mechanism passes data to and from the host.<br>Independent, full-fragment gathering (download) and scattering (upload) DMA<br>engines allow full-duplex operation and reduce the amount of buffer RAM<br>required on the NIC. The DMA engines reference DPDs and UPDs in host memory.<br>UPDs and DPDs indicate the size and location of the buffers for each packet.<br>When the host transmits a packet, the driver programs the location of the DPD<br>into the NIC to trigger the DMA engine to begin a download. |

Likewise, packets move from the NIC to host memory according to a UPD. A UPD can be specified before the NIC receives the packet (in which case, the packet moves immediately off the wire and into host buffers), or can be specified after a packet has been received. The former case results in higher performance.

The UPD can specify buffer sizes ranging from just large enough to hold some amount of look-ahead data to large enough to hold a maximum size packet. The software environment determines the most appropriate arrangement to use.

PCI Memory Commands The 3C359 NIC supports all PCI memory commands. (See Table 7.)

| Command | Description             |

|---------|-------------------------|

| MW      | Memory write            |

| MWI     | Memory write invalidate |

| MR      | Memory read             |

| MRL     | Memory read line        |

| MRM     | Memory read multiple    |

Table 7

PCI Memory Commands

To read packet data transmitted to it, the NIC uses the MR, MRL, or MRM command. To write packet data it receives, the NIC uses either the MW or MWI command. For maximum bus efficiency, the NIC decides which command to use on a burst-by-burst basis. The choice depends on the remaining number of bytes in the fragment, the amount of free space in the transmit or receive FIFO, and certain system parameters, such as cache line size.

These configuration bits control the use of PCI memory commands:

- The MWIEnable bit in the PciCommand configuration register enables or disables the NIC's use of MWI.

- The defeatMWI bit in the DmaCtrl register can disable the NIC's use of MWI, independently of the MWIEnable bit. By default, MWI is enabled.

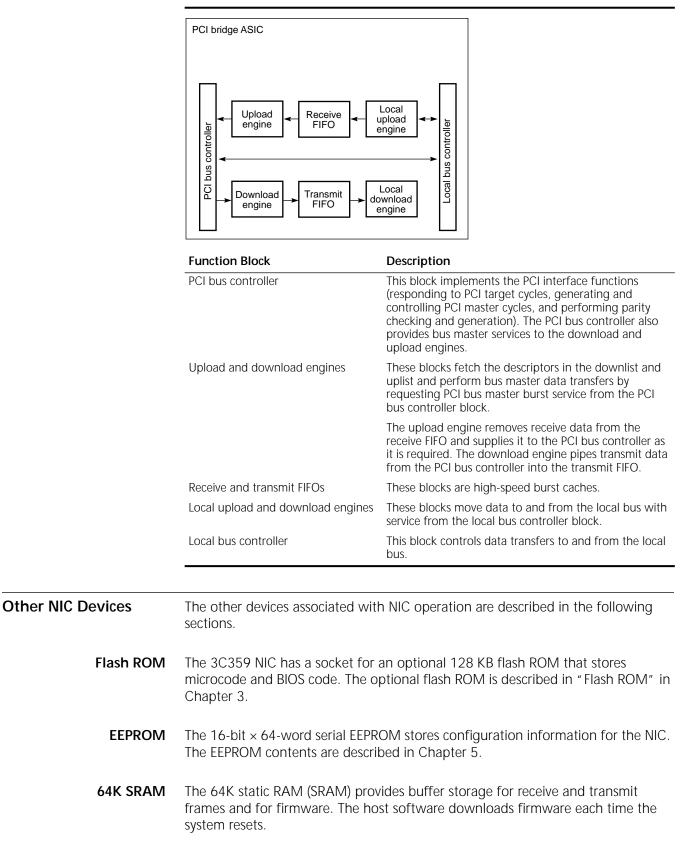

### PCI Bus Request Control

A set of registers controls PCI burst behavior. These registers allow trade-offs to be made between PCI bus efficiency and underrun and overrun frequency. Figure 2 illustrates the bus request structure.

#### Figure 2 3C359 NIC Bus Request Structure

Arbitration logic (the arbiter) within the PCI bus controller block accepts bus requests from the download and upload engines.

### Download

The download engine monitors the amount of free space in the transmit FIFO. When there are at least 16 bytes of free space and a fragment available for download, the download engine issues the dnRequest signal to make a standard bus request. The DnBurstThresh logic qualifies dnRequest. When the amount of free space in the FIFO is greater than the value in the DnBurstThresh register, a download request is passed on to the arbiter. The purpose of DnBurstThresh is to delay the bus request until there is enough free space in the FIFO for a long, efficient burst.

The download engine also has a way to make an emergency bus request. When the number of used bytes in the FIFO drops below the value in the DnPriReqThresh register, indicating that the FIFO is approaching an underrun condition, the dnPriorityRequest signal makes a priority request. This request is not subject to the DnBurstThresh constraint; when the FIFO is close to underrun, burst efficiency is sacrificed in favor of requesting the bus as quickly as possible.

### Upload

|                     | opicad                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | The upload mechanism is similar to download. The upload engine monitors the number of bytes in the receive FIFO. When there are at least 16 bytes in the FIFO and a buffer is available for upload, the upload engine issues the upRequest signal to make a standard bus request. The UpBurstThresh logic qualifies the upRequest signal; when the number of bytes in the FIFO is greater than the value in the UpBurstThresh register, an upload request is passed on to the arbiter. |

|                     | Upload does not have a priority request mechanism because the upload FIFO buffer is larger than 30 KB, which is large enough to tolerate large bus latencies. Download, with only 512 bytes of buffering, requires the priority mechanism.                                                                                                                                                                                                                                             |

| Power Management    | The NIC supports power management directed by the operating system, in accordance with the <i>Advanced Configuration and Power Interface (ACPI)</i> specification. A properly equipped PC can put itself into a low-power state while the NIC remains active on the ring. A defined network event can then be used to wake the computer remotely. This mode is known as <i>remote wake-up</i> mode.                                                                                    |

|                     | 3C359 NICs include power management registers in the PCI configuration space, as defined by the <i>PCI Bus Power Management Interface Specification, Revision 1.0.</i> The PowerMgmtCap register supplies the system with information about the NIC's power management support and capabilities. The PowerMgmtCtrl register allows system or driver software to read the NIC's power management status and set the NIC's power state.                                                  |

|                     | For a complete discussion of power management, refer to the <i>PCI Bus Power</i><br><i>Management Interface</i> specification on the World Wide Web at www.pcisig.com.                                                                                                                                                                                                                                                                                                                 |

| Remote Wake-up Mode | When the NIC prepares to enter the remote wake-up mode, the driver specifies one or more types of wake-up packets. While in this mode, the NIC does not process DPDs, nor does it upload to the host any logical link control (LLC) frames                                                                                                                                                                                                                                             |

that it receives. It simply monitors the ring for a wake-up packet. Firmware parses all received frames, looking for one that matches the contents of one of the wake-up packet types. Packets that do not match are discarded.

When the NIC recognizes a remote wake-up packet, it activates a signal on the PCI bus connector that causes the PC to start up and assume an operational state. Firmware takes the following actions when it receives a remote wake-up packet:

- 1 Puts an appropriate response into the adapter request block (ARB), indicating that it has received a remote wake-up packet.

- 2 Saves the remote wake-up packet for possible forwarding to the host. The driver needs to reconfigure the NIC for normal operation before the packet can be forwarded.

Table 8 Power States

| State                         | powerState Value | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D0 <sub>uninitialized</sub>   | 0                | D0 <sub>uninitialized</sub> is the result of a hardware reset, or of a transition from D3 <sub>hot</sub> to D0. The PCI configuration registers are uninitialized, and the NIC responds to PCI configuration cycles only.                                                                                                                                                                                                                 |

| D0 <sub>active</sub>          | 0                | DO <sub>active</sub> is the normal operational power state for the NIC. In DO <sub>active</sub> , the PCI configuration registers have been initialized by the system, including the ioSpace, memorySpace, and busMaster bits in the PciCommand register. Therefore, the NIC is able to respond to PCI I/O and memory and configuration cycles and can operate as a PCI master.                                                           |

|                               |                  | The NIC cannot signal wake-up (assert the PME# signal on the PCI bus) from the D0 state.                                                                                                                                                                                                                                                                                                                                                  |

| D1                            | 1                | D1 is a "light-sleep" state, which allows transition back to D0 with no delay. In D1, the PCI clock is running. The NIC responds to PCI configuration accesses, allowing the system to change the power state, but it does not respond to PCI I/O or memory accesses. The NIC's function in the D1 state is to recognize wake-up events and link state events and pass them on to the system by asserting the PME# signal on the PCI bus. |

| D2                            | 2                | D2 is a partial power-down state that allows a faster transition back to D0 than is possible from the D3 state. D2 is functionally identical to D1, except that in D2, the PCI clock may be stopped, reducing power consumption even further.                                                                                                                                                                                             |

| D3 <sub>hot</sub>             | 3                | $D3_{hot}$ is the full power-down state for the NIC. In $D3_{hot}$ , the NIC shuts down and places itself into the lowest power condition.                                                                                                                                                                                                                                                                                                |

|                               |                  | In D3 <sub>hot</sub> , the NIC responds to PCI configuration accesses, to allow the system to change the power state back to $D0_{uninitialized}$ , but it does not respond to PCI I/O or memory accesses.                                                                                                                                                                                                                                |

| $\mathrm{D3}_{\mathrm{cold}}$ | N/A              | This is the power-off state for the NIC. The NIC has no function in this state. Restoring power causes a hardware reset, which puts the NIC into the DO <sub>uninitialized</sub> state.                                                                                                                                                                                                                                                   |

The system puts the NIC into either the D1 or D2 state when it is going to power down but wants the NIC to monitor for wake-up packets. From the NIC's perspective, D1 and D2 are identical, but D2 consumes less power because the PCI clock may be stopped.

Because the clock is stopped in D2, the dynamic power consumption of the PCI bridge ASIC drops dramatically, thus reducing the overall power consumption of the NIC. Only as much logic as is necessary to allow the NIC to monitor for wake-up packets and to assert the PME# signal is left powered. Because the NIC is still inserted in the ring and participating in ring polling, power consumption of the rest of the NIC is unaffected by whether it is in the D0, D1, or D2 state.

**Power States** Table 8 defines the supported power states. The current power state is determined by the powerState field in the PowerMgmtCtrl register.

|                                      | Exiting the D1 or D2 states involves changing the powerState bit in the PowerMgmtCtrl register.                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      | In D3 <sub>hot</sub> the PCI bridge ASIC turns the 32-MHz clock off. The RESETOUT signal is applied to the MAC control ASIC and the PWRDN signal is applied to the TI380C60 ring interface device (PHY). Power consumption in this state is less than a few tens of milliwatts, most of which is consumed in the 5-V-tolerant I/O buffers between the PCI bridge ASIC and the MAC control ASIC, and in the 3.3-V regulator. In the D3 <sub>hot</sub> state, it is not possible to monitor for wake-up packets. |

|                                      | Removing power puts the NIC into the $D3_{cold}$ state, and all NIC context is lost. $D3_{cold}$ can only be exited by restoring the power and clock and then asserting the RST# signal.                                                                                                                                                                                                                                                                                                                       |

|                                      | In accordance with the PCI specification, the NIC ignores all bus transactions except configuration accesses when it is in the D1, D2, or D3 <sub>hot</sub> states.                                                                                                                                                                                                                                                                                                                                            |

| Programming Remote<br>Wake-up Events | The following steps put the 3C395 NIC into the remote wake-up mode (D1 or D2):                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1                                    | The operating system calls the driver and tells it to go into remote wake-up mode.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2                                    | The driver takes the following actions:                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                      | <b>a</b> Waits until all queued download packets have been transmitted, or stalls the download and purges all remaining packets from memory.                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | <b>b</b> Uses the Set.Sleep.Mode command to tell the firmware that it is to enter the remote wake-up mode. The firmware reconfigures the MAC receiver to place all LLC frames that pass the address filter into private MAC buffers. The driver specifies to the firmware the contents of all remote wake-up packet types to be monitored.                                                                                                                                                                     |

|                                      | c Processes or discards all receive frames still in the queue. The host also processes all pending interrupts.                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                      | <b>d</b> Informs the operating system that the NIC is ready to be put to sleep.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3                                    | The operating system puts the NIC into either the D1 or D2 state and uses the PowerMgmtCtrl register to enable the PME# pin.                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | The following steps put the 3C395 NIC into the full power-down state (D3 $_{\rm hot}$ ):                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                                    | The driver closes the NIC (remove it from the ring) and informs the operating system that the NIC is closed.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 2                                    | The operating system puts the NIC in the D3 <sub>hot</sub> state.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3                                    | The PCI bridge ASIC initiates a controlled power-down sequence:                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      | <b>a</b> Sets the PCI bridge ASIC's pins to predetermined power-down states.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                      | <b>b</b> Applies the RESETOUT signal to the MAC control ASIC.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                      | c Applies the PWRDN signal to the PHY.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |