# MU9C8338/8358L Ethernet Filter Interface Errata Sheet

# AFFECTED DEVICES

MU9C8338 Revision C and MU9C8358L Revision A Ethernet Filter Interfaces.

# **PROBLEM 1**

/FI input expects a 0 to 1 transition in order to cause the Full Flag interrupt, while the LANCAM /FF output goes from 1 to 0 when a CAM Full condition occurs.

## Scope

This problem affects applications where the Full Flag Interrupt is enabled in the System Target register (STARG) with bits [1:0] = 10.

#### Fix

No silicon changes are currently planned to correct this problem but future changes are possible.

## Workaround

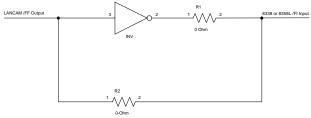

MUSIC recommends that all designs requiring the Full Flag interrupt have an inverter placed between the /FF output and /FI input. If the inverter is obtained from logic other than a programmable logic device, a 0-Ohm bypass resistor is recommended so the PCB will be compatible with any later revisions. In the example shown in Figure 1, R1 is installed and R2 is omitted. If the inverter is not required and can not be removed from the PCB, resistor R1 can be omitted and R2 installed.

# Figure 1: LANCAM /FF Signal Inverter Workaround Documentation

The installation of the inverter, described in the workaround section of this errata, requires a minor clarification to the Data Sheet. Table 2 on page 10 of the 8353L Data Sheet and Table 2 on page 5 of the 8338 Data Sheet should be changed as shown in bold in Table 1 and Table 2 while using the workaround.

## Table 1: Previous

## Table 2: Revision After Workaround

| STARG | SSTAT. Please note that /INTR will<br>only return HIGH when the<br>LANCAM has become not full.<br>Therefore, after the SSTAT register<br>read has confirmed the status of<br>the interrupt condition, an entry<br>should be removed from the<br>LANCAM by using the PURGE | The /FF output from the LANCAM(s) has indicated that the LANCAM is full. When reading the SSTAT register, a full condition is indicated by bit <b>0 = 1 due to the inverter.</b> |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | sequence.                                                                                                                                                                                                                                                                 |                                                                                                                                                                                  |

# PROBLEM 2

After setting the System Target register (STARG) appropriately, the method for resetting the Full Flag interrupt does not function as it is described in the data sheet. Once a Full Flag interrupt has occurred, it should reset once the System Status register (SSTAT) is read and the LANCAM has been made not full by removing an entry. A problem exists that causes the /INTR pin to remain at logic 0 although the interrupt condition has been removed and the appropriate registers have been read.

#### Scope

This problem affects applications where the Full Flag Interrupt is enabled in the STARG register with bits [1:0] = 10.

#### Fix

No silicon changes are currently planned to correct this problem but future changes are possible.

#### Workaround

The Full Flag Interrupt condition can be reset once it has occurred by reading an additional register. Although the additional register is not related to the condition, it will cause the /INTR pin to return to its initial state once it is read. The new procedure to reset the interrupt condition is as follows:

- 1. Read System Status register (SSTAT) to determine Full Flag condition.

- 2. Remove at least one LANCAM entry using purge routine.

- 3. Repeat steps 1 and 2 until reading SSTAT reveals the LANCAM is no longer full.

- 4. Read the Result Data register (RDAT) which causes the /INTR pin to return to normal state. The contents of the register should be ignored as the action of reading the register is enough to reset the condition.

## **PROBLEM 3**

After setting the Port Target register (PTARG) appropriately, the method for resetting the interrupt caused by a DA processing function is not as it is described in the data sheet. This problem exists for the single port in the MU9C8338 and for all four ports in the MU9C8358L. Once an interrupt has occurred, it should reset only when all possible Result data has been read from the Result Data register (RDAT). A problem exists that causes the /INTR pin to return to logic 1, regardless if there is Result data still available to be read.

#### Scope

This problem affects applications where the DA processing Interrupt is enabled in the Port Target register (PTARG) with bits [5:4] = 10. The problem affects the PTARG register in the MU9C8338 and PTARG\_A, PTARG\_B, PTARG\_C, and PTARG\_D in the MU9C8358L.

#### Fix

No silicon changes are currently planned to correct this problem but future changes are possible.

## Workaround

The workaround for this problem is quite straightforward. The new procedure to reset the interrupt condition is as follows:

- 1. Read the Result Status register (RSTAT) to determine if there is a result in the RDAT register.

- 2. Read the RDAT register to retrieve the data. This will reset the Interrupt condition and therefore cause the /INTR pin to return to logic 1.

- 3. Read the RSTAT register to confirm if there are further results to be read from the RDAT register. If so, repeat steps 2 and 3 until RSTAT confirms there is no remaining Result data. If not, there is no further action required.

MUSIC Semiconductors, the MUSIC logo, and the phrase "MUSIC Semiconductors" are Registered trademarks of MUSIC Semiconductors. MUSIC is a trademark of MUSIC Semiconductors.

## **PROBLEM 4**

After setting the Port Configure register (PCFG) to enable the 10 Base - x CRC check facility, the facility does not function properly. A problem exists that causes the internal logic to miscalculate the CRC when the function is enabled. This means that the SA processing function is not performed if the CRC check is enabled.

## Scope

This problem affects applications where the 10 Base - x CRC check facility is enabled in the PCFG register with bit 1 = 1.

## Fix

No silicon changes are currently planned to correct this problem but future changes are possible.

#### Workaround

It is recommended that the 10 Base - x CRC check facility is disabled in the PCFG register with bit 1 = 0.

MUSIC Semiconductors' agent or distributor:

MUSIC Semiconductors reserves the right to make changes to its products and specifications at any time in order to improve on performance, manufacturability or reliability. Information furnished by MUSIC is believed to be accurate, but no responsibility is assumed by MUSIC Semiconductors for the use of said information, nor for any infringements of patents or of other third-party rights which may result from said use. No license is granted by implication or otherwise under any patent or patent rights of any MUSIC company.

© Copyright 2000, MUSIC Semiconductors

http://www.musicsemi.com

email: info@musicsemi.com

Worldwide Headquarters MUSIC Semiconductors 1521 California Circle Milpitas, CA 95035 USA Tel: 408 869-4600 Fax: 408 942-0837 USA Only: 800 933-1550 Tech Support 888 226-6874 Product Info

## Asian Headquarters

MUSIC Semiconductors Special Export Processing Zone Carmelray Industrial Park Canlubang, Calamba, Laguna Philippines Tel: +63 49 549-1480 Fax: +63 49 549-1024 Sales Tel/Fax: +632 723-6215 MUSIC Semiconductors P. O. Box 184 6470 ED Eygelshoven The Netherlands Tel: +31 43 455-2675 Fax: +31 43 455-1573

**European Headquarters**